28 www.national.com

DP83847

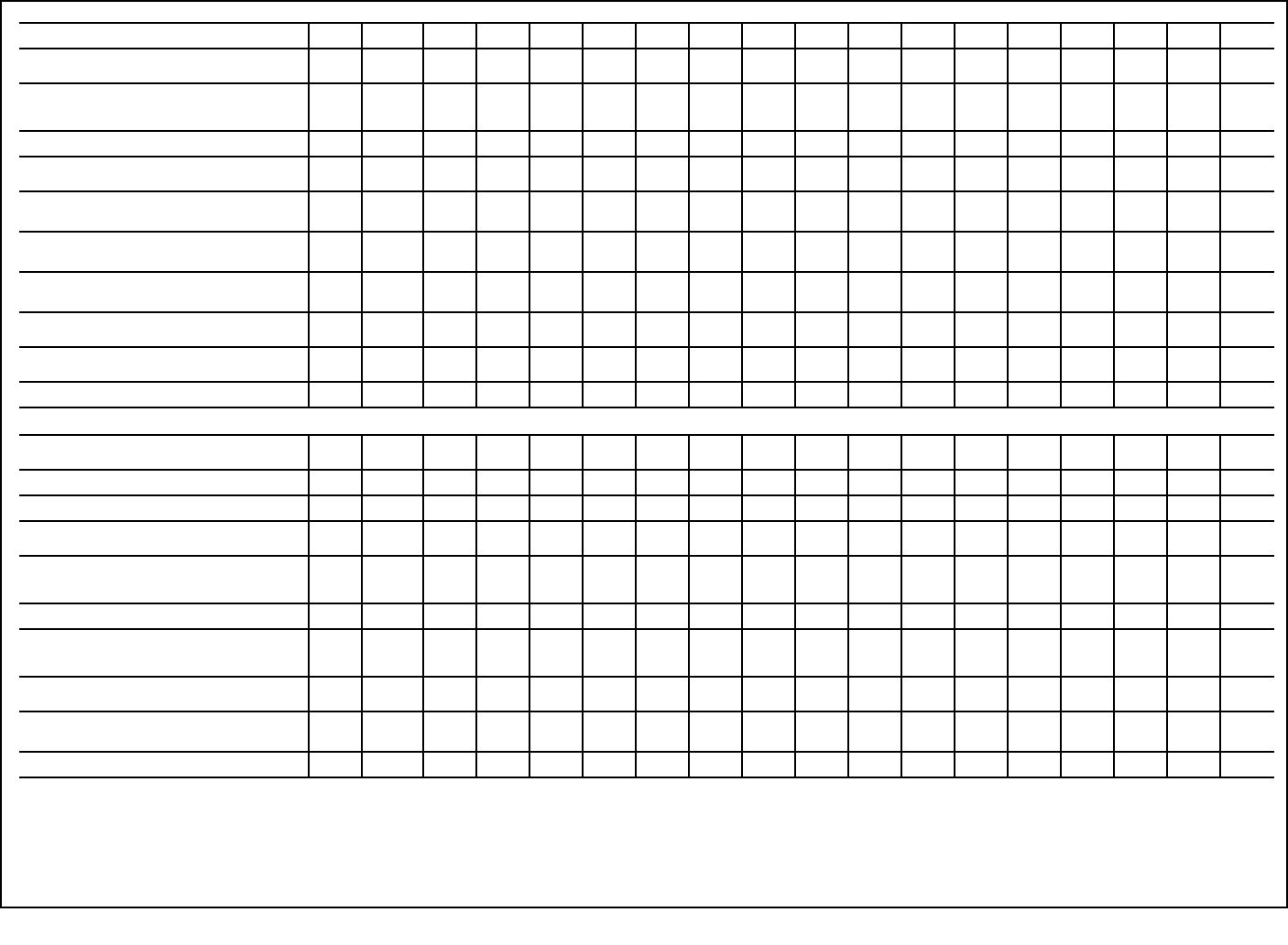

Register Name Addr Tag Bit 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Basic Mode Control Register

00h BMCR Reset Loopback Speed Se-

lect

Auto-Neg

Enable

Power

down

Isolate Restart

Auto-Neg

Duplex Collision

Test

Reserved Reserved Reserved Reserved Reserved Reserved Reserved

Basic Mode Status Register

01h BMSR 100Base-

T4

100Base-

TX FDX

100Base-

TX HDX

10Base-

T

FDX

10Base-

T

HDX

Reserved Reserved Reserved Reserved MF Pre-

amble

Suppress

Auto-Neg

Complete

Remote

Fault

Auto-Neg

Ability

Link

Status

Jabber

Detect

Extended

Capability

PHY Identifier Register 1

02h PHYIDR1 OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB OUI MSB

PHY Identifier Register 2

03h PHYIDR2 OUI LSB OUI LSB OUI LSB OUI LSB OUI LSB OUI LSB VNDR_

MDL

VNDR_

MDL

VNDR_

MDL

VNDR_

MDL

VNDR_

MDL

VNDR_

MDL

MDL_

REV

MDL_

REV

MDL_

REV

MDL_

REV

Auto-Negotiation Advertisement Register

04h ANAR Next Page

Ind

Reserved Remote

Fault

Reserved Reserved PAUSE T4 TX_FD TX 10_FD 10 Protocol

Selection

Protocol

Selection

Protocol

Selection

Protocol

Selection

Protocol

Selection

Auto-Negotiation Link Partner Ability Regis-

ter (Base Page)

05h ANLPAR Next Page

Ind

ACK Remote

Fault

Reserved Reserved Reserved T4 TX_FD TX 10_FD 10 Protocol

Selection

Protocol

Selection

Protocol

Selection

Protocol

Selection

Protocol

Selection

Auto-Negotiation Link Partner Ability Regis-

ter Next Page

05h ANLPARNP Next Page

Ind

ACK Message

Page

ACK2 Toggle Code Code Code Code Code Code Code Code Code Code Code

Auto-Negotiation Expansion Register

06h ANER Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved PDF LP_NP_

ABLE

NP_

ABLE

PAGE_

RX

LP_AN_

ABLE

Auto-Negotiation Next Page TX Register

07h ANNPTR Next Page

Ind

Reserved Message

Page

ACK2 TOG_TX CODE CODE CODE CODE CODE CODE CODE CODE CODE CODE CODE

RESERVED

08-0fh Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

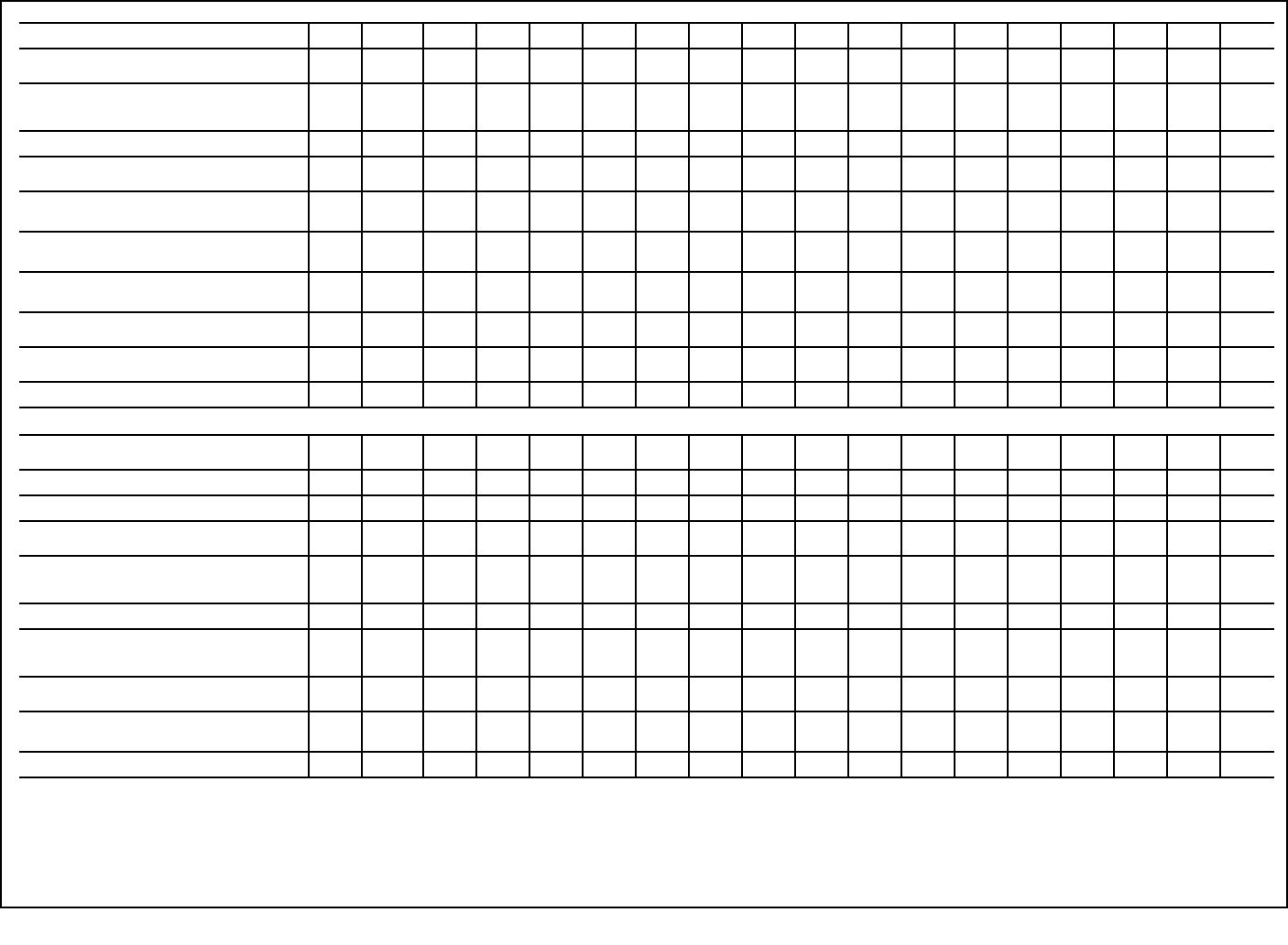

EXTENDED REGISTERS

PHY Status Register

10h PHYSTS Reserved Reserved Rx Err

Latch

Polarity

Status

False Car-

rier Sense

Signal De-

tect

Descram

Lock

Page

Receive

Reserved Remote

Fault

Jabber

Detect

Auto-Neg

Complete

Loopback

Status

Duplex

Status

Speed

Status

Link

Status

RESERVED

11-13h Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

False Carrier Sense Counter Register

14h FCSCR Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved FCSCNT FCSCNT FCSCNT FCSCNT FCSCNT FCSCNT FCSCNT FCSCNT

Receive Error Counter Register

15h RECR Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved RXER-

CNT

RXER-

CNT

RXER-

CNT

RXER-

CNT

RXER-

CNT

RXER-

CNT

RXER-

CNT

RXER-

CNT

PCS Sub-Layer Configuration and Status

Register

16h PCSR Reserved Reserved Reserved BYP_

4B5B

FREE_

CLK

TQ_EN SD_FOR

CE_PMA

SD_

OPTION

Unused Reserved FORCE_

100_OK

Reserved Reserved NRZI_

BYPASS

SCRAM_

BYPASS

DE

SCRAM_

BYPASS

RESERVED

17-18h Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved

PHY Control Register

19h PHYCTRL Unused Unused Unused Unused PSR_15 BIST_

STATUS

BIST_

START

BP_

STRETC

H

PAUSE_

STS

LED_

CNFG

LED_

CNFG

PHY

ADDR

PHY

ADDR

PHY

ADDR

PHY

ADDR

PHY

ADDR

10Base-T Status/Control Register

1Ah 10BTSCR Unused Unused Unused Unused Unused Unused Unused Loopback

_10_dis

LP_DIS Force_

Link_10

Reserved Polarity Reserved Reserved Hrtbeat

_Dis

Jabber

_Dis

CD Test Control Register

1Bh CDCTRL CD_Enabl

e

DCD_

Comp

FIL_TTL rise-

Time[1]

rise-

Time[0]

fallTime[1] fallTime[0] cdTestEn Reserved Reserved Reserved cdPattEn_

10

cdPatEn_

100

10meg_

patt_gap

cdPatt-

Sel[1]

cdPatt-

Sel[0]

RESERVED

1C-1Fh Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved Reserved