46 www.national.com

DP83847

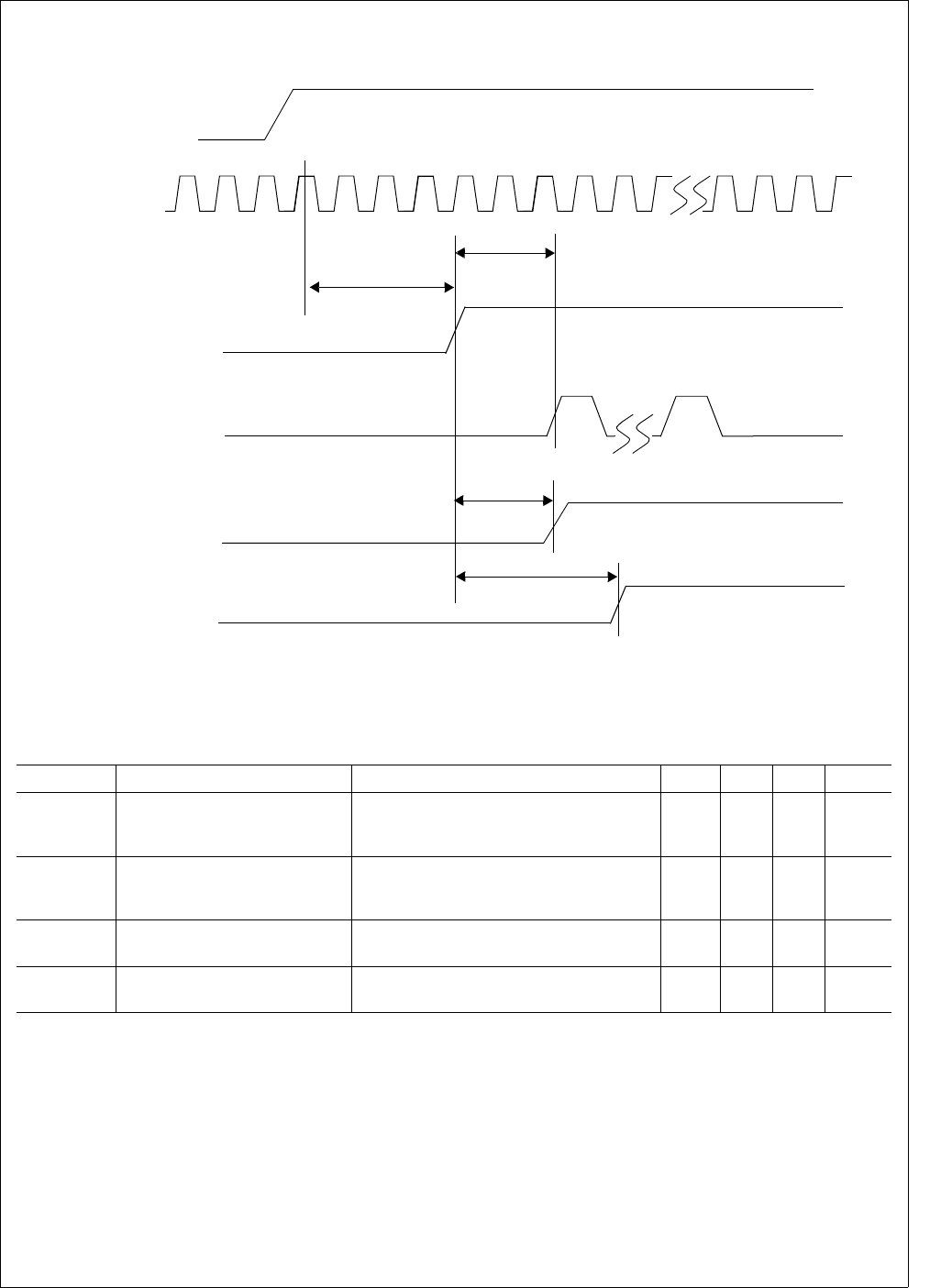

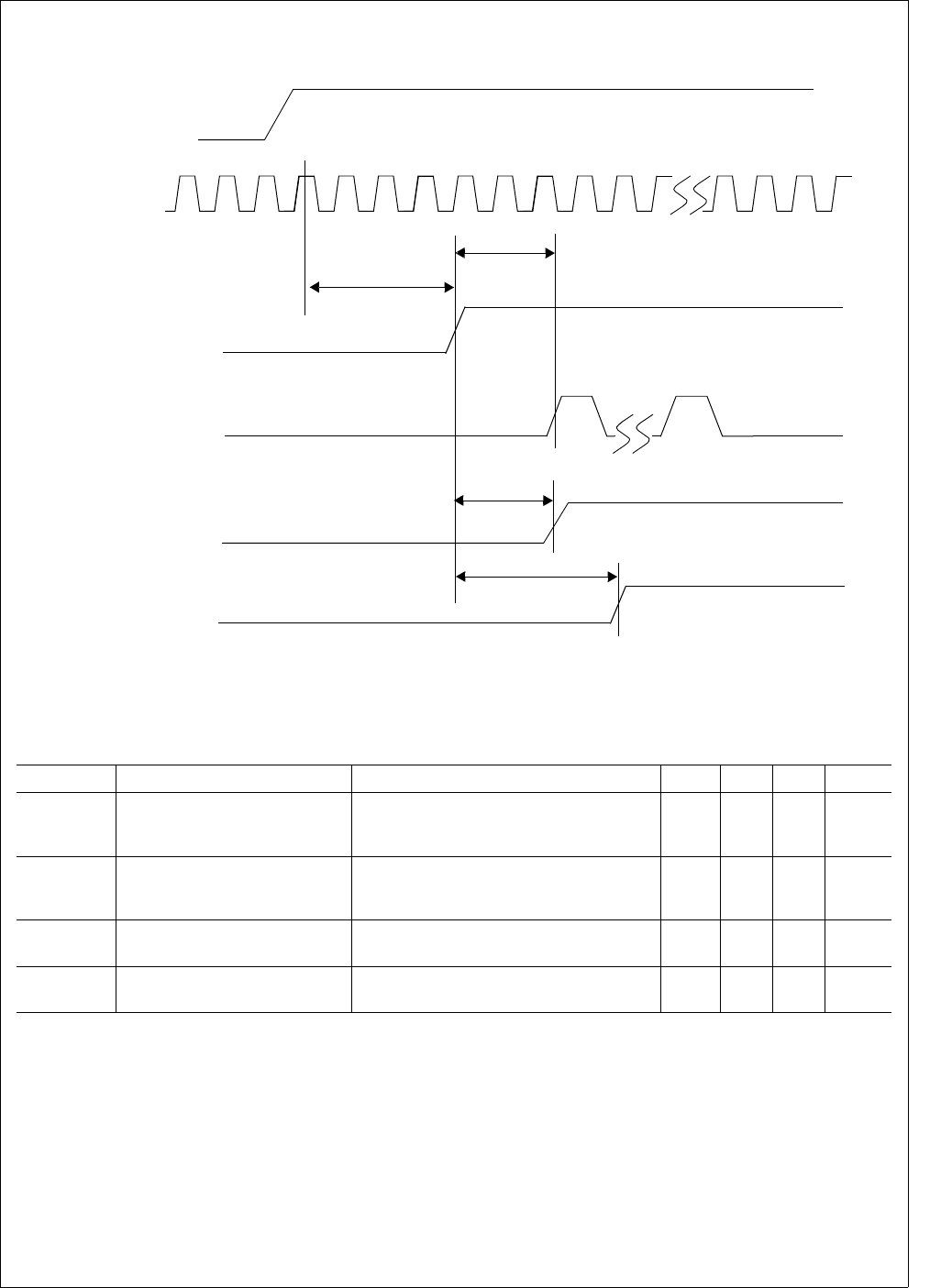

6.1 Reset Timing

Note1: Software Reset should be initiated no sooner then 500 µs after power-up or the deassertion of hardware reset.

Note2: It is important to choose pull-up and/or pull-down resistors for each of the hardware configuration pins that provide

fast RC time constants in order to latch-in the proper value prior to the pin transitioning to an output driver.

Parameter Description Notes Min Typ Max Units

T1.0.1 Post RESET Stabilization time

prior to MDC preamble for reg-

ister accesses

MDIO is pulled high for 32-bit serial man-

agement initialization.

3 µs

T1.0.2 Hardware Configuration Latch-

in Time from the Deassertion of

RESET (either soft or hard)

Hardware Configuration Pins are de-

scribed in the Pin Description section.

3 µs

T1.0.3 Hardware Configuration pins

transition to output drivers

3.5 µs

T1.0.4 RESET pulse width X1 Clock must be stable for at min. of

160us during RESET pulse low time.

160 µs

V

CC

HARDWARE

RSTN

MDC

32 CLOCKS

Latch-In of Hardware

Configuration Pins

Dual Function Pins

Become Enabled As Outputs

INPUT

OUTPUT

T1.0.3

T1.0.2

T1.0.1

T1.0.4

X1 Clock