42 www.national.com

DP83847

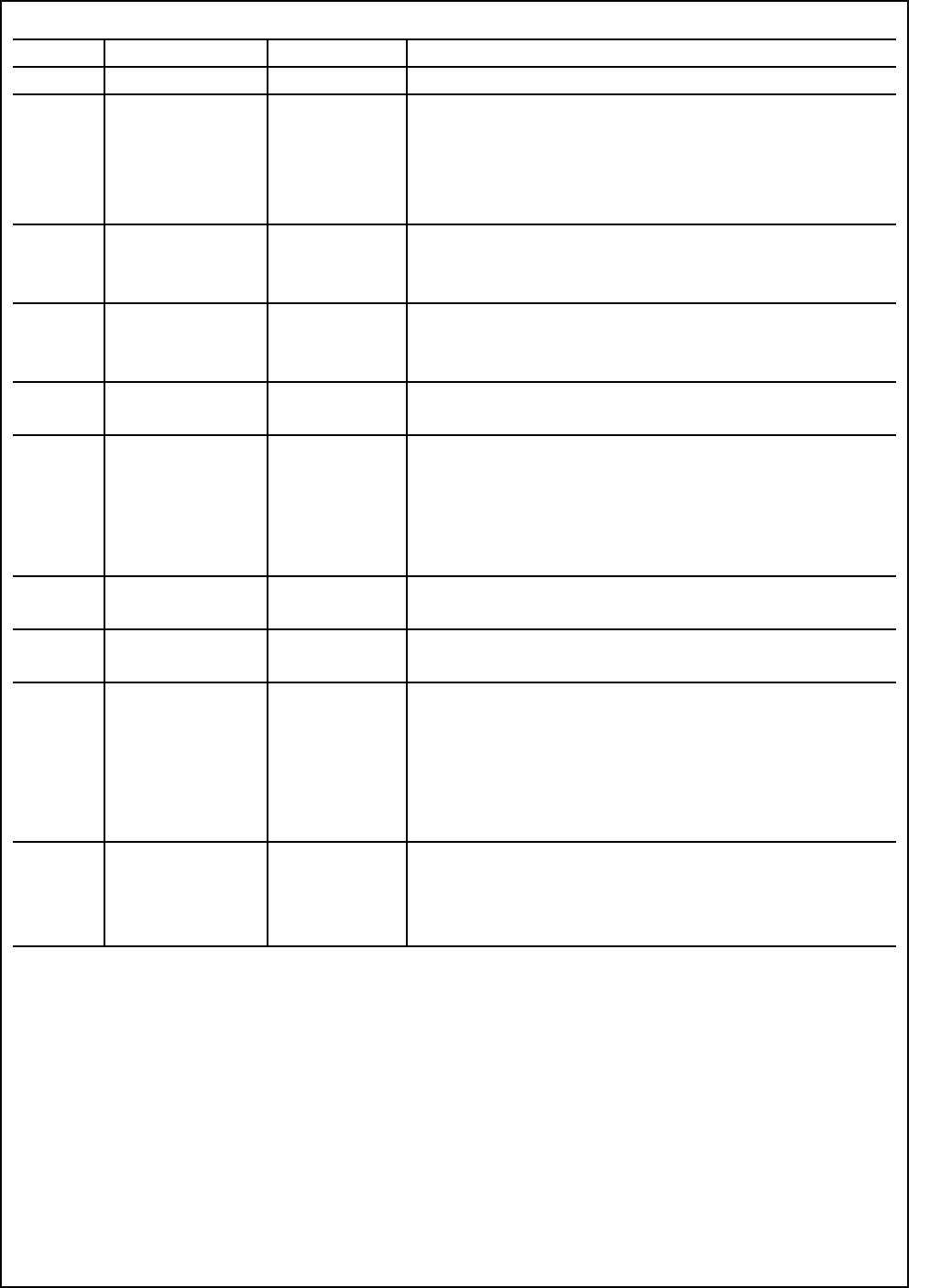

Table 22. 10Base-T Status/Control Register (10BTSCR), Address 0x1A

Bit Bit Name Default Description

15:9 Unused 0, RO

8 LOOPBACK_10_DIS 0, RW 10BASE-T Loopback Disable:

If bit 14 (Loopback) in the BMCR is 0:

1 = 10 Mb/s Loopback is disabled.

If bit 14 (Loopback) in the BMCR is 1:

1 = 10 Mb/s Loopback is enabled.

7 LP_DIS 0, RW Normal Link Pulse Disable:

1 = Transmission of NLPs is disabled.

0 = Transmission of NLPs is enabled.

6 FORCE_LINK_10 0, RW Force 10Mb Good Link:

1 = Forced Good 10Mb Link.

0 = Normal Link Status.

5 RESERVED 0, RW RESERVED:

Must be zero.

4POLARITY RO/LH10Mb Polarity Status:

This bit is a duplication of bit 12 in the PHYSTS register. Both bits

will be cleared upon a read of 10BTSCR register, but not upon a

read of the PHYSIS register.

1 = Inverted Polarity detected.

0 = Correct Polarity detected.

3 RESERVED 0, RW RESERVED:

Must be zero.

2 RESERVED 1, RW RESERVED:

Must be set to one.

1 HEARTBEAT_DIS 0, RW Heartbeat Disable: This bit only has influence in half-duplex 10Mb

mode.

1 = Heartbeat function disabled.

0 = Heartbeat function enabled.

When the device is operating at 100Mb or configured for full

duplex operation, this bit will be ignored - the heartbeat func-

tion is disabled.

0 JABBER_DIS 0, RW Jabber Disable:

Applicable only in 10BASE-T.

1 = Jabber function disabled.

0 = Jabber function enabled.