DP83847 DsPHYTER II — Single 10/100 Ethernet Transceiver

©2002 National Semiconductor Corporation

www.national.com

February 2002

DP83847 DsPHYTER II — Single 10/100 Ethernet Transceiver

General Description

The DP83847 is a full feature single Physical Layer device

with integrated PMD sublayers to support both 10BASE-T

and 100BASE-TX Ethernet protocols over Category 3 (10

Mb/s) or Category 5 unshielded twisted pair cables.

The DP83847 is designed for easy implementation of

10/100 Mb/s Ethernet home or office solutions. It interfaces

to Twisted Pair media via an external transformer. This

device interfaces directly to MAC devices through the IEEE

802.3u standard Media Independent Interface (MII) ensur-

ing interoperability between products from different ven-

dors.

The DP83847 utilizes on chip Digital Signal Processing

(DSP) technology and digital Phase Lock Loops (PLLs) for

robust performance under all operating conditions,

enhanced noise immunity, and lower external component

count when compared to analog solutions.

Applications

■ LAN on Motherboard

■ Embedded Applications

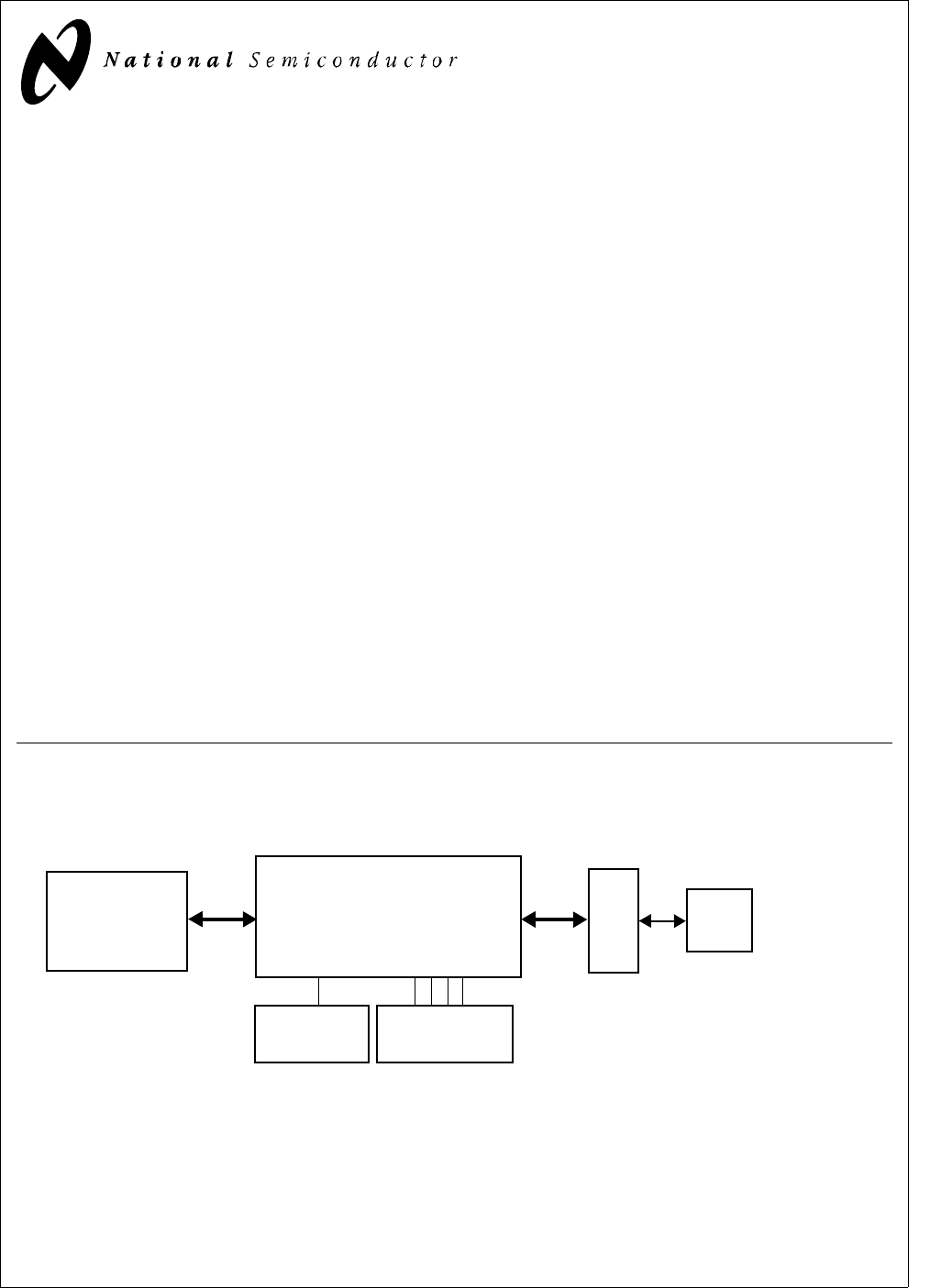

System Diagram

Status

10BASE-T

or

100BASE-TX

MII

25 MHz

Typical DsPHYTER II application

Ethernet MAC

Magnetics

RJ-45

Clock

LEDs

DP83847

10/100 Mb/s

DsPHYTER II

Features

■ Low-power 3.3V, 0.18µm CMOS technology

■ Power consumption < 351mW (typical)

■ 5V tolerant I/Os

■ 5V/3.3V MAC interface

■ IEEE 802.3 ENDEC, 10BASE-T transceivers and filters

■ IEEE 802.3u PCS, 100BASE-TX transceivers and filters

■ IEEE 802.3 compliant Auto-Negotiation

■ Output edge rate control eliminates external filtering for

Transmit outputs

■ BaseLine Wander compensation

■ IEEE 802.3u MII (16 pins/port)

■ LED support (Link, Rx, Tx, Duplex, Speed, Collision)

■ Single register access for complete PHY status

■ 10/100 Mb/s packet loopback BIST (Built in Self Test)

■ 56-pin LLP package (9w) x (9l) x (.75h) mm