ADM485E/ADM487E/ADM1487E

Rev. 0 | Page 5 of 16

V

CC

= 5 V ± 5%, T

A

= T

MIN

to T

MAX

, unless otherwise noted.

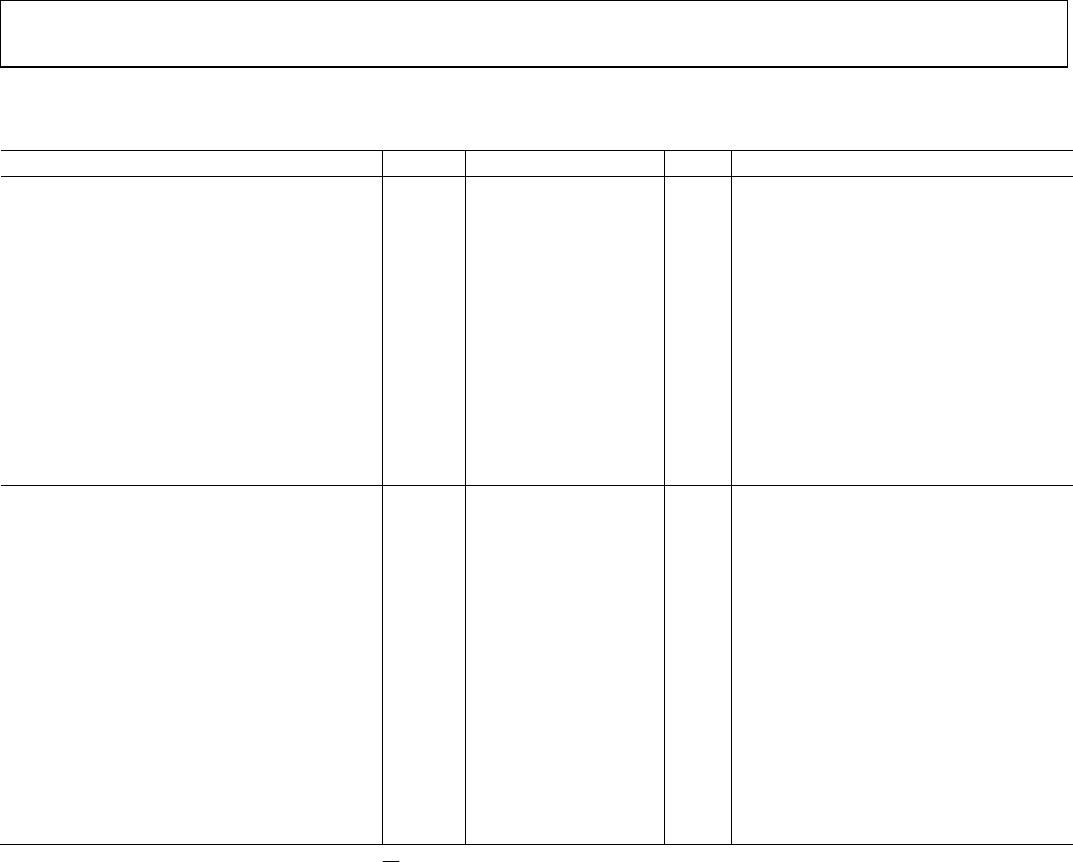

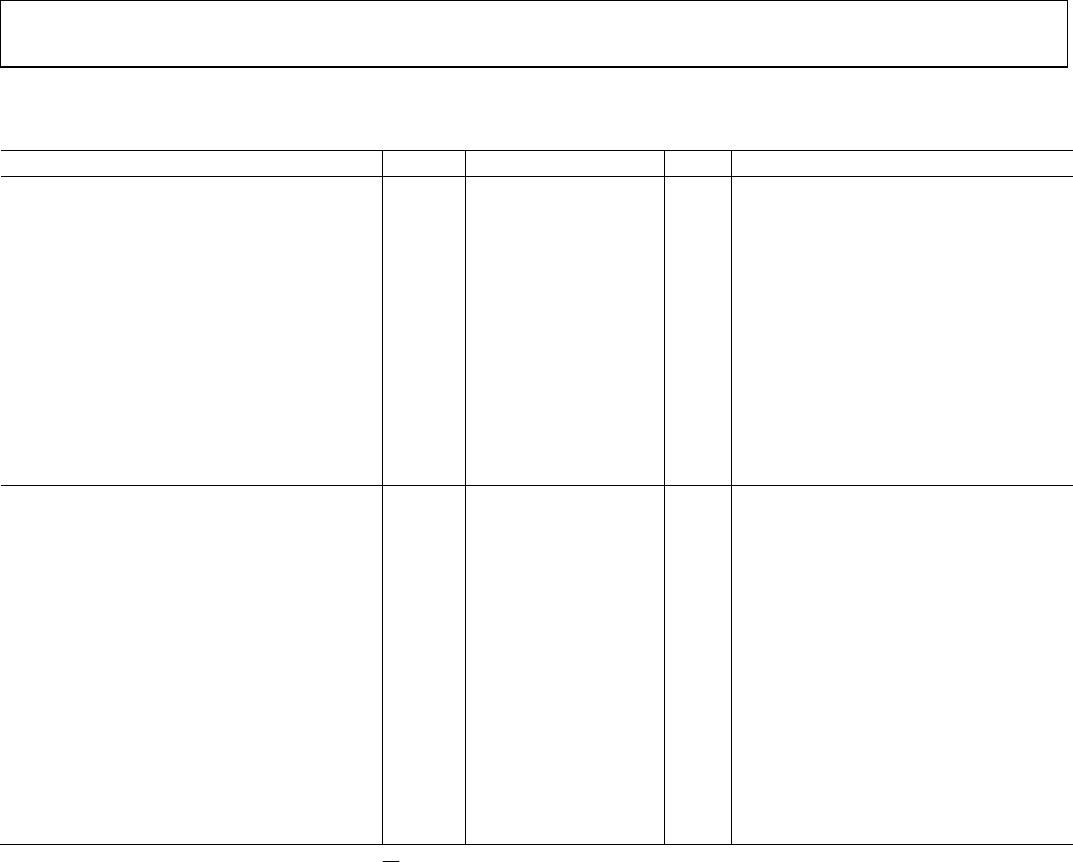

Table 4. ADM487E

Parameter Symbol Min Typ Max Unit Test Conditions/Comments

DRIVER

Input to Output t

DPLH

250 800 2000 ns

R

DIFF

= 54 Ω, CL1 = CL2 = 100 pF

(see

Figure 19 and Figure 20)

t

DPHL

250 800 2000 ns

R

DIFF

= 54 Ω, CL1 = CL2 = 100 pF

(see

Figure 19 and Figure 20)

Output Skew to Output t

SKEW

250 20 800 ns

R

DIFF

= 54 Ω, CL1 = CL2 = 100 pF

(see

Figure 19 and Figure 20)

Rise/Fall Time t

DR

, t

DF

250 2000 ns

R

DIFF

= 54 Ω, CL1 = CL2 = 100 pF

(see

Figure 19 and Figure 20)

Enable Time to High Level t

DZH

250 2000 ns C

RL

= 100 pF, S2 closed (see Figure 21)

Enable Time to Low Level t

DZL

2000 ns C

RL

= 100 pF, S1 closed (see Figure 22)

Disable Time from Low Level t

DLZ

300 3000 ns C

RL

= 15 pF, S1 closed (see Figure 22)

Disable Time from High Level t

DHZ

300 3000 ns C

RL

= 15 pF, S2 closed (see Figure 21)

RECEIVER

Input to Output t

RPLH

250 2000 ns R

DIFF

= 54 Ω, CL1 = CL2 = 100 pF

t

RPHL

250 2000 ns

R

DIFF

= 54 Ω, CL1 = CL2 = 100 pF

(see

Figure 19 and Figure 20)

|t

PLH

− t

PHL

| Differential Receiver Skew t

SKEW

100 ns

C

RL

= 15 pF, S1 closed

(see

Figure 23 and Figure 24)

Enable Time to Low Level t

RZL

25 50 ns C

RL

= 15 pF, S2 closed (see Figure 25)

Enable Time to High Level t

RZL

25 50 ns C

RL

= 15 pF, S1 closed (see Figure 25)

Disable Time from Low Level t

RLZ

25 50 ns C

RL

= 15 pF, S2 closed (see Figure 25)

Disable Time from High Level t

RHZ

25 50 ns t

PLH

, t

PHL

< 50% of data period

Maximum Data Rate f

MAX

250 kbps

Time to Shutdown

1

t

DZH(SHDN)

50 200 600 ns C

L

= 100 pF, S2 closed (see Figure 21)

Driver Enable from Shutdown to Output High t

DZL(SHDN)

5000 ns C

L

= 100 pF, S1 closed (see Figure 22)

Driver Enable from Shutdown to Output Low t

RZL(SHDN)

5000 ns C

L

= 15 pF, S2 closed (see Figure 25)

Receiver Enable from Shutdown to Output High t

RZH(SHDN)

5000 ns C

L

= 15 pF, S1 closed (see Figure 25)

1

The ADM487E is put into shutdown mode by bringing the

RE

high and the DE low. If the inputs are in this state for less than 50 ns, the parts are guaranteed not to

enter shutdown. If the inputs are in this state for at least 600 ns, the ADM487E is guaranteed to enter shutdown.