Philips Semiconductors Product specification

74F67416-bit serial/parallel-in, serial-out shift register (3-State)

1

1989 Feb 05 853–1248 92263

FEATURES

• 16-bit serial I/O shift register

• 16-bit parallel-in/serial-out converter

• Recirculating serial shifting

• Common serial data I/O pin (3-State)

DESCRIPTION

The 74F674 is a 16-bit shift register with serial and parallel load

capability and serial output. A single pin serves alternately as an

input for serial entry or as a 3-State serial output. In the serial out

mode the data recirculates in the register. Chip Select, Read/Write

and Mode inputs provide control flexibility. The 74F674 operates in

one of four modes, as indicated in the Function table.

Hold: A High signal on the Chip Select (CS

) input prevents clocking

and forces the Serial Input/Output (SI/O) 3-State buffer into the high

impedance state.

Serial load: Data present on the SI/O pin shifts into the register on

the falling edge of CP

. Data enters the Q0 position and shifts toward

Q15 on successive clocks.

Serial output: The SI/O 3-State buffer is active and the register

contents are shifted out from Q15 and simultaneously shifted back

into Q0.

Parallel load: Data present on D0–D15 is entered into the register

on the falling edge of CP

. The SI/O 3-State buffer is active and

represents the Q15 output. To prevent false clocking, CP

must be

Low during a Low-to-High transition of CS

.

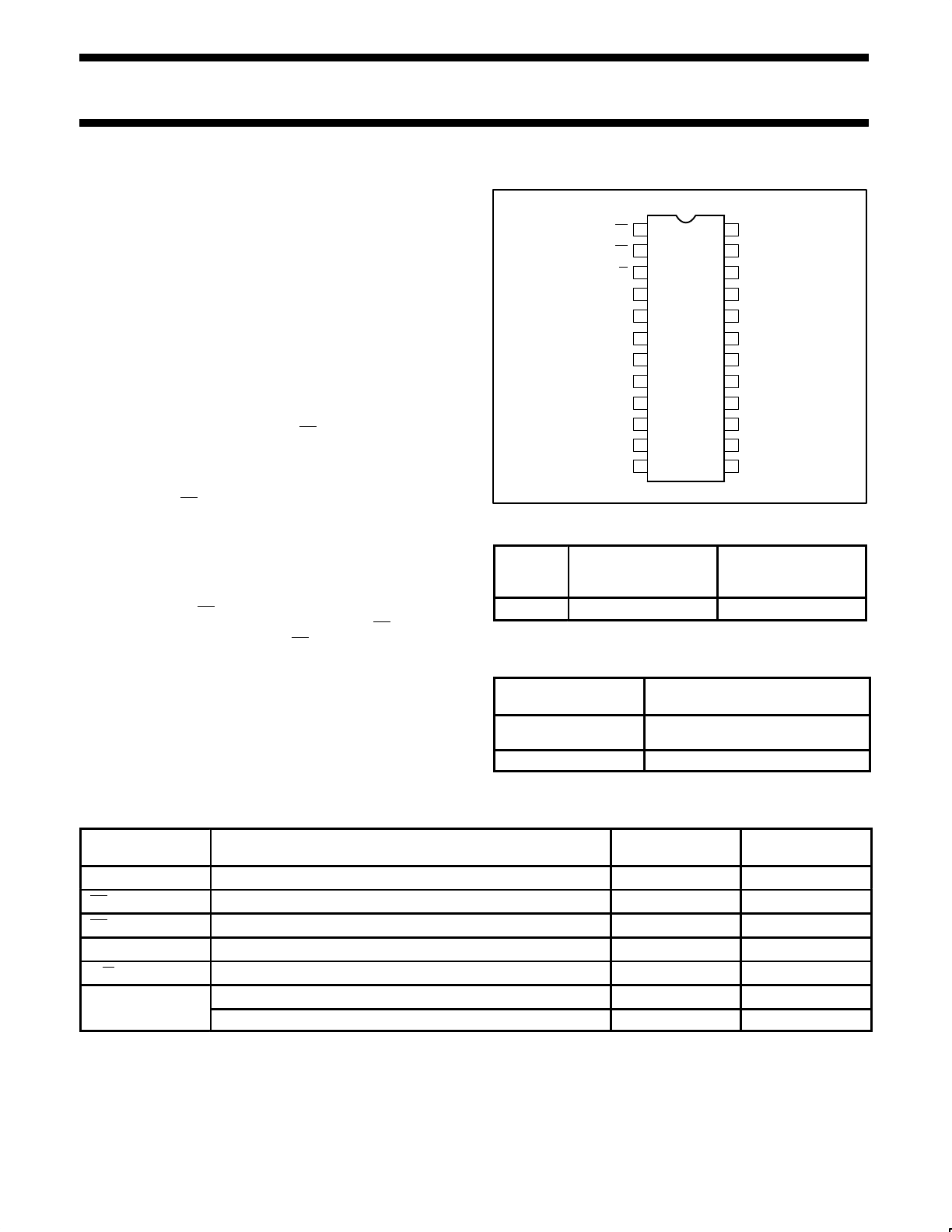

PIN CONFIGURATION

241

V

CC

CS

23

22

21

20

19

18

17

16

10 15

9

8

7

6

5

4

3

2

D15

D14

D11

D10

D9

D8

CP

M

SI/O

D1

D2

D3

D13

D12

NC

R/W

SF01188

D0

D7

14

12 13

11

D6

D4

GND

D5

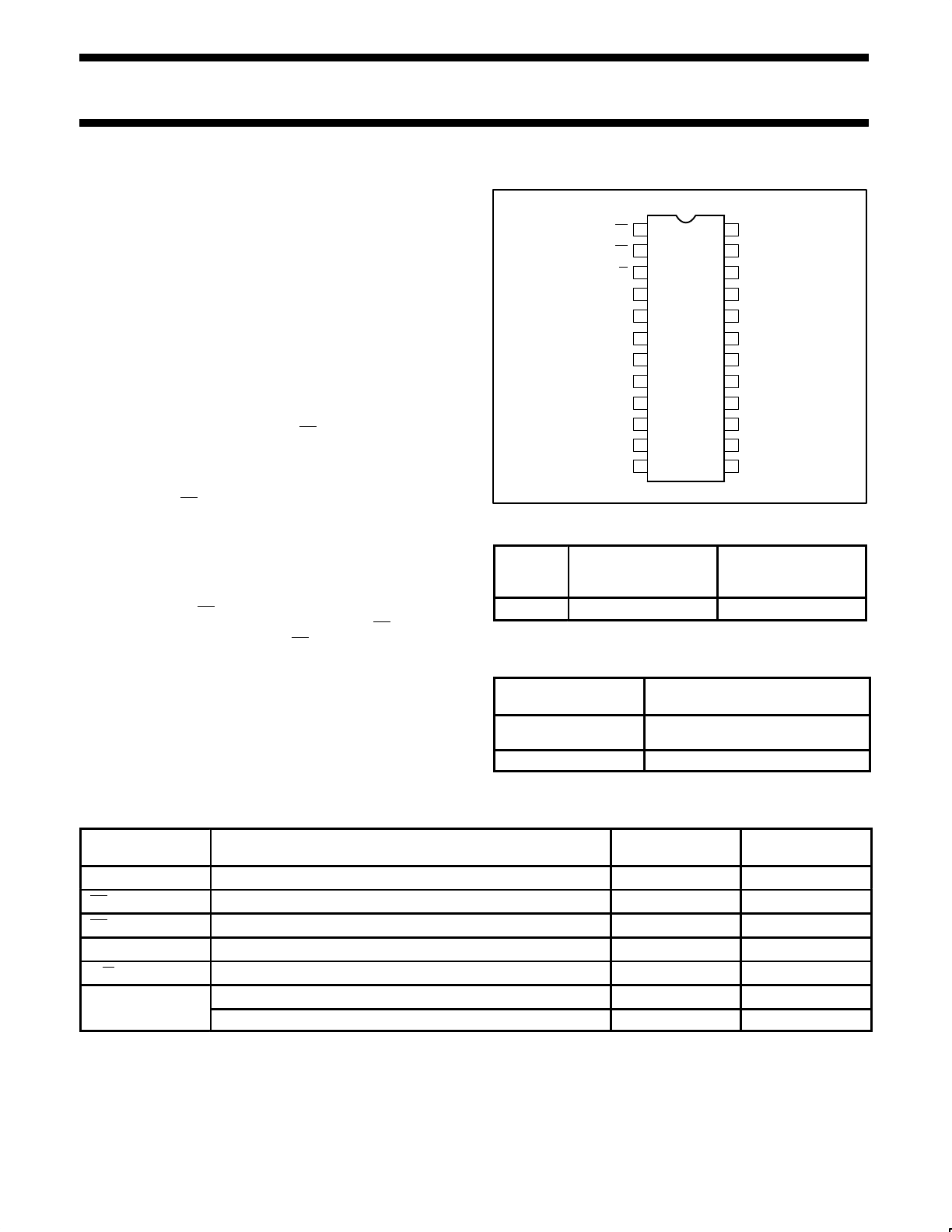

TYPE TYPICAL f

MAX

TYPICAL SUPPLY

CURRENT

(TOTAL)

74F674 95MHz 55mA

ORDERING INFORMATION

DESCRIPTION COMMERCIAL RANGE

V

CC

= 5V ±10%, T

amb

= 0°C to +70°C

24-Pin Plastic Slim DIP

(300mil)

N74F674N

24-Pin Plastic SOL N74F674D

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS DESCRIPTION

74F(U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

D0–D15 Parallel data inputs 1.0/1.0 20µA/0.6mA

CS Chip Select input (active Low) 1.0/1.0 20µA/0.6mA

CP Clock Pulse input (active falling edge) 1.0/1.0 20µA/0.6mA

M Mode select input 1.0/1.0 20µA/0.6mA

R/W Read/Write input 1.0/1.0 20µA/0.6mA

Serial data input or 3.5/1.0 70mA/0.6mA

Serial 3-state output 150/40 3.0mA/24mA

NOTE: One (1.0) FAST Unit Load is defined as: 20µA in the High state and 0.6mA in the Low state.