MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

17

INTERRUPTS

Interrupts can be caused by 15 different sources consisting of 3 ex-

ternal, 10 internal, 1 software, and reset. Interrupts are vectored in-

terrupts with priorities as shown in Table 1. Reset is also included in

the table because its operation is similar to an interrupt.

When an interrupt is accepted,

(1) The contents of the program counter and processor status

register are automatically stored into the stack.

(2) The interrupt disable flag I is set to “1” and the corresponding

interrupt request bit is set to “0.”

(3) The jump destination address stored in the vector address enters

the program counter.

Other interrupts are disabled when the interrupt disable flag is set to

“1.”

All interrupts except the BRK instruction interrupt have an interrupt

request bit and an interrupt enable bit. The interrupt request bits are

in interrupt request registers 1 and 2 and the interrupt enable bits are

in interrupt control registers 1 and 2. Figures 10 to 13 show the inter-

rupt-related registers.

Interrupts other than the BRK instruction interrupt and reset are ac-

cepted when the interrupt enable bit is “1,” interrupt request bit is “1,”

and the interrupt disable flag is “0.” The interrupt request bit can be

set to “0” by a program, but not set to “1.” The interrupt enable bit can

be set to “0” and “1” by a program.

Reset is treated as a non-maskable interrupt with the highest priority.

Figure 9 shows interrupt control.

Interrupt Causes

(1) VSYNC and CRT interrupts

The VSYNC interrupt is an interrupt request synchronized with

the vertical sync signal.

The CRT interrupt occurs after character block display to the CRT

is completed.

(2) INT1, INT2 interrupts

With an external interrupt input, the system detects that the level

of a pin changes from “L” to “H” or from “H” to “L,” and generates

an interrupt request. The input active edge can be selected by

bits 3 and 4 of the interrupt interval determination control register

(address 00D816) : when this bit is “0,” a change from “L” to “H” is

detected; when it is “1,” a change from “H” to “L” is detected.

Note that all bits are cleared to “0” at reset.

(3) Timer 1, 2, 3 and 4 interrupts

An interrupt is generated by an overflow of timer 1, 2, 3 or 4.

(4) Serial I/O interrupt

This is an interrupt request from the clock synchronous serial

I/O function.

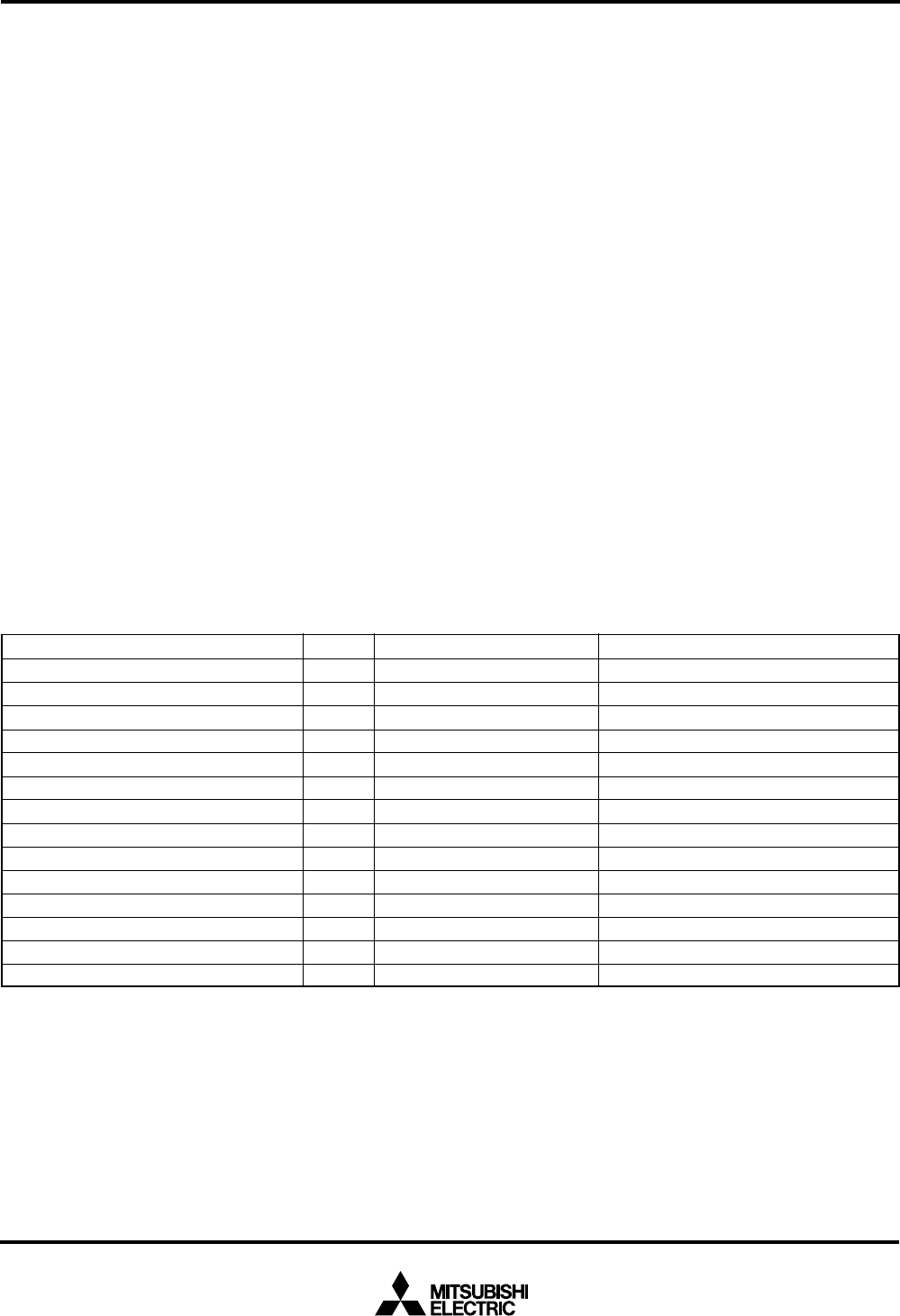

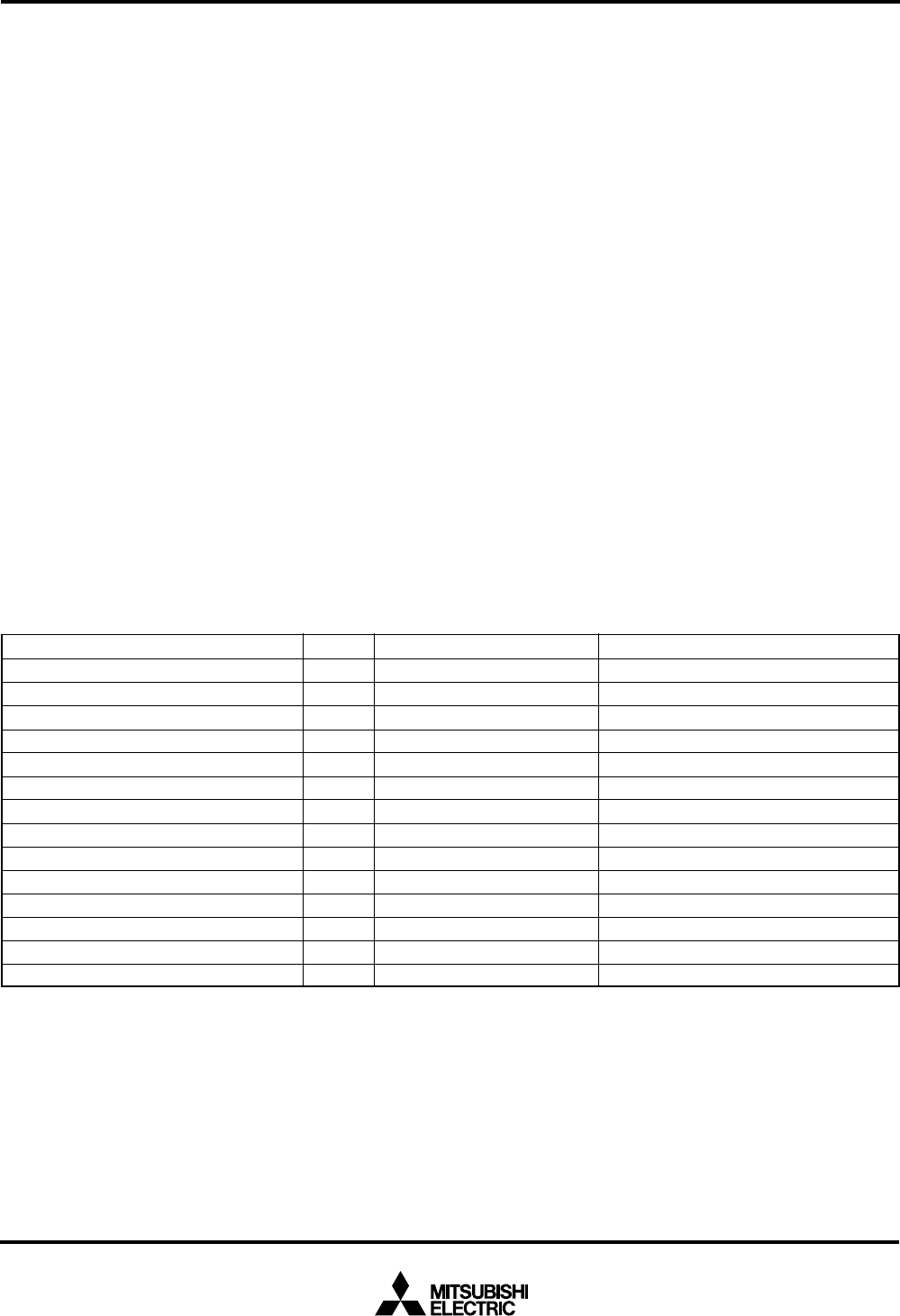

Priority

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Vector Addresses

FFFF16, FFFE16

FFFD16, FFFC16

FFFB16, FFFA16

FFF916, FFF816

FFF716, FFF616

FFF516, FFF416

FFF316, FFF216

FFF116, FFF016

FFEF16, FFEE16

FFED16, FFEC16

FFEB16, FFEA16

FFE716, FFE616

FFE316, FFE216

FFDF16, FFDE16

Interrupt Source

Reset

CRT interrupt

INT1 interrupt

INT2 interrupt

Timer 4 interrupt

f(XIN)/4096 interrupt

VSYNC interrupt

Timer 3 interrupt

Timer 2 interrupt

Timer 1 interrupt

Serial I/O interrupt

Multi-master I

2

C-BUS interface interrupt

Timer 5 · 6 interrupt

BRK instruction interrupt

Remarks

Non-maskable

Active edge selectable

Active edge selectable

Active edge selectable

Source switch by software (See note)

Non-maskable (software interrupt)

Table 1. Interrupt Vector Addresses and Priority

Note : Switching a source during a program causes an unnecessary interrupt. Therefore, set a source at initializing of program.