MITSUBISHI MICROCOMPUTERS

M37207MF-XXXSP/FP, M37207M8-XXXSP

M37207EFSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER

and ON-SCREEN DISPLAY CONTROLLER

50

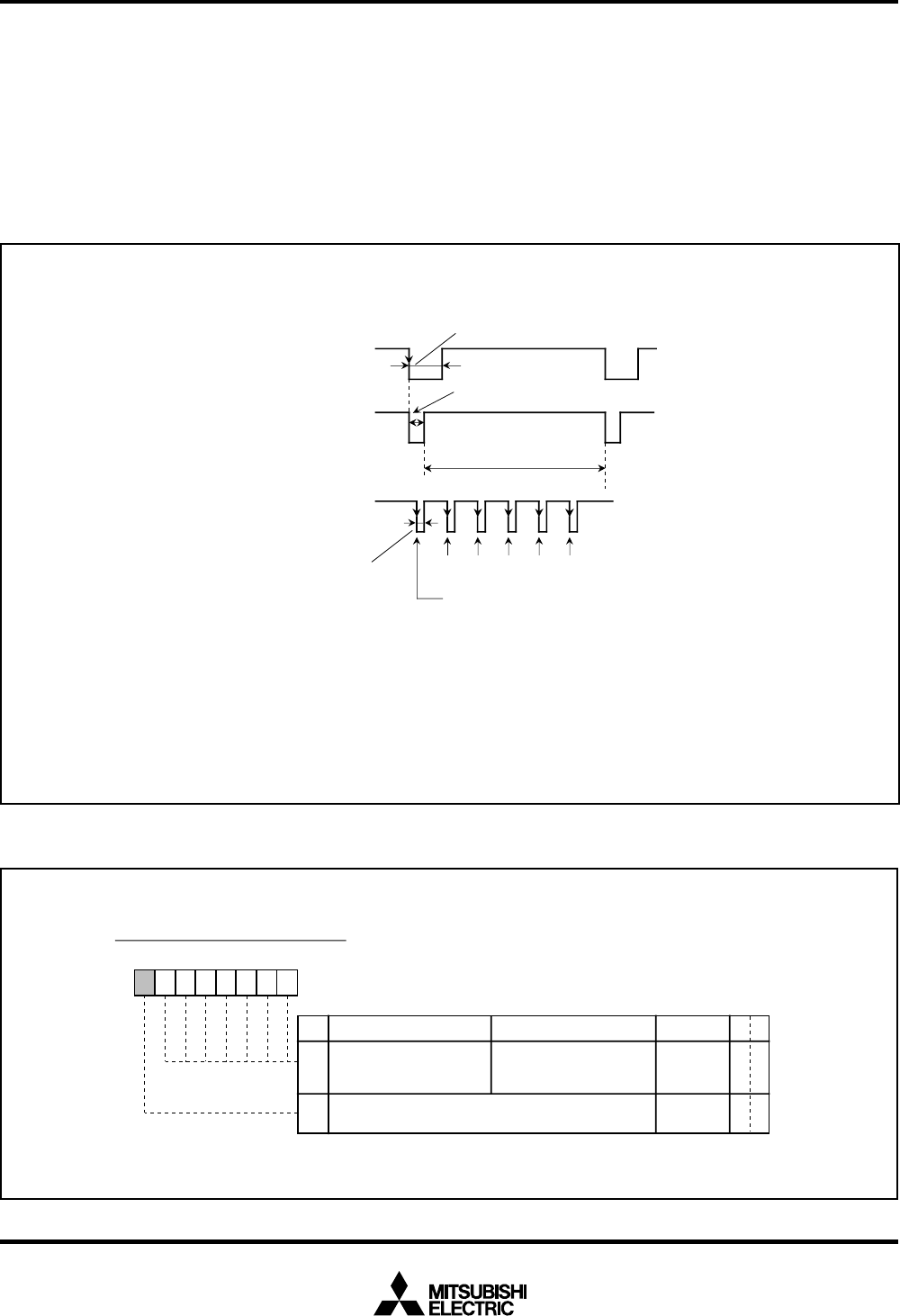

The display position in the vertical direction is determined by count-

ing the horizontal sync signal (HSYNC). At this time, when VSYNC and

HSYNC are positive polarity (negative polarity), it starts to count the

rising edge (falling edge) of HSYNC signal from after fixed cycle of

rising edge (falling edge) of VSYNC signal. So interval from rising edge

(falling edge) of VSYNC signal to rising edge (falling edge) of HSYNC

signal needs enough time (2 machine cycles or more) for avoiding

jitter. The polarity of HSYNC and VSYNC signals can select with the

CRT port control register (address 00EC16).

Fig. 48. Vertical Position Register i

Fig. 47. Supplement Explanation for Display Position

When bits 0 and 1 of the CRT port control register

(address 00EC

16

) are set to “1” (negative polarity)

V

SYNC

signal input

V

SYNC

control

signal in

microcomputer

0.125 to 0.50 [

µ

s]

( at f(X

IN

) = 8MHz)

Period of counting

H

SYNC

signal

(Note 2)

H

SYNC

signal input

Not count

12345

Notes 1 : The vertical position is determined by counting falling edge of H

SYNC

signal after rising edge of V

SYNC

control signal in the microcomputer.

2 : Do not generate falling edge of H

SYNC

signal near rising edge of

V

SYNC

control signal in microcomputer to avoid jitter.

8 machine cycles

or more

8 machine cycles

or more

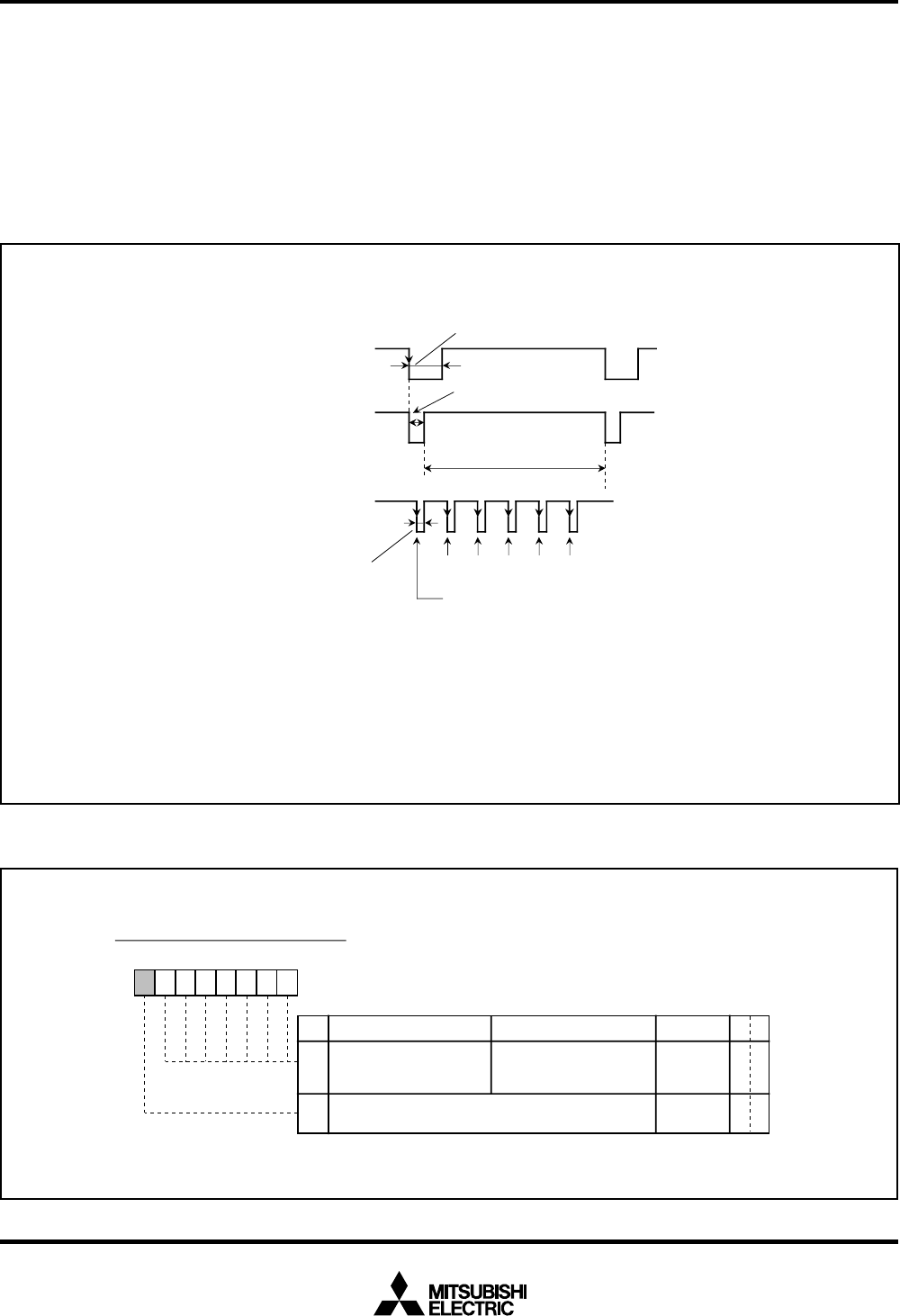

b7 b6 b5 b4 b3 b2 b1 b0

Vertical position register i (CVi) (i = 1 to 3) [Addresses 00E1

16

to 00E3

16

]

B Name Functions

After reset

R

W

Vertical Position Register i

0

to

6

7

Vertical display start positions

128 steps (00

16

to 7F

16

)

Indeterminate

0

(CVi : CVi0 to CVi6)

Nothing is assigned. This bit is a write disable bit.

When this bit is read out, the value is “0.”

RW

R—