µA

µA

µA

mA

V

CC

= 5.5 V, V

O

= 2.7 V

V

CC

= 5.5 V, V

O

= 0.4 V

V

CC

= 5.5 V, V

I

= 2.7 V

V

CC

= 5.5 V, V

I

= 0.4 V

I

OZH

I

OZL

I

IH

I

IL

ns

Pulse duration (see Note 2)

t

w

PAL16L8A-2M, PAL16R4A-2M, PAL16R6A-2M, PAL16R8A-2M

STANDARD HIGH-SPEED PAL

CIRCUITS

SRPS016 – D2705, FEBRUARY 1984 – REVISED MARCH 1992

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

11

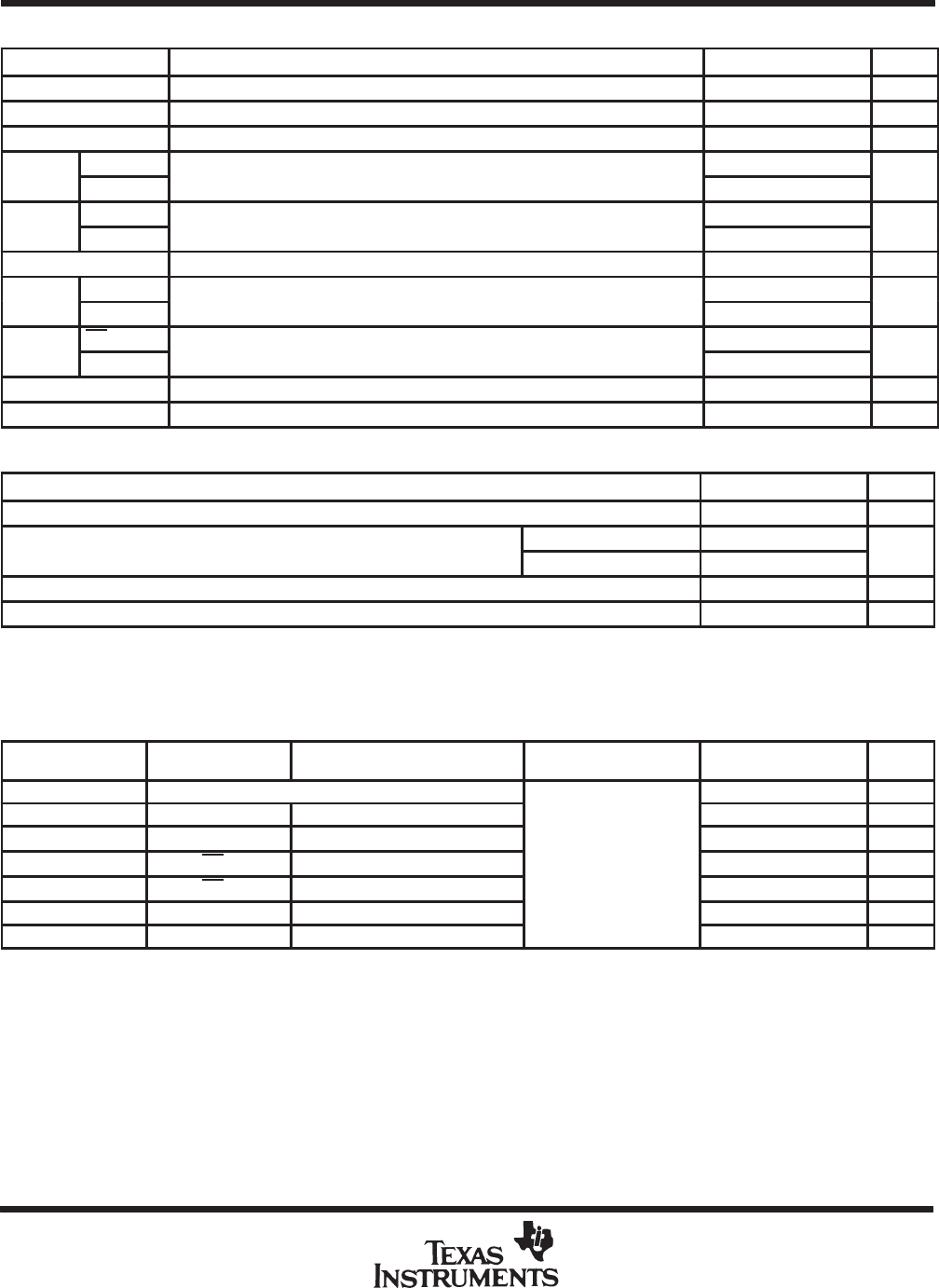

electrical characteristics over recommended operating free-air temperature range

PARAMETER TEST CONDITIONS MIN TYP

†

MAX UNIT

V

IK

V

CC

= 4.5 V, I

I

= –18 mA –1.5 V

V

OH

V

CC

= 4.5 V, I

OH

= –2 mA 2.4 3.2 V

V

OL

V

CC

= 4.5 V, I

OL

= 12 mA 0.25 0.4 V

Outputs 20

I/O ports 100

Outputs –20

I/O ports –100

I

I

V

CC

= 5.5 V, V

I

= 5.5 V 0.2 mA

I/O Ports 100

All others 25

OE input –0.2

All others –0.1

I

OS

‡

V

CC

= 5.5 V, V

O

= 0.5 V –30 –250 mA

I

CC

V

CC

= 5.5 V, V

I

= 0, Outputs open 75 90 mA

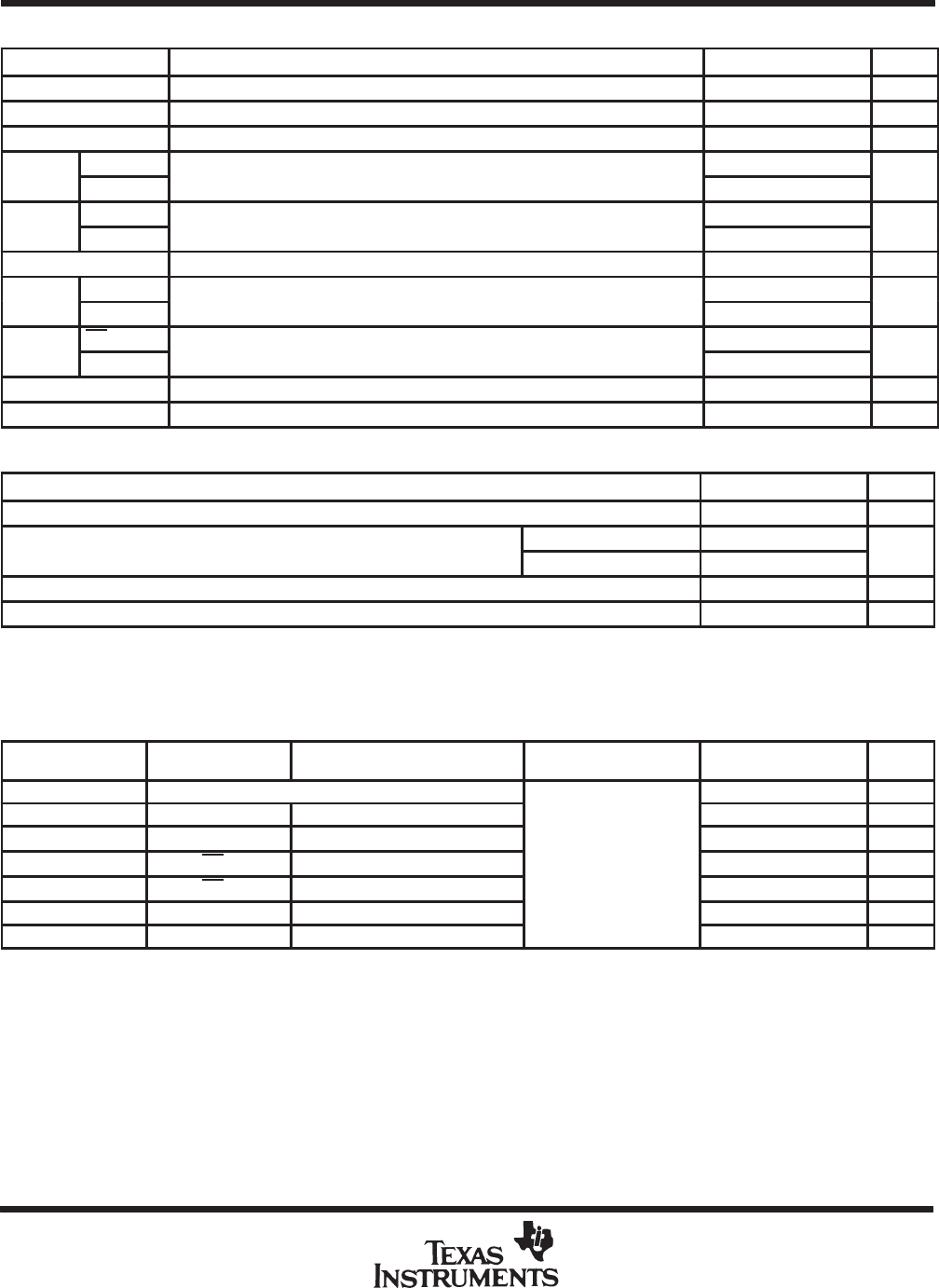

timing requirements

MIN MAX UNIT

f

clock

Clock Frequency 0 16 MHz

Clock high 25

Clock low 25

t

su

Setup time, input or feedback before CLK↑ 35 ns

t

h

Hold time, input or feedback after CLK↑ 0 ns

NOTE 2: The total clock period of clock high and clock low must not exceed clock frequency, f

clock

. The minimum pulse durations specified are

only for clock high or low, but not for both simultaneously.

switching characteristics over recommended ranges of supply voltage and operating free-air

temperature (unless otherwise noted)

PARAMETER

FROM

(INPUT)

TO

(OUTPUT)

TEST CONDITION MIN TYP

†

MAX UNIT

f

max

16 25 MHz

t

pd

I, I/O O, I/O

25 40 ns

t

pd

CLK↑ Q R1 = 390 Ω, 11 25 ns

t

en

OE↓ Q R2 = 750 Ω, 20 25 ns

t

dis

OE↑ Q See Figure 1 11 25 ns

t

en

I, I/O O, I/O 25 40 ns

t

dis

I, I/O O, I/O 25 35 ns

†

All typical values are at V

CC

= 5 V, T

A

= 25°C.

‡

Not more than one output should be shorted at a time and the duration of the short circuit should not exceed one second. Set V

O

at 0.5 V to avoid

test equipment degradation.