3

Absolute Maximum Ratings Thermal Information

DC Supply Voltage, V

CC

. . . . . . . . . . . . . . . . . . . . . . . . -0.5V to 7V

DC Input Diode Current, I

IK

For V

I

< -0.5V or V

I

> V

CC

+ 0.5V. . . . . . . . . . . . . . . . . . . . . .±20mA

DC Output Diode Current, I

OK

For V

O

< -0.5V or V

O

> V

CC

+ 0.5V . . . . . . . . . . . . . . . . . . . .±20mA

DC Output Source or Sink Current per Output Pin, I

O

For V

O

> -0.5V or V

O

< V

CC

+ 0.5V . . . . . . . . . . . . . . . . . . . .±25mA

DC V

CC

or Ground Current, I

CC or

I

GND

. . . . . . . . . . . . . . . . . .±50mA

Operating Conditions

Temperature Range (T

A

) . . . . . . . . . . . . . . . . . . . . . -55

o

C to 125

o

C

Supply Voltage Range, V

CC

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V

HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, V

I

, V

O

. . . . . . . . . . . . . . . . . 0V to V

CC

Input Rise and Fall Time

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max)

4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max)

6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

Thermal Resistance (Typical, Note 1) θ

JA

(

o

C/W)

E (PDIP) Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

M (SOIC) Package. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Maximum Junction Temperature (Hermetic Package or Die) . . . 175

o

C

Maximum Junction Temperature (Plastic Package) . . . . . . . . 150

o

C

Maximum Storage Temperature Range . . . . . . . . . .-65

o

C to 150

o

C

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300

o

C

(SOIC - Lead Tips Only)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation

of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1. The package thermal impedance is calculated in accordance with JESD 51-7.

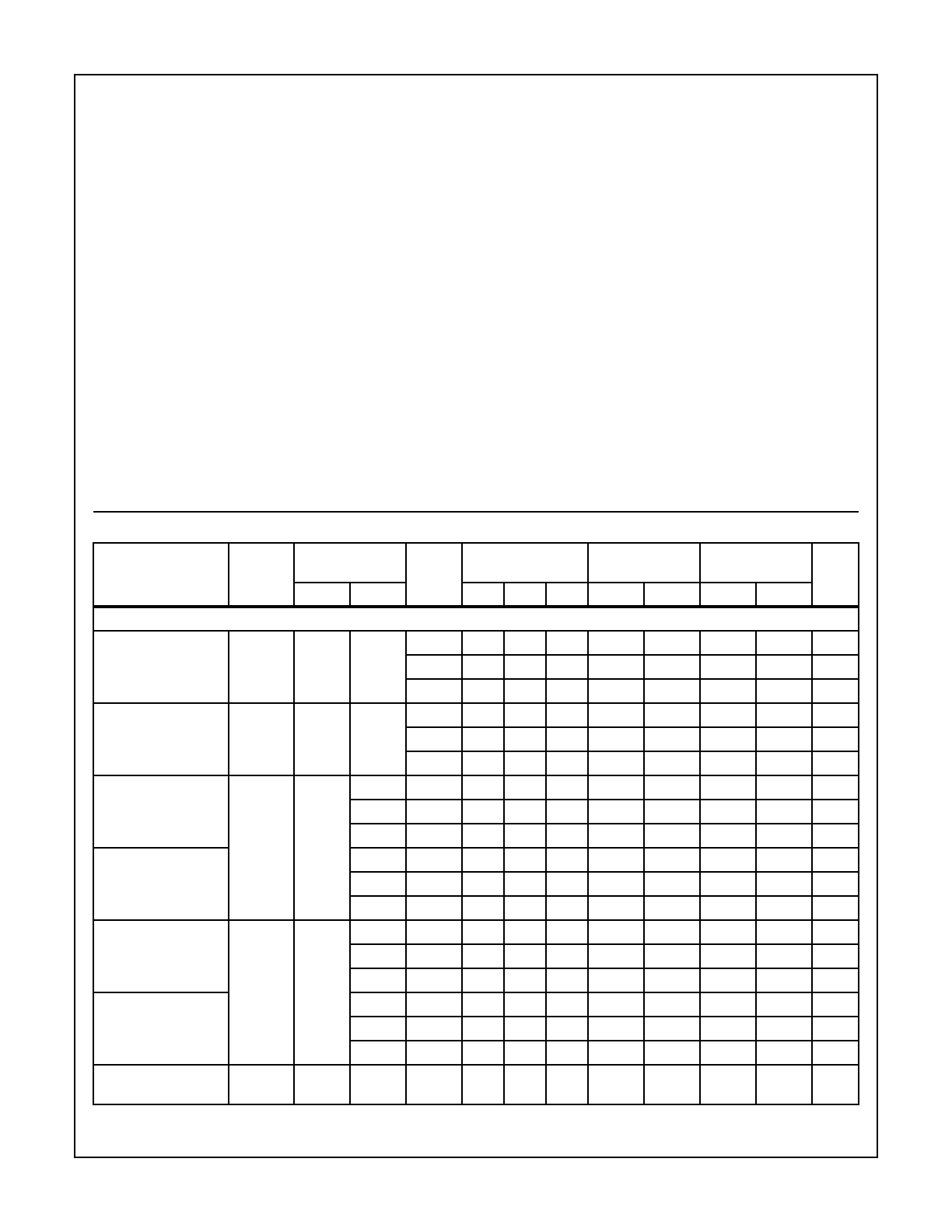

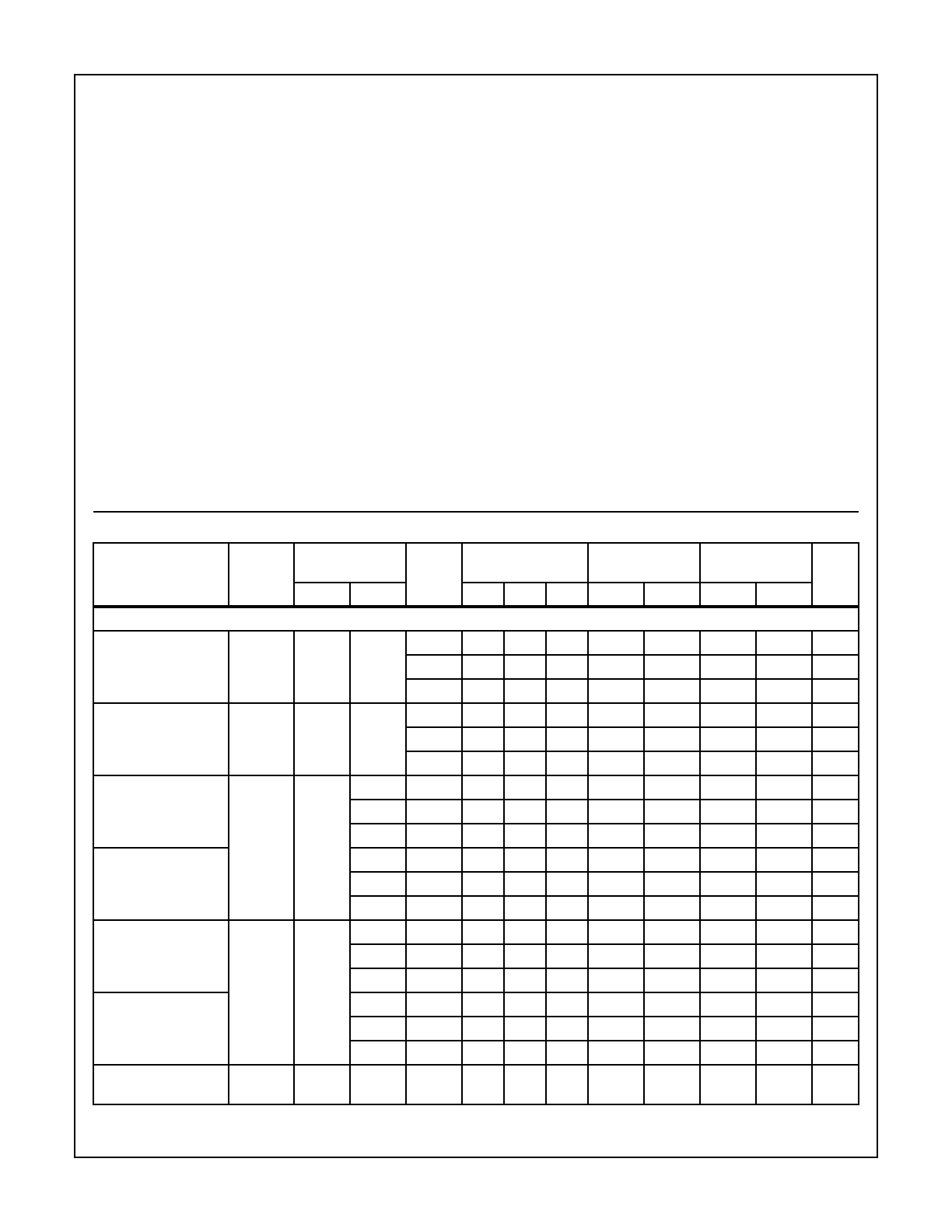

DC Electrical Specifications

PARAMETER SYMBOL

TEST

CONDITIONS

V

CC

(V)

25

o

C -40

o

C TO 85

o

C -55

o

C TO 125

o

C

UNITSV

I

(V) I

O

(mA) MIN TYP MAX MIN MAX MIN MAX

HC TYPES

High Level Input

Voltage

V

IH

- - 2 1.5 - - 1.5 - 1.5 - V

4.5 3.15 - - 3.15 - 3.15 - V

6 4.2 - - 4.2 - 4.2 - V

Low Level Input

Voltage

V

IL

- - 2 - - 0.5 - 0.5 - 0.5 V

4.5 - - 1.35 - 1.35 - 1.35 V

6 - - 1.8 - 1.8 - 1.8 V

High Level Output

Voltage

CMOS Loads

V

OH

V

IH

or

V

IL

-0.02 2 1.9 - - 1.9 - 1.9 - V

-0.02 4.5 4.4 - - 4.4 - 4.4 - V

-0.02 6 5.9 - - 5.9 - 5.9 - V

High Level Output

Voltage

TTL Loads

---------V

-4 4.5 3.98 - - 3.84 - 3.7 - V

-5.2 6 5.48 - - 5.34 - 5.2 - V

Low Level Output

Voltage

CMOS Loads

V

OL

V

IH

or

V

IL

0.02 2 - - 0.1 - 0.1 - 0.1 V

0.02 4.5 - - 0.1 - 0.1 - 0.1 V

0.02 6 - - 0.1 - 0.1 - 0.1 V

Low Level Output

Voltage

TTL Loads

---------V

4 4.5 - - 0.26 - 0.33 - 0.4 V

5.2 6 - - 0.26 - 0.33 - 0.4 V

Input Leakage

Current

I

I

V

CC

or

GND

-6--±0.1 - ±1-±1 µA

CD54HC00, CD74HC00, CD54HCT00, CD74HCT00