22

FN6849.3

December 16, 2011

The switching frequency can also be set to any value

between 200 kHz and 1.4 MHz using the I

2

C/SMBus

interface. The available frequencies are bounded by

the relation f

sw

= 8 MHz/N, (with 6<= N <= 40). See

Application Note AN2013 for details on configuring

the switching frequency using the I

2

C/SMBus inter-

face.

If multiple ZL2005Ps are used together, co

nnecting

the SYNC pins together will force all devices to syn-

chronize to one another. The CFG pin of one device

mu

st have its SYNC pin set as an output and the

remaining devices must have their SYNC pins set as

an input or all devices must be driven by the same

external clock source.

Note: The s

witching frequency read back using the

appropriate PMBus command will differ slightly from

the selected value in Table 17. The difference is due to

hardware quantization.

5.8 Selecting Power Train Components

The ZL2005P is a synchronous buck controller that

uses external MOSFETs, inductor and capacitors to

perform the power conversion process. The proper

selection of the external components is critical for

optimized performance. Zilker Labs offers an online

circuit design and simulation tool, PowerPilot, to

assist designers in this task.

Please visit

www.intersil.com/zilkerlabs/ to access

PowerPilot. For more detailed guidelines regarding

component s

election, please refer to Application Note

AN2011.

To select the appropriate power stage components for

a

set of desired performance goals, the power supply

requirements listed in Table 18 must be known.

Design Trade-offs

The design of a switching regulator power stage

require

s the user to consider trade-offs between cost,

size and performance. For example, size can be opti-

mized at the expense of efficiency. Additionally, cost

ca

n be optimized at the expense of size. For a detailed

description of circuit trade-offs, refer to Application

Note AN2011.

To start a design, select a switching frequency (f

SW

)

based on Table 19. This frequency is a starting point

and may be adjusted as the design progresses.

Table 19. Circuit Design Considerations

200 – 400 kHz Highest Larger

400 – 800 kHz Moderate Smaller

800 – 1400 kHz Lower Smallest

Inductor Selection

The output inductor selection pr

ocess will include sev-

eral trade-offs. A high inductance value will result in a

low

ripple current (I

opp

), which will reduce the output

capacitance requirement and produce a low output rip-

ple voltage, but may also compromise output transient

loa

d performance. Therefore, a balance must be

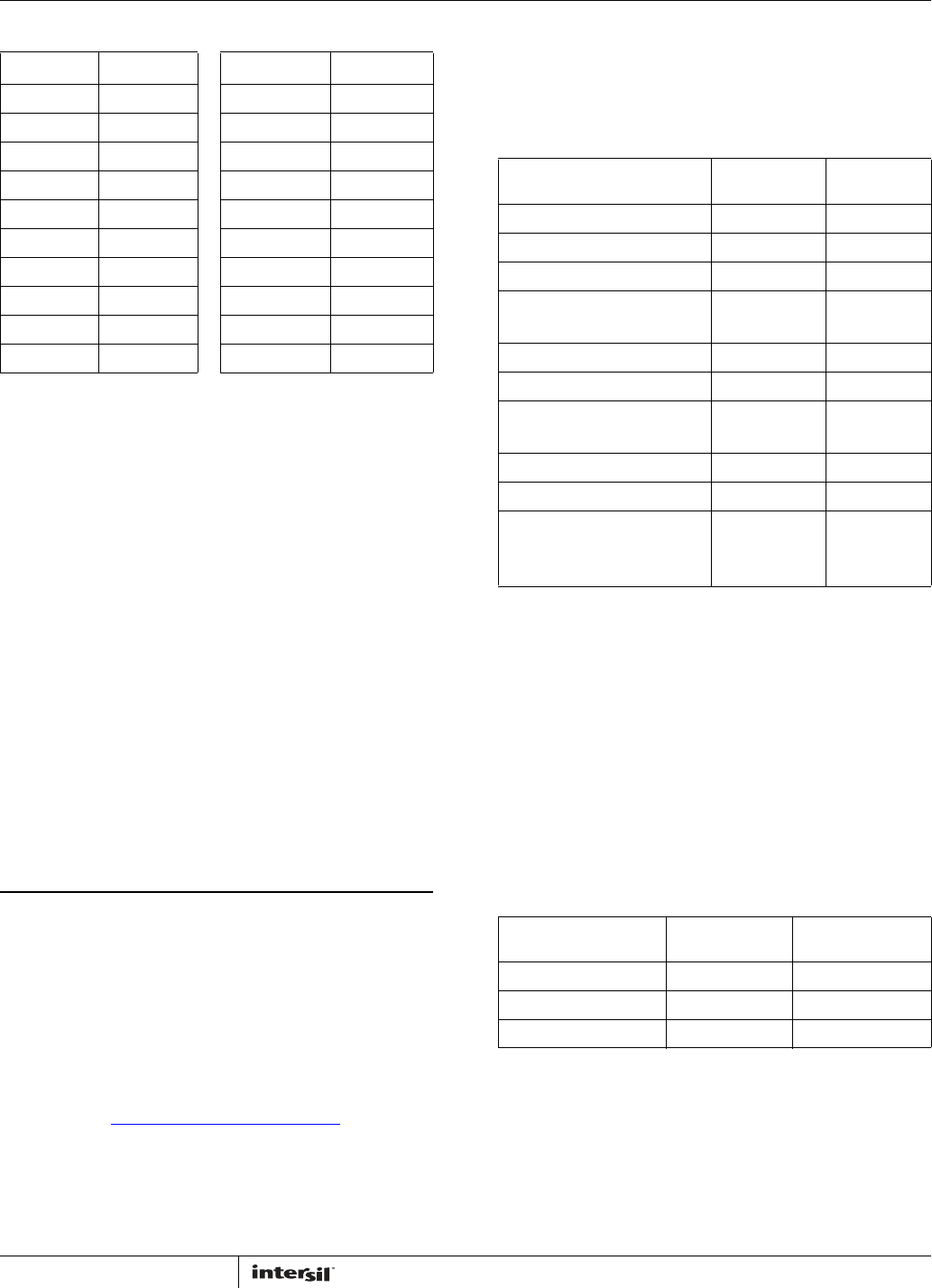

Table 17. R

SYNC

Resistor Values

f

SW

R

SYNC

f

SW

R

SYNC

200 kHz 10 kΩ 533 kHz 26.1 kΩ

222 kHz 11 kΩ 571 kHz 28.7 kΩ

242 kHz 12.1 kΩ 615 kHz 31.6 kΩ

267 kHz 13.3 kΩ 667 kHz 34.8 kΩ

296 kHz 14.7 kΩ 727 kHz 38.3 kΩ

320 kHz 16.2 kΩ 889 kHz 46.4 kΩ

364 kHz 17.8 kΩ 1000 kHz 51.1 kΩ

400 kHz 19.6 kΩ 1143 kHz 56.2 kΩ

421 kHz 21.5 kΩ 1333 kHz 68.1 kΩ

471 kHz 23.7 kΩ

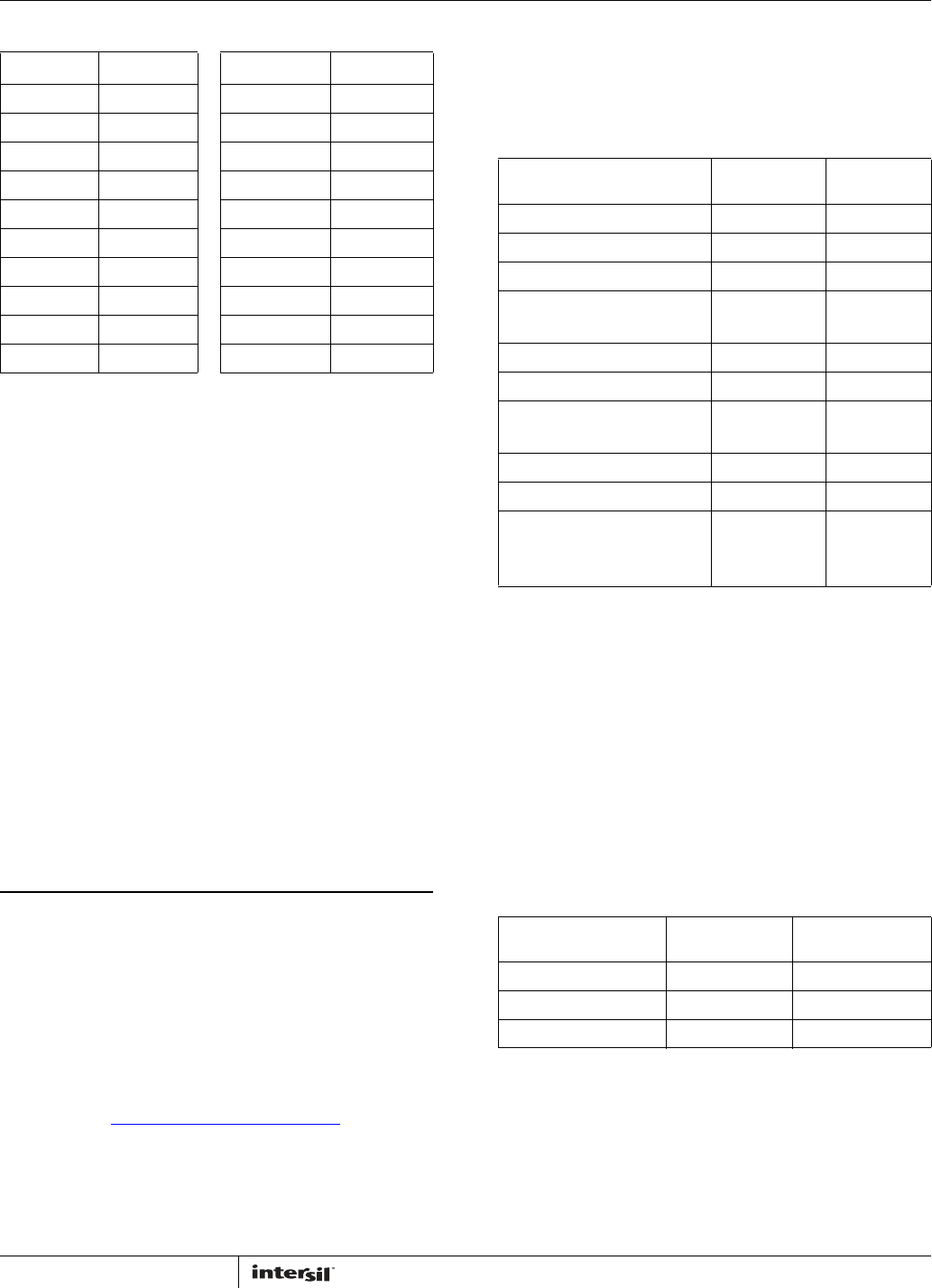

Table 18. Power Supply Requirements

Example

Parameter Range

Example

Value

Input voltage (V

IN

) 3.0 – 14.0 V 12 V

Output voltage (V

OUT

) 0.6 – 5.0 V 1.2 V

Output current (I

OUT

) 0 to ~25 A 20 A

Output voltage ripple

(V

orip

)

< 3% of

V

OUT

1% of

V

OUT

Output load step (I

ostep

)< Io50% of I

o

Output load step rate — 10 A/µS

Allowable output

deviation due to load step

—± 50 mV

Maximum PCB temp. 120°C 85°C

Desired efficiency — 85%

Other considerations Various

Optimize

for small

size

Frequency

Range

Efficiency Circuit Size

ZL2005P