8

FN6849.3

December 16, 2011

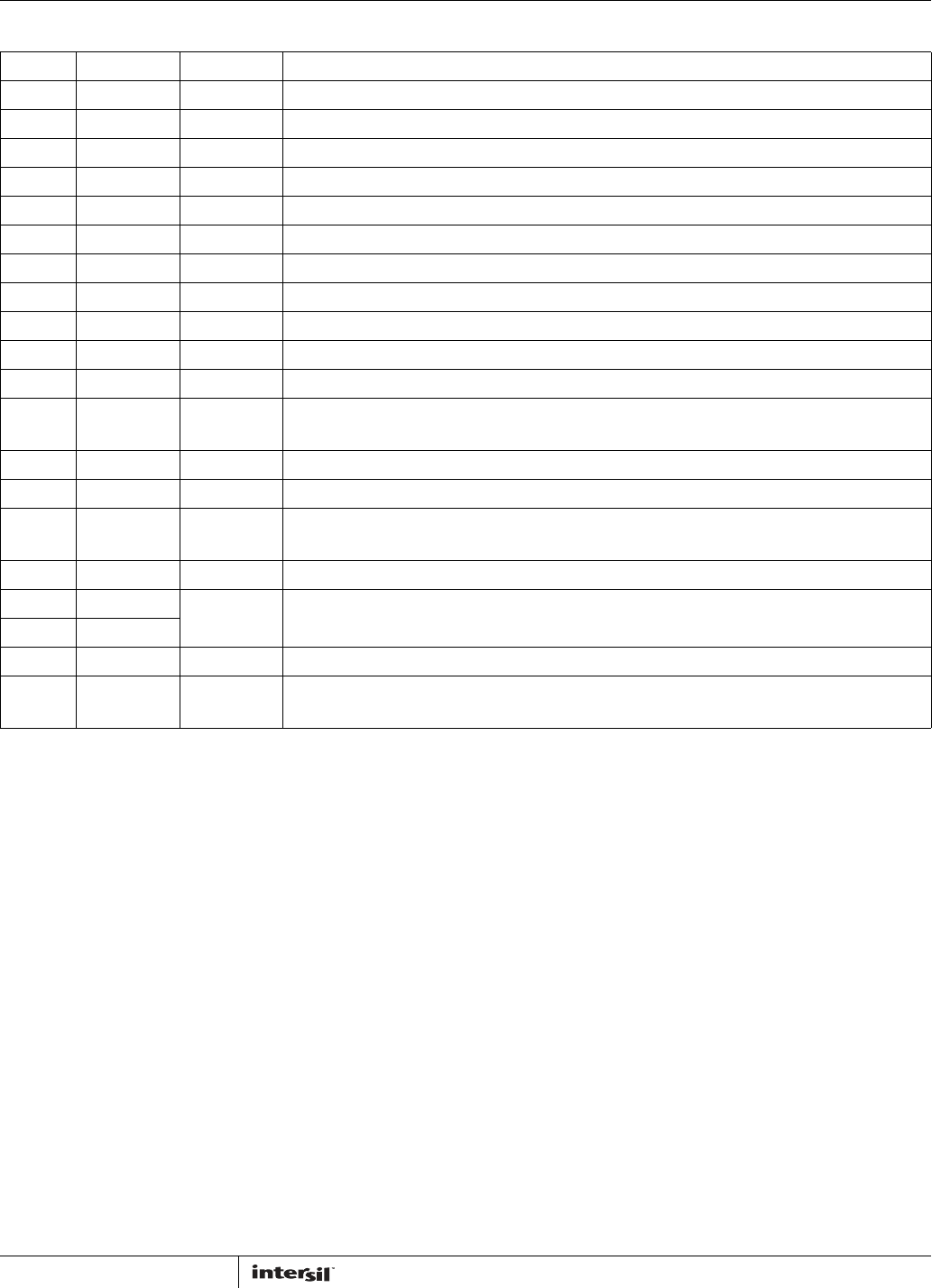

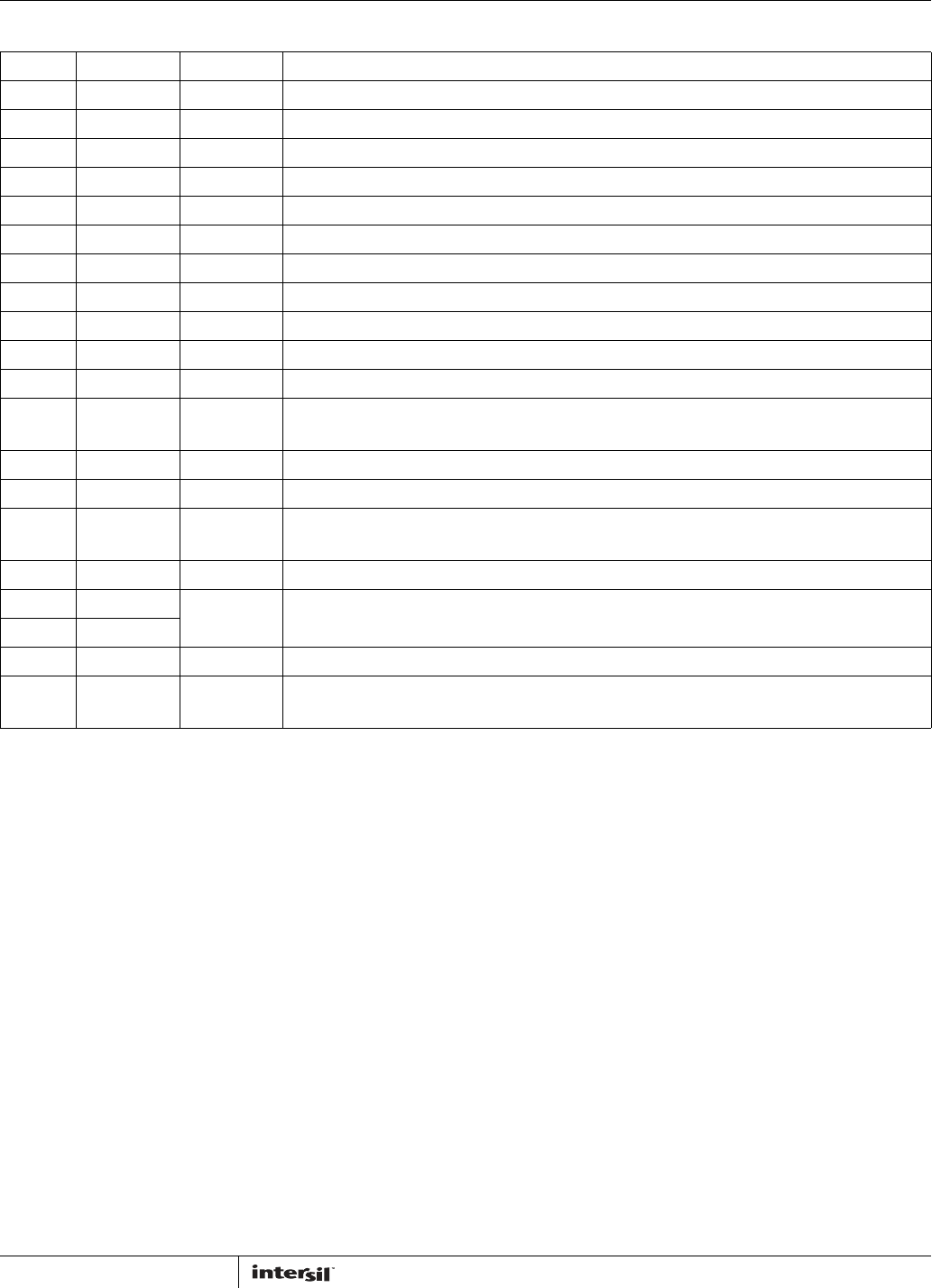

18 VSEN I Output voltage feedback. Connect to output regulation point.

19 ISENB I Differential voltage input for current limit.

20 ISENA I Differential voltage input for current limit. High voltage tolerant.

21 VR PWR Internal 5V reference used to power internal drivers.

22 GL O Low side FET gate drive.

23 PGND PWR Power ground. Connect to low impedance ground plane.

24 SW PWR Drive train switch node.

25 GH O High-side FET gate drive.

26 BST PWR High-side drive boost voltage.

27 VDD

3

PWR Supply voltage.

28 V25 PWR Internal 2.5 V reference used to power internal circuitry.

29 XTEMP I

External temperature sensor input. Connect to external 2N3904 diode connected

transistor.

30 VADJ I Output voltage setting pin (POLA/DOSA mapping)

31 MGN I Digital V

OUT

margin control

32 CFG I

Configuration pin. Used to control the switching phase offset, sequencing and

other management features.

33 EN I Enable. Active signal enables PWM switching.

34 DLY0

I, M

Softstart delay select. Sets the delay from when EN is asserted until the output

voltage starts to ramp.

35 DLY1

36 PG O Power good output.

ePad SGND PWR

Exposed thermal pad. Connect to low impedance ground plane. Internal

connection to SGND.

Table 4. Pin Descriptions (Continued)

Pin Label

Type

1

Description

NOTES:

1. I = Input, O = Output, PWR = Power or Ground, M = Multi-mode pin (refer to Section 4.5, “Multi-mode Pins,” )

2. The SYNC pin can be used as a logic pin, a clock input or a clock output.

3. V

DD

is measured internally and the value is used to modify the PWM loop gain.

ZL2005P