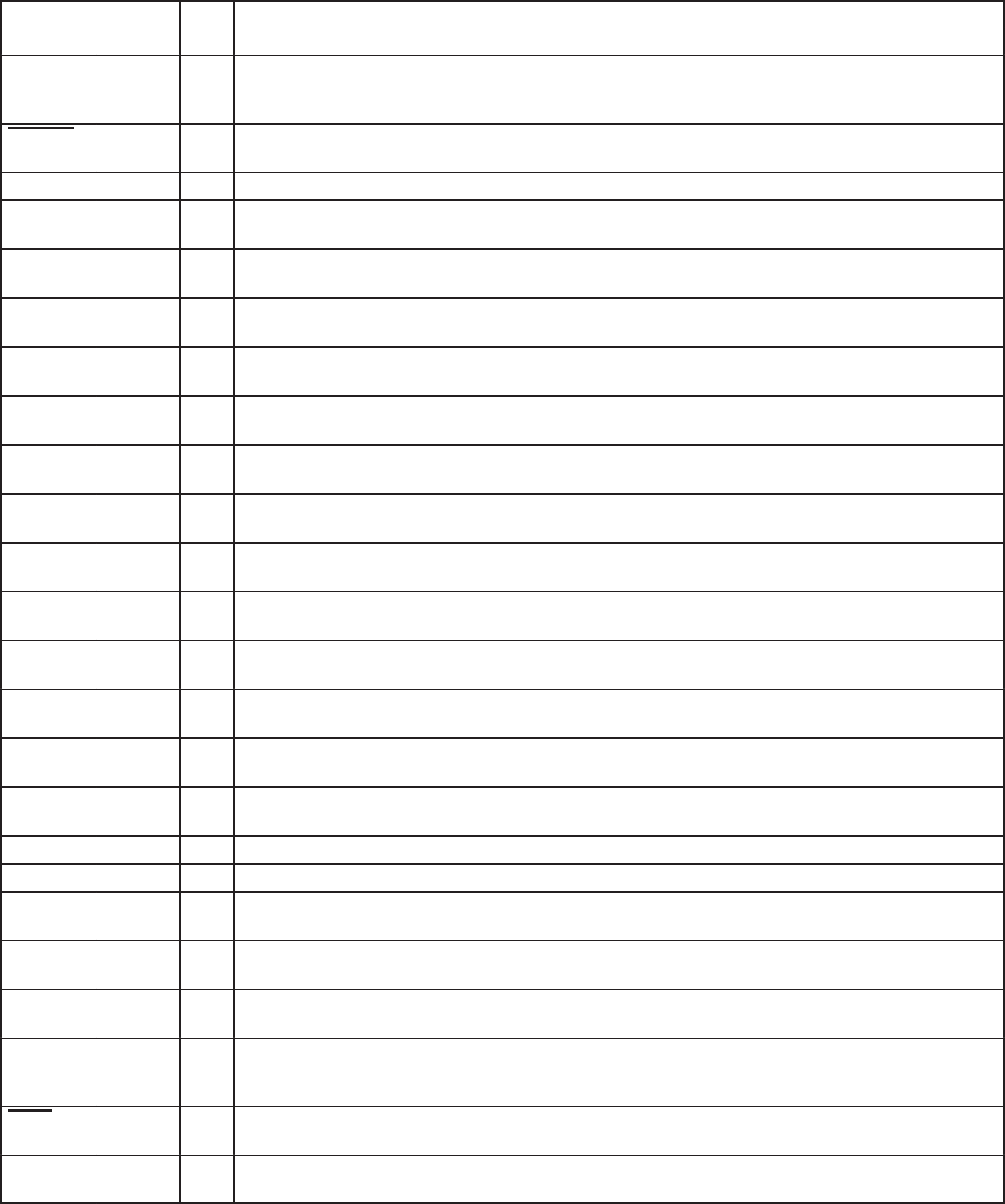

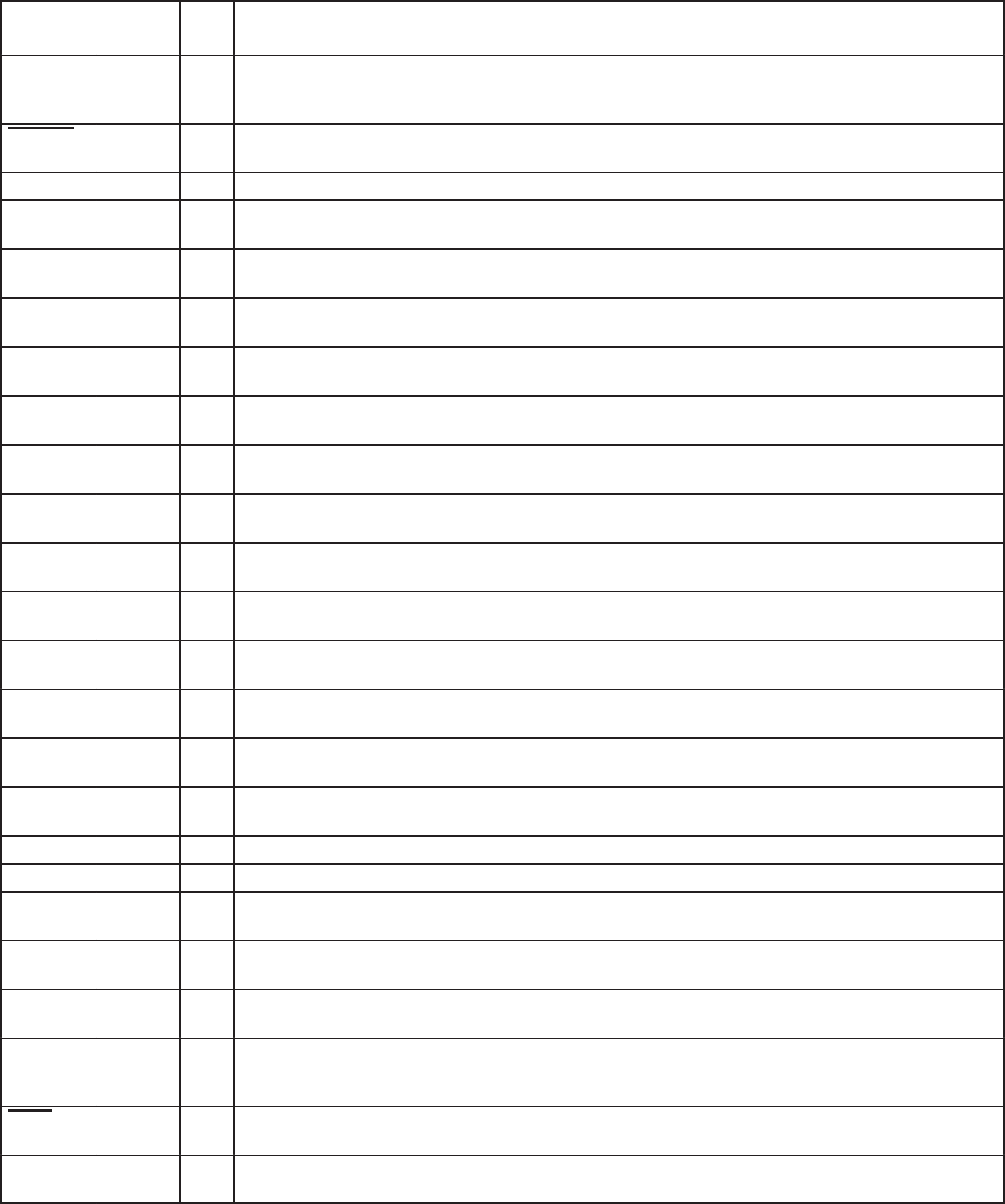

1–6

1.6 Terminal Functions – Normal Mode (Continued)

TERMINAL

NAME NO.

MCLKO2 45 O Master clock output 2:An output that can be used as the master clock for the CODEC port interface and the

CODEC. This clock signal can also be used as a miscellaneous clock. This signal uses a 3.3-V TTL/LVCMOS

output buffer.

MRESET 10 I Master reset: An active low asynchronous reset for the device that resets all logic to the default state. This

signal uses a 3.3-V TTL/LVCMOS input buffer.

Not Used 22 I This pin is not used in the normal mode. This signal should be tied to digital ground for normal operation.

P1.0 24 I/O General-purpose I/O port 1 bit 0: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P1.1 25 I/O General-purpose I/O port 1 bit 1: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P1.2 26 I/O General-purpose I/O port 1 bit 2: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P1.3 28 I/O General-purpose I/O port 1 bit 3: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P1.4 29 I/O General-purpose I/O port 1 bit 4: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P1.5 30 I/O General-purpose I/O port 1 bit 5: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P1.6 31 I/O General-purpose I/O port 1 bit 6: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P1.7 32 I/O General-purpose I/O port 1 bit 7: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P3.0 14 I/O General-purpose I/O port 3 bit 0: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P3.1 15 I/O General-purpose I/O port 3 bit 1: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P3.3 18 I/O General-purpose I/O port 3 bit 3: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P3.4 19 I/O General-purpose I/O port 3 bit 4: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

P3.5 20 I/O General-purpose I/O port 3 bit 5: A bidirectional I/O port. This signal uses a 5-V compatible TTL/LVCMOS

input/output buffer with an internal 100 µA active pullup.

PLLFILI 52 I PLL loop filter input: Input to on-chip PLL from external filter components.

PLLFILO 1 O PLL loop filter output: Output from on-chip PLL to external filter components.

PLLO 4 O PLL output: The 48-MHz output of the PLL used for diagnostic purposes only. This signal uses a 3.3-V

TTL/LVCMOS output buffer.

PLLOEN 23 I PLL output enable: An input used to enable the PLLO output signal. This signal uses a 5-V compatible input

buffer.

PWMO 3 O PWM output: Output of the pulse width modulation circuit. This signal uses a 3.3-V to 5-V CMOS level shifting

output buffer.

PUR 6 O USB data signal plus pullup resistor connect: PUR is used to connect the pullup resistor on the DP signal to

3.3-V or a 3-state. When the DP signal is connected to 3.3-V the host PC should detect the connection of the

TUSB3200 device to the universal serial bus. This signal uses a 3.3-V TTL/LVCMOS output buffer.

RSTO 13 O Reset output: Output that is active while the master reset input or the USB reset is active. This signal uses a

3.3-V TTL/LVCMOS output buffer.

SCL 42 O I

2

C interface serial clock: SCL is the clock signal for the I

2

C serial interface. This signal uses a 3.3-V to 5-V TTL

level shifting open drain output buffer.