A–38

A.5.5.4 I

2

C Interface Control and status register (I2CCTL – Address FFC0h)

The I

2

C interface control and status register contains various control and status bits used for the I

2

C interface

operation.

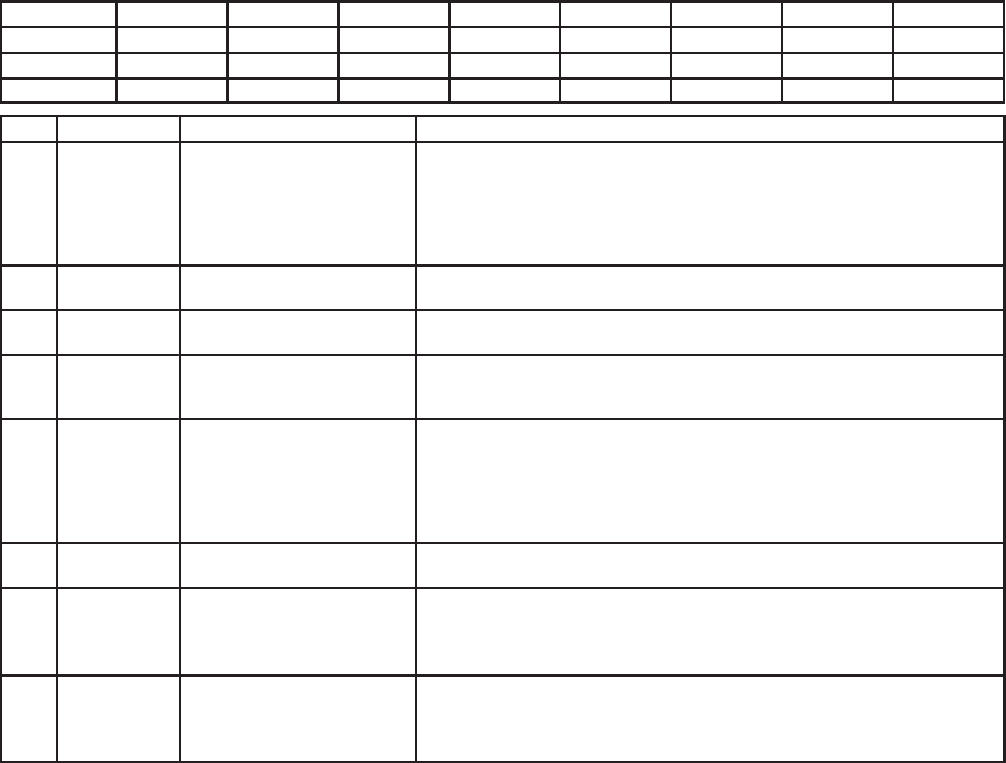

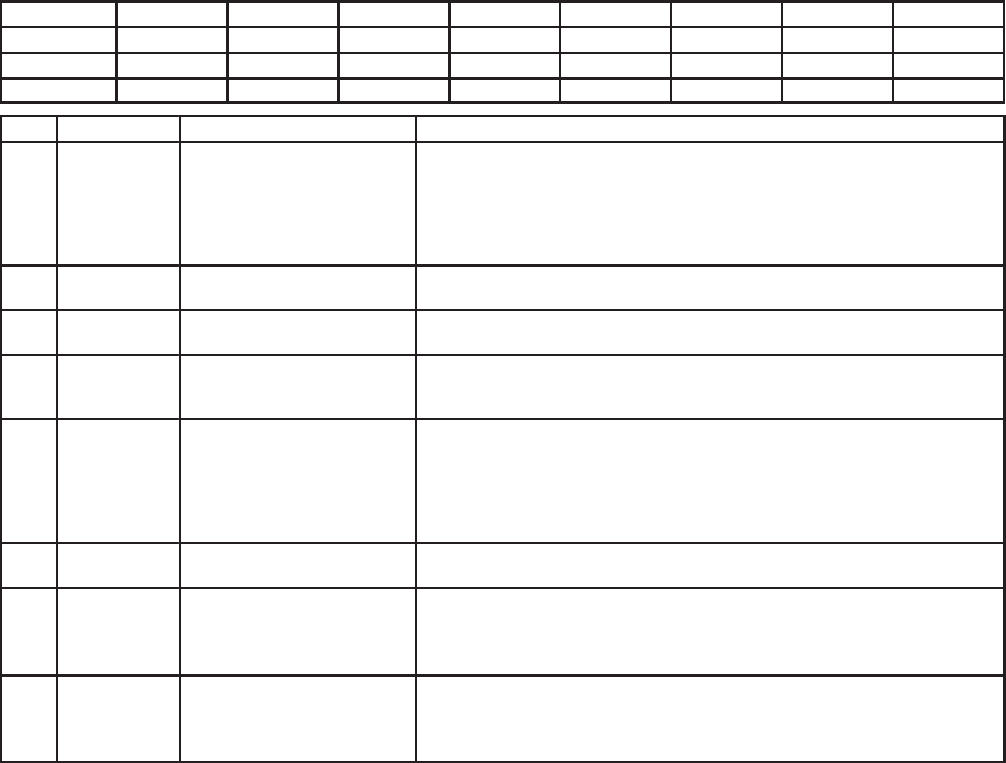

Bit 7 6 5 4 3 2 1 0

Mnemonic RXF RXIE ERR FRQ TXE TXIE STPRD STPWR

Type R R/W R/W R/W R R/W R/W R/W

Default 0 0 0 0 0 0 0 0

BIT MNEMONIC NAME DESCRIPTION

7 RXF Receive data register full The receive data register full bit is set to a 1 by hardware when a new data byte has

been received into the receive data register from the slave device. This bit is read

only and is cleared to a 0 by hardware when the MCU reads the new byte from the

receive data register. Note that when the MCU writes to the interrupt vector register,

the I

2

C receive data register full interrupt will be cleared but this status bit will not be

cleared at that time.

6 RXIE Receive interrupt enable The receive interrupt enable bit is set to a 1 by the MCU to enable the I

2

C receive

data register full interrupt.

5 ERR Error condition The error condition bit is set to a 1 by hardware when the slave device does not

respond. This bit is read/write and can only be cleared by the MCU.

4 FRQ Frequency select The frequency select bit is used by the MCU to program the I

2

C serial clock (SCL)

output signal frequency. A value of 0 sets the SCL frequency to 100 kHz and a value

of 1 sets the SCL frequency to 400 kHz.

3 TXE Transmit data register empty The transmit data register empty bit is set to a 1 by hardware when the data byte in

the transmit data register has been sent to the slave device. This bit is read only and

is cleared to a 0 by hardware when a new data byte is written to the transmit data

register by the MCU. Note that when the MCU writes to the interrupt vector register,

the I

2

C transmit data register empty interrupt will be cleared but this status bit will not

be cleared at that time.

2 TXIE Transmit interrupt enable The transmit interrupt enable bit is set to a 1 by the MCU to enable the I

2

C transmit

data register empty interrupt.

1 STPRD Stop – read transaction The stop read transaction bit is set to a 1 by the MCU to enable the hardware to

generate a stop condition on the I

2

C bus after the next data byte from the slave

device is received into the receive data register. The MCU should clear this bit to a 0

after the read transaction has concluded.

0 STPWR Stop – write transaction The stop write transaction bit is set to a 1 by the MCU to enable the hardware to

generate a stop condition on the I

2

C bus after the data byte in the transmit data

register is sent to the slave device. The MCU should clear this bit to a 0 after the write

transaction has concluded.