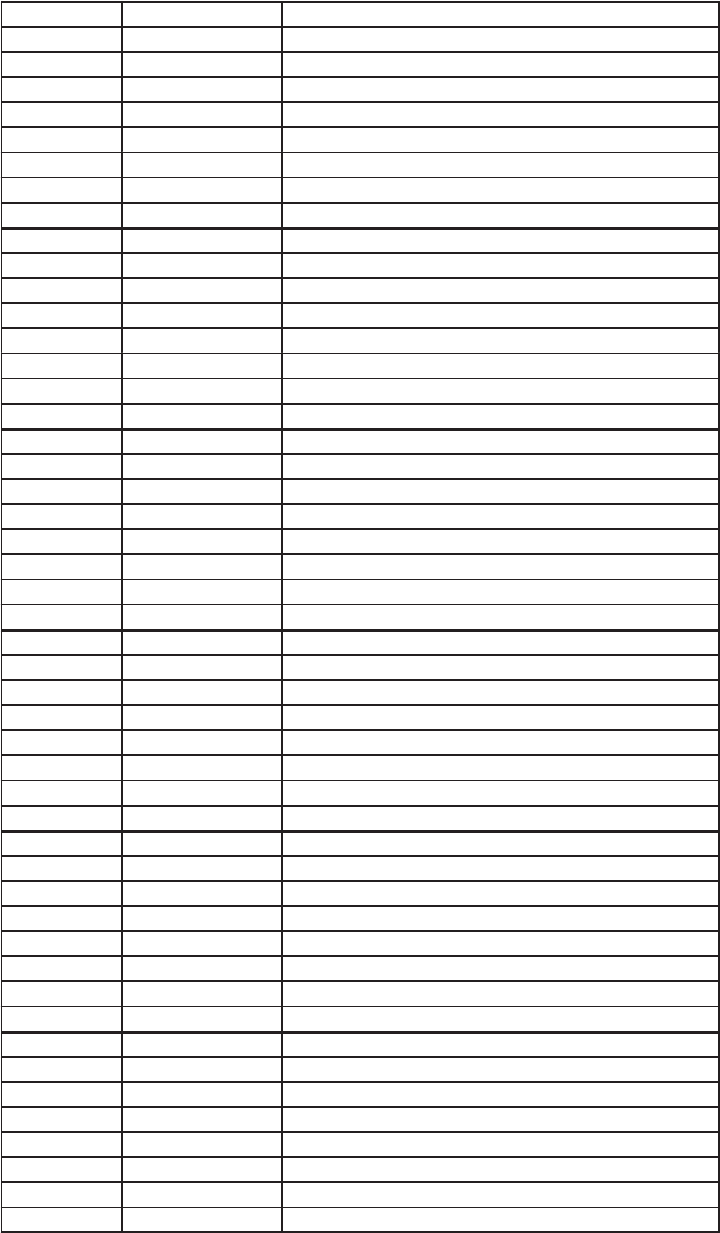

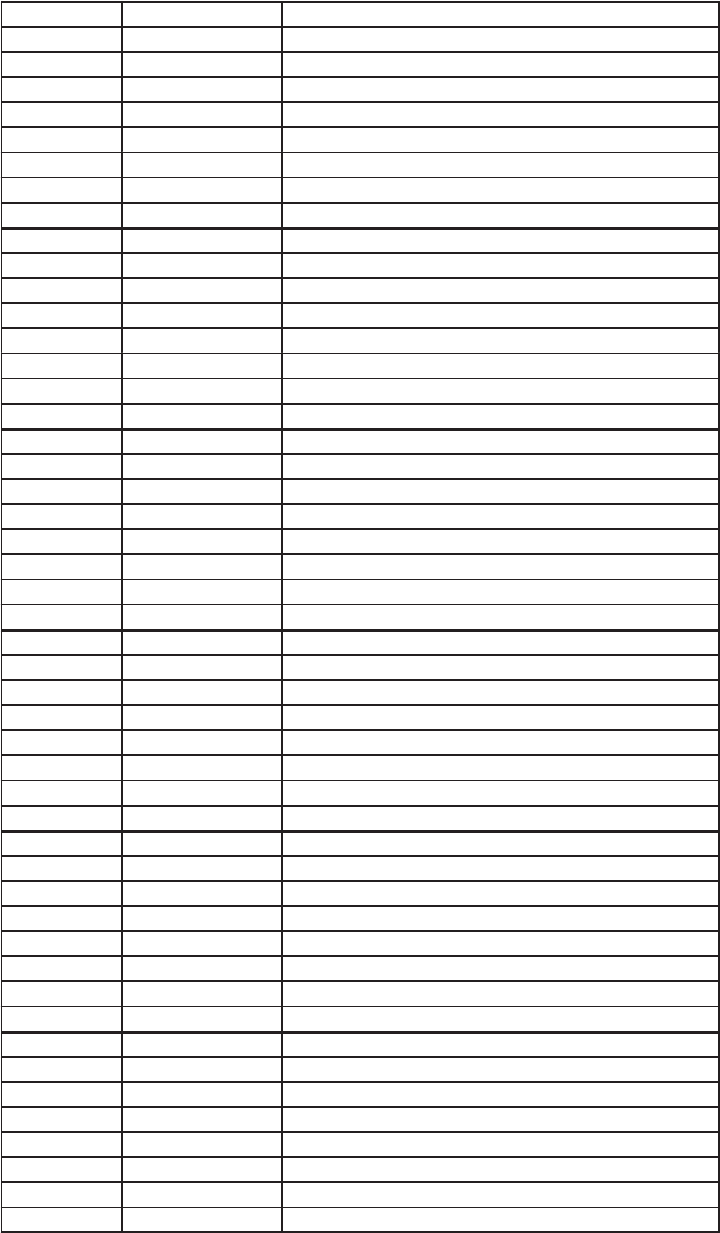

A–6

Table A–1. USB Endpoint Configuration Blocks Address Map (Continued)

ADDRESS MNEMONIC NAME

FF7Fh OEPDCNTY6 Out endpoint 6 - Y buffer data count byte

FF7Eh Reserved Reserved for future use.

FF7Dh OEPBBAY6 Out endpoint 6 - Y buffer base address byte

FF7Ch Reserved Reserved for future use.

FF7Bh OEPDCNTX6 Out endpoint 6 - X buffer data count byte

FF7Ah OEPBSIZ6 Out endpoint 6 - X and Y buffer size byte

FF79h OEPBBAX6 Out endpoint 6 - X buffer base address byte

FF78h OEPCNF6 Out endpoint 6 – configuration byte

FF77h OEPDCNTY7 Out endpoint 7 - Y buffer data count byte

FF76h Reserved Reserved for future use.

FF75h OEPBBAY7 Out endpoint 7 - Y buffer base address byte

FF74h Reserved Reserved for future use.

FF73h OEPDCNTX7 Out endpoint 7 - X buffer data count byte

FF72h OEPBSIZ7 Out endpoint 7 - X and Y buffer size byte

FF71h OEPBBAX7 Out endpoint 7 - X buffer base address byte

FF70h OEPCNF7 Out endpoint 7 – configuration byte

FF6Fh IEPDCNTY0 In endpoint 0 - Y buffer data count byte

FF6Eh Reserved Reserved for future use.

FF6Dh IEPBBAY0 In endpoint 0 - Y buffer base address byte

FF6Ch Reserved Reserved for future use.

FF6Bh IEPDCNTX0 In endpoint 0 - X buffer data count byte

FF6Ah IEPBSIZ0 In endpoint 0 - X and Y buffer size byte

FF69h IEPBBAX0 In endpoint 0 - X buffer base address byte

FF68h IEPCNF0 In endpoint 0 – configuration byte

FF67h IEPDCNTY1 In endpoint 1 - Y buffer data count byte

FF66h Reserved Reserved for future use.

FF65h IEPBBAY1 In endpoint 1 - Y buffer base address byte

FF64h Reserved Reserved for future use.

FF63h IEPDCNTX1 In endpoint 1 - X buffer data count byte

FF62h IEPBSIZ1 In endpoint 1 - X and Y buffer size byte

FF61h IEPBBAX1 In endpoint 1 - X buffer base address byte

FF60h IEPCNF1 In endpoint 1 – configuration byte

FF5Fh IEPDCNTY2 In endpoint 2 - Y buffer data count byte

FF5Eh Reserved Reserved for future use.

FF5Dh IEPBBAY2 In endpoint 2 - Y buffer base address byte

FF5Ch Reserved Reserved for future use.

FF5Bh IEPDCNTX2 In endpoint 2 - X buffer data count byte

FF5Ah IEPBSIZ2 In eEndpoint 2 - X and Y buffer size byte

FF59h IEPBBAX2 In endpoint 2 - X buffer base address byte

FF58h IEPCNF2 In endpoint 2 – configuration byte

FF57h IEPDCNTY3 In endpoint 3 - Y buffer data count byte

FF56h Reserved Reserved for future use.

FF55h IEPBBAY3 In endpoint 3 - Y buffer base address byte

FF54h Reserved Reserved for future use.

FF53h IEPDCNTX3 In endpoint 3 - X buffer data count byte

FF52h IEPBSIZ3 In endpoint 3 - X and Y buffer size byte

FF51h IEPBBAX3 In endpoint 3 - X buffer base address byte

FF50h IEPCNF3 In endpoint 3 – configuration byte