3–5

3.4.4 CODEC Port Interface Signals (I

2

S Modes) Over Recommended Operating Conditions

(unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

f

SCLK

Frequency, SCLK C

L

= 50 pF (32)F

S

(64)F

S

MHz

t

cyc

Cycle time, SCLK C

L

= 50 pF, See Note 1 1/(64)F

S

1/(32)F

S

ns

t

pd

Propagation delay, SCLK falling edge to LRCLK and SDOUT C

L

= 50 pF 15 ns

t

su

Setup time, SDIN to SCLK rising edge 10 ns

t

h

Hold time, SDIN from SCLK rising edge 10 ns

NOTE 1: Worst case duty cycle is 45/55.

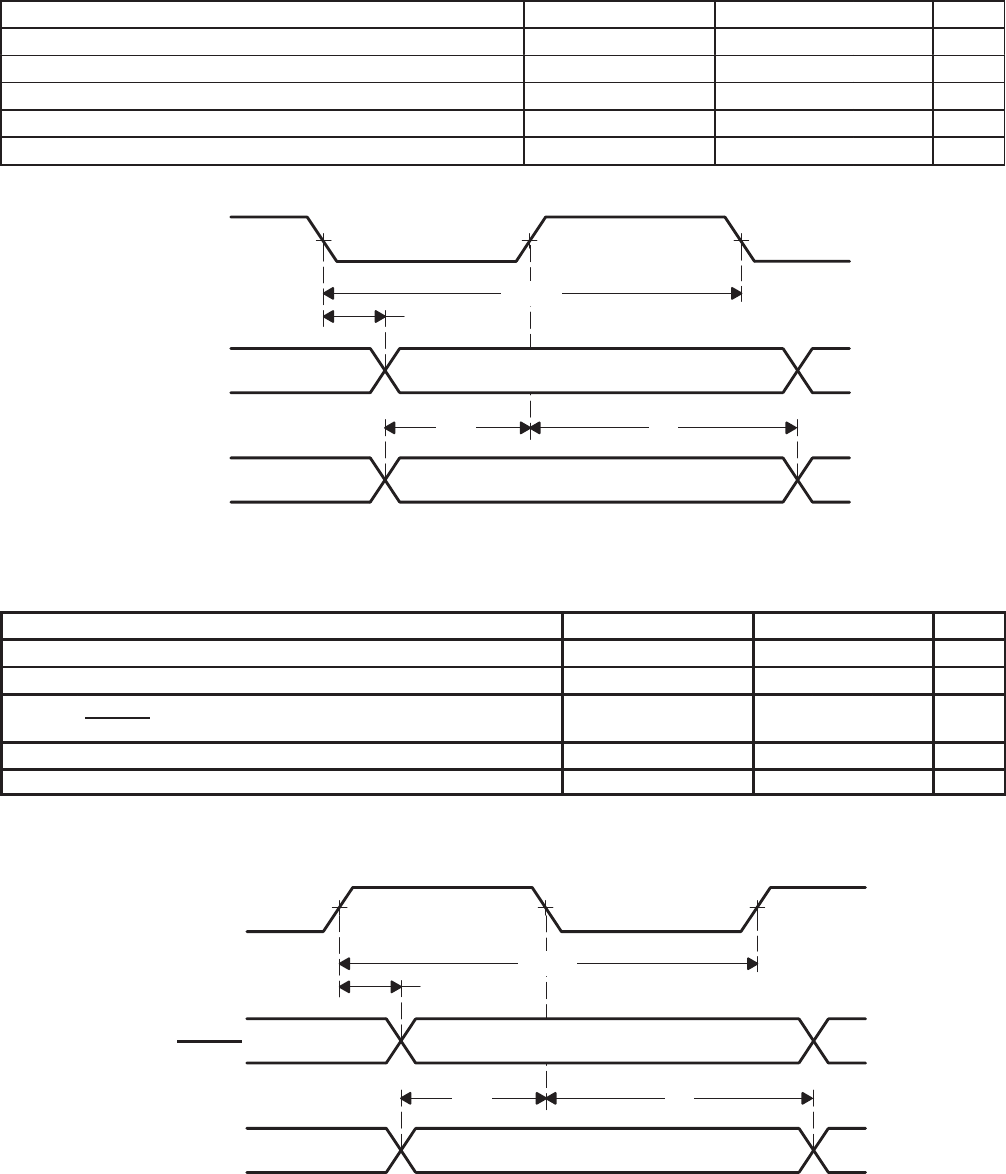

t

su

t

h

SCLK

LRCLK, SD_OUT

SD_IN

t

pd

t

cyc

Figure 3–5. I

2

S Mode Timing Waveforms

3.4.5 CODEC Port Interface Signals (General Purpose Mode) Over Recommended Operating

Conditions (unless otherwise noted)

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

f

CSCLK

Frequency, CSCLK C

L

= 50 pF 0.125 25 MHz

t

cyc

Cycle time, CSCLK C

L

= 50 pF, See Note 2 0.040 8 µs

t

pd

Propagation delay, CSCLK to CSYNC, CDATO, CSCHNE and

CRESET

C

L

= 50 pF 15 ns

t

su

Setup time, CDATI to CSCLK 10 ns

t

h

Hold time, CDATI from CSCLK 10 ns

NOTE 2: The timing waveforms in Figure 3-6 show the CSYNC, CDATO, CSCHNE and CRESET signals generated with the rising edge of the

clock and the CDATI signal sampled with the falling edge of the clock. The edge of the clock used is programmable. However, the timing

characteristics are the same regardless of which edge of the clock is used.

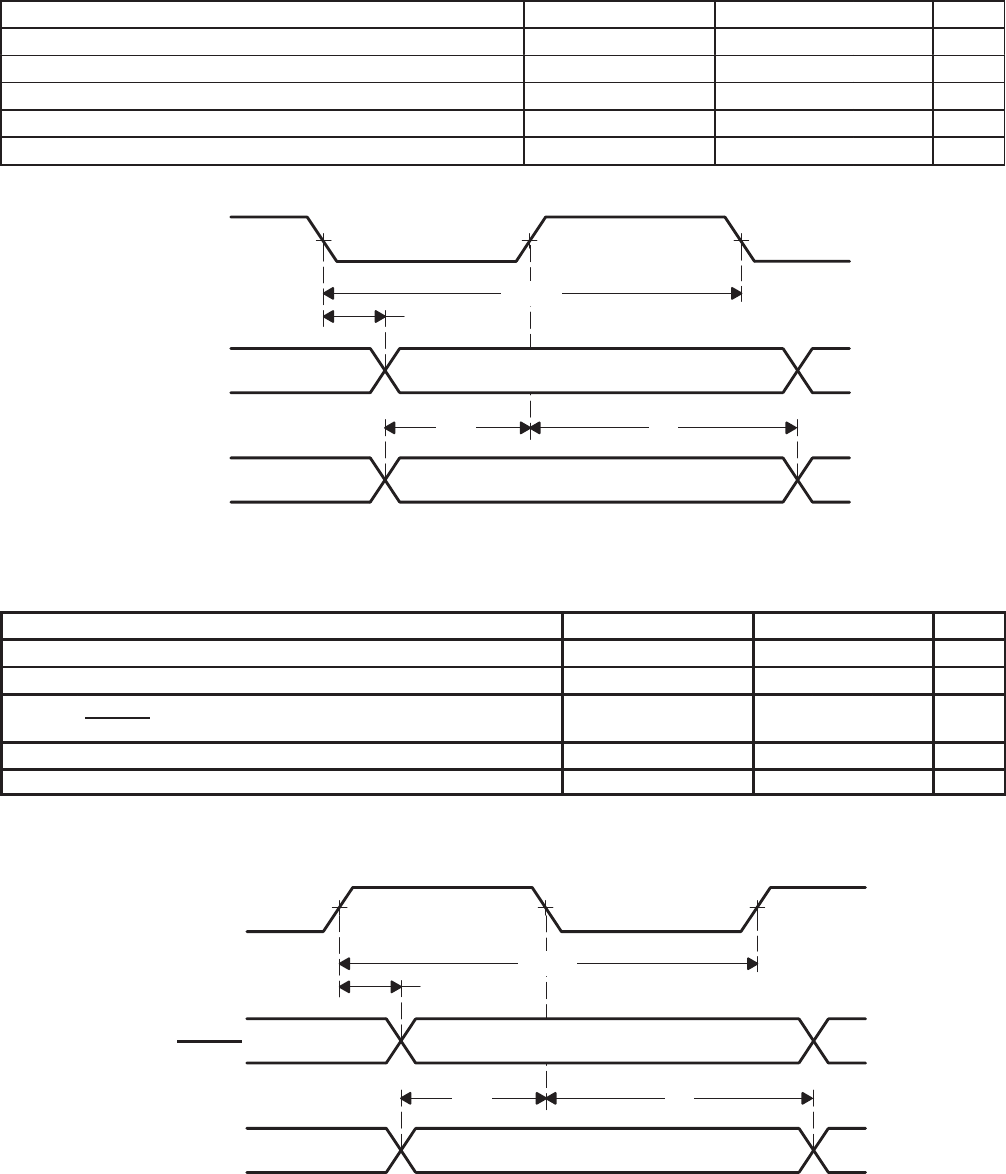

t

su

t

h

CSCLK

CSYNC, CDATO,

CSCHNE, CRESET

CDATI

t

pd

t

cyc

Figure 3–6. General-Purpose Mode Timing Waveforms