3−12

3.17 Power Management Capabilities Register

The power management capabilities register indicates the capabilities of the TSB12LV26 device related to PCI power

management. See Table 3−14 for a complete description of the register contents.

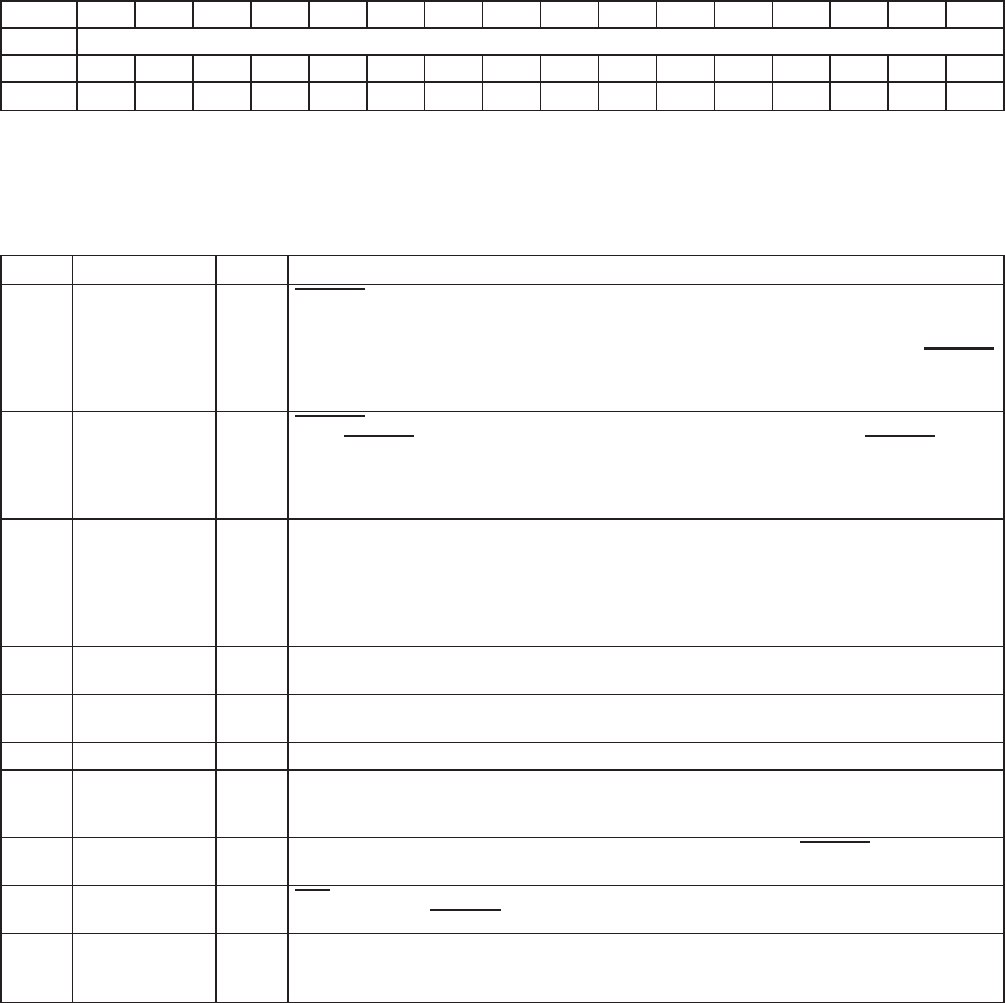

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name Power management capabilities

Type RU RU RU RU RU RU R R R R R R R R R R

Default 0 1 1 0 0 1 0 0 0 0 0 0 0 0 0 1

Register: Power management capabilities

Type: Read/Update, Read-only

Offset: 46h

Default: 6401h

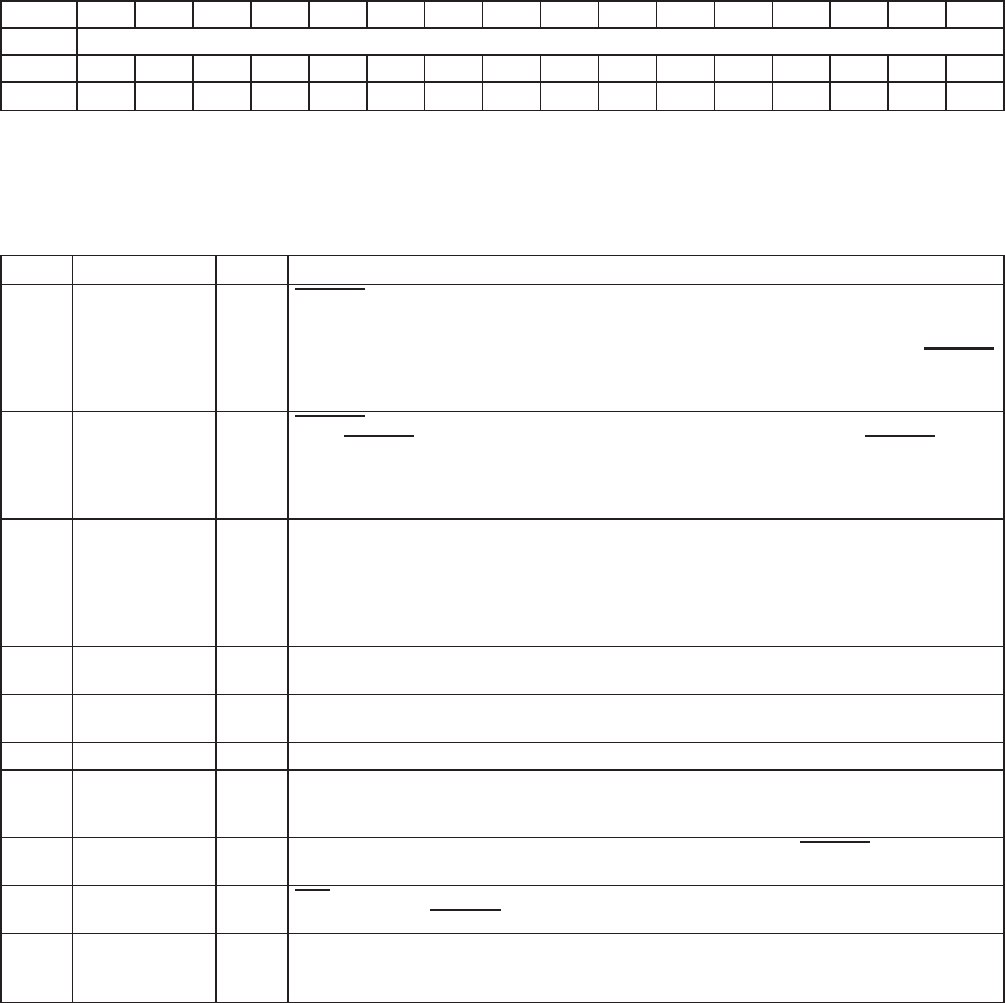

Table 3−14. Power Management Capabilities Register Description

BIT FIELD NAME TYPE DESCRIPTION

15 PME_D3COLD RU PCI_PME support from D3

cold

. This bit can be set to 1 or cleared to 0 via bit 15 (PME_D3COLD) in

the miscellaneous configuration register at offset F0h in the PCI configuration space (see Section 3.20,

Miscellaneous Configuration Register). The miscellaneous configuration register is loaded from ROM.

When this bit is set to 1, it indicates that the TSB12LV26 device is capable of generating a PCI_PME

wake event from D3

cold

. This bit state is dependent upon the TSB12LV26 V

AUX

implementation and

may be configured by using bit 15 (PME_D3COLD) in the miscellaneous configuration register.

14−11 PME_SUPPORT RU PCI_PME support. This 4-bit field indicates the power states from which the TSB12LV26 device may

assert PCI_PME

. This field returns a value of 1100b by default, indicating that PCI_PME may be

asserted from the D3

hot

and D2 power states. Bit 13 may be modified by host software using bit 13

(PME_SUPPORT_D2) in the miscellaneous configuration register at offset F0h in the PCI

configuration space (see Section 3.20, Miscellaneous Configuration Register).

10 D2_SUPPORT RU D2 support. This bit can be set or cleared via bit 10 (D2_SUPPORT) in the miscellaneous configuration

register at offset F0h in the PCI configuration space (see Section 3.20, Miscellaneous Configuration

Register). The miscellaneous configuration register is loaded from serial EEPROM. When this bit is

set to 1, it indicates that D2 support is present. When this bit is cleared, it indicates that D2 support

is not present for backward compatibility with the TSB12LV22 device. For normal operation, this bit is

set to 1.

9 D1_SUPPORT R D1 support. Bit 9 returns a 0 when read, indicating that the TSB12LV26 device does not support the

D1 power state.

8 DYN_DATA R Dynamic data support. Bit 8 returns a 0 when read, indicating that the TSB12LV26 device does not

report dynamic power-consumption data.

7−6 RSVD R Reserved. Bits 7 and 6 return 0s when read.

5 DSI R Device-specific initialization. Bit 5 returns 0 when read, indicating that the TSB12LV26 device does not

require special initialization beyond the standard PCI configuration header before a generic class

driver is able to use it.

4 AUX_PWR R Auxiliary power source. Since the TSB12LV26 device does not support PCI_PME generation in the

D3

cold

device state, bit 4 returns 0 when read.

3 PME_CLK R PME clock. Bit 3 returns 0 when read, indicating that no host bus clock is required for the TSB12LV26

device to generate PCI_PME

.

2−0 PM_VERSION R Power-management version. This field returns 001b when read, indicating that the TSB12LV26 device

is compatible with the registers described in the PCI Bus Power Management Interface Specification

(Revision 1.0).