4−16

4.19 Isochronous Receive Channel Mask High Register

The isochronous receive channel mask high set/clear register enables packet receives from the upper 32

isochronous data channels. A read from either the set register or clear register returns the content of the isochronous

receive channel mask high register. See Table 4−13 for a complete description of the register contents.

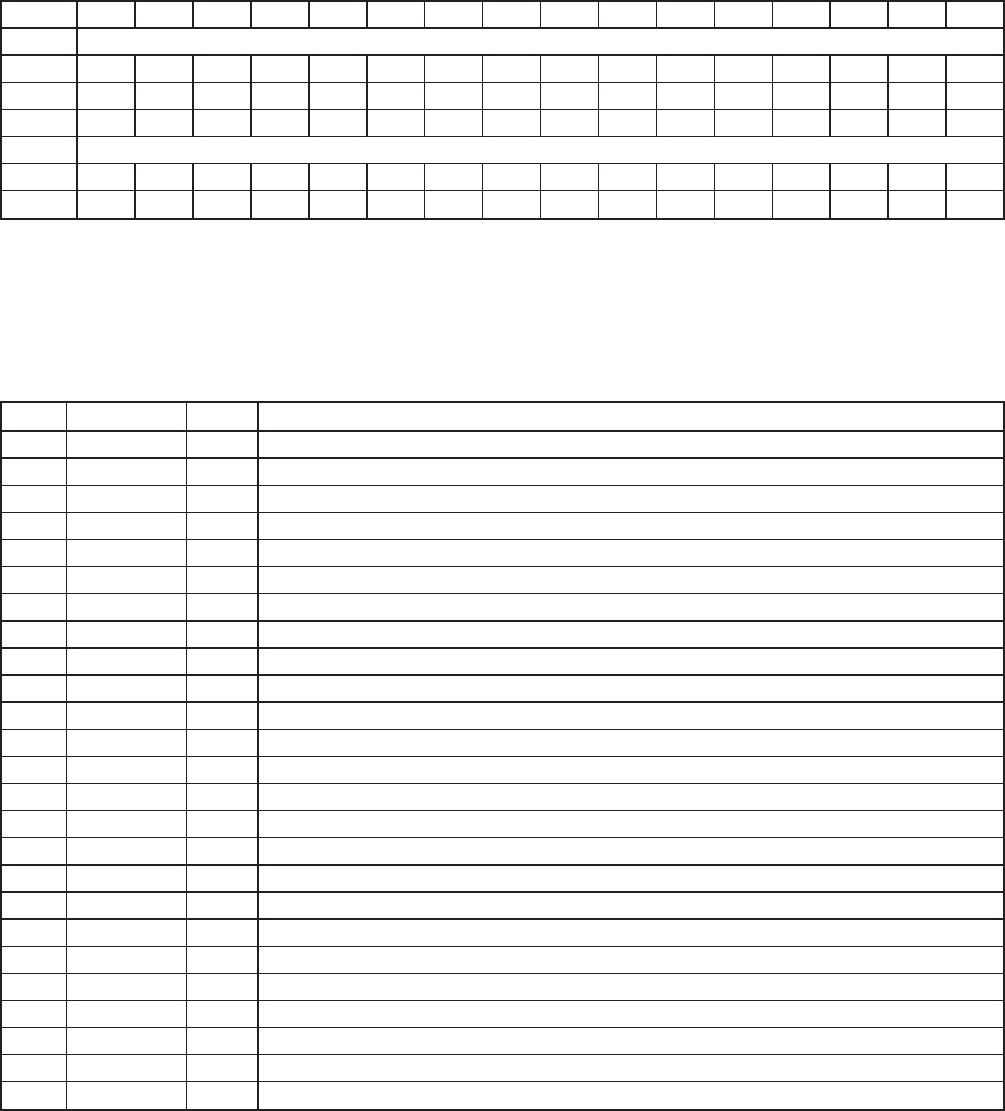

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Name Isochronous receive channel mask high

Type RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC

Default X X X X X X X X X X X X X X X X

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name Isochronous receive channel mask high

Type RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC RSC

Default X X X X X X X X X X X X X X X X

Register: Isochronous receive channel mask high

Type: Read/Set/Clear

Offset: 70h set register

74h clear register

Default: XXXX XXXXh

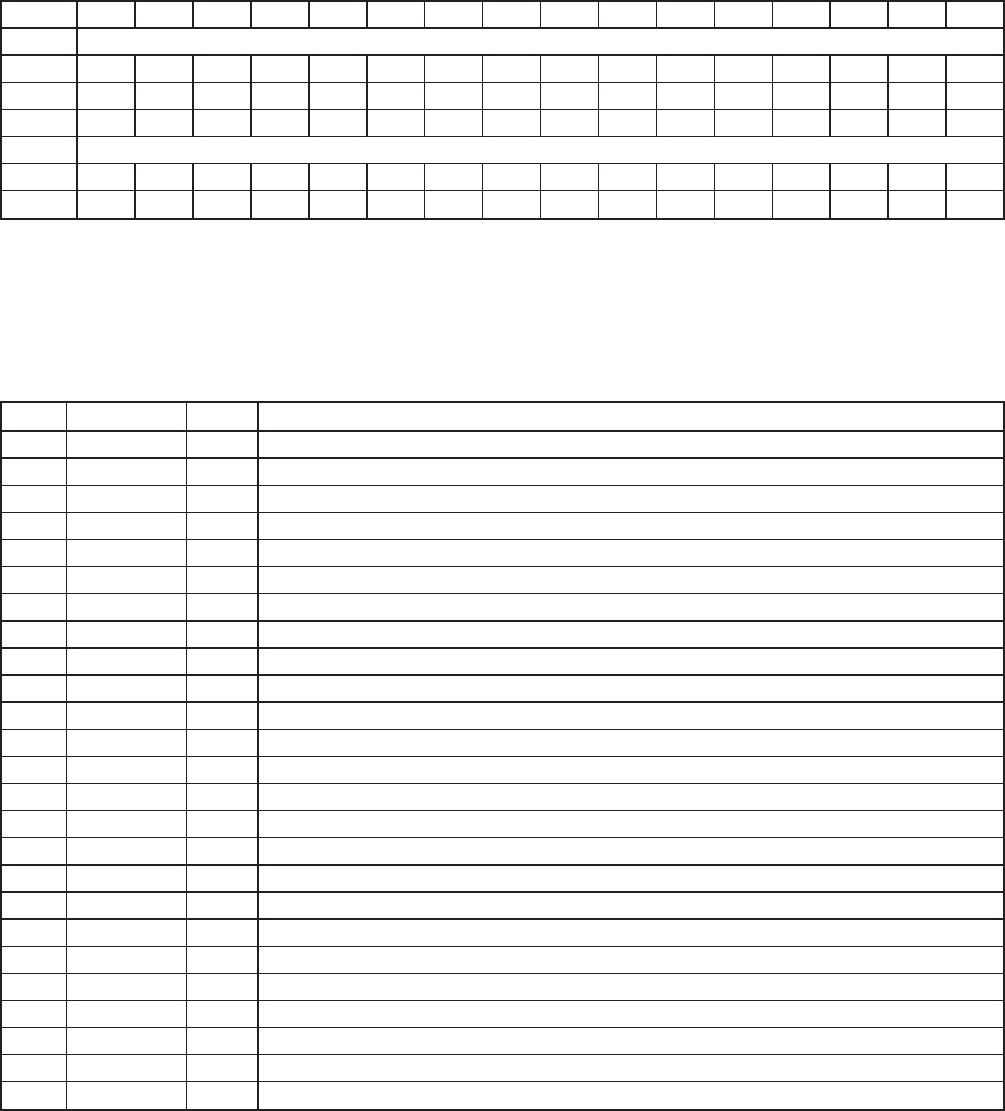

Table 4−13. Isochronous Receive Channel Mask High Register Description

BIT FIELD NAME TYPE DESCRIPTION

31 isoChannel63 RSC When bit 31 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 63.

30 isoChannel62 RSC When bit 30 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 62.

29 isoChannel61 RSC When bit 29 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 61.

28 isoChannel60 RSC When bit 28 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 60.

27 isoChannel59 RSC When bit 27 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 59.

26 isoChannel58 RSC When bit 26 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 58.

25 isoChannel57 RSC When bit 25 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 57.

24 isoChannel56 RSC When bit 24 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 56.

23 isoChannel55 RSC When bit 23 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 55.

22 isoChannel54 RSC When bit 22 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 54.

21 isoChannel53 RSC When bit 21 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 53.

20 isoChannel52 RSC When bit 20 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 52.

19 isoChannel51 RSC When bit 19 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 51.

18 isoChannel50 RSC When bit 18 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 50.

17 isoChannel49 RSC When bit 17 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 49.

16 isoChannel48 RSC When bit 16 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 48.

15 isoChannel47 RSC When bit 15 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 47.

14 isoChannel46 RSC When bit 14 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 46.

13 isoChannel45 RSC When bit 13 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 45.

12 isoChannel44 RSC When bit 12 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 44.

11 isoChannel43 RSC When bit 11 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 43.

10 isoChannel42 RSC When bit 10 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 42.

9 isoChannel41 RSC When bit 9 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 41.

8 isoChannel40 RSC When bit 8 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 40.

7 isoChannel39 RSC When bit 7 is set to 1, the TSB12LV26 device is enabled to receive from isochronous channel number 39.