4−5

4.2 GUID ROM Register

The GUID ROM register accesses the serial EEPROM and is applicable only if bit 24 (GUID_ROM) in the OHCI

version register at OHCI offset 00h (see Section 4.1, OHCI Version Register) is set to 1. See Table 4−3 for a complete

description of the register contents.

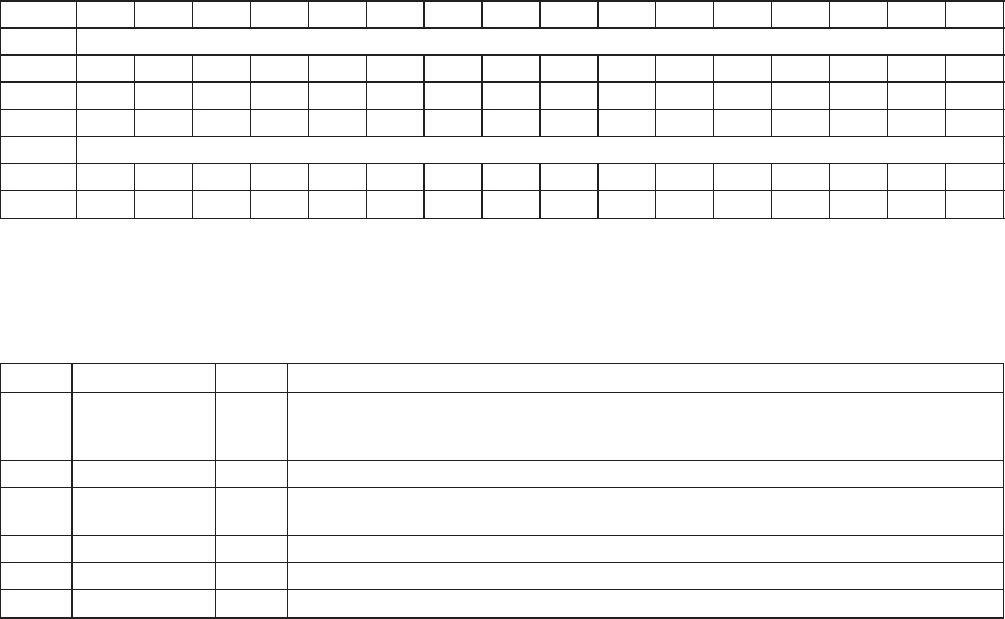

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Name GUID ROM

Type RSU R R R R R RSU R RU RU RU RU RU RU RU RU

Default 0 0 0 0 0 0 0 0 X X X X X X X X

Bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Name GUID ROM

Type R R R R R R R R R R R R R R R R

Default 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Register: GUID ROM

Type: Read/Set/Update, Read/Update, Read-only

Offset: 04h

Default: 00XX 0000h

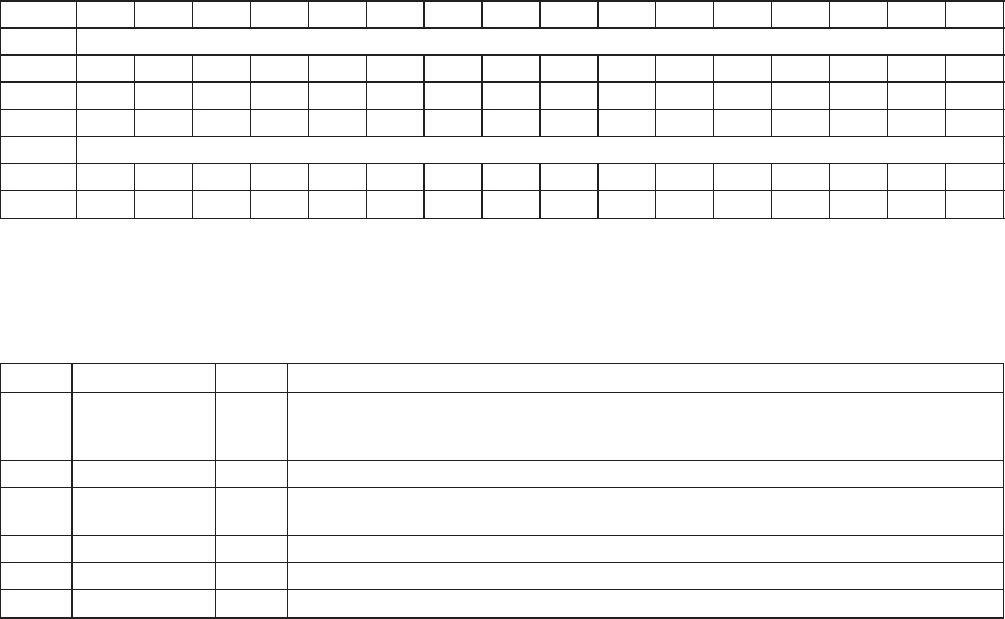

Table 4−3. GUID ROM Register Description

BIT FIELD NAME TYPE DESCRIPTION

31 addrReset RSU Software sets bit 31 to 1 to reset the GUID ROM address to 0. When the TSB12LV26 device completes

the reset, it clears this bit. The TSB12LV26 device does not automatically fill bits 23−16 (rdData field)

with the 0

th

byte.

30−26 RSVD R Reserved. Bits 30−26 return 0s when read.

25 rdStart RSU A read of the currently addressed byte is started when bit 25 is set to 1. This bit is automatically cleared

when the TSB12LV26 device completes the read of the currently addressed GUID ROM byte.

24 RSVD R Reserved. Bit 24 returns 0 when read.

23−16 rdData RU This field contains the data read from the GUID ROM.

15−0 RSVD R Reserved. Bits 15−0 return 0s when read.