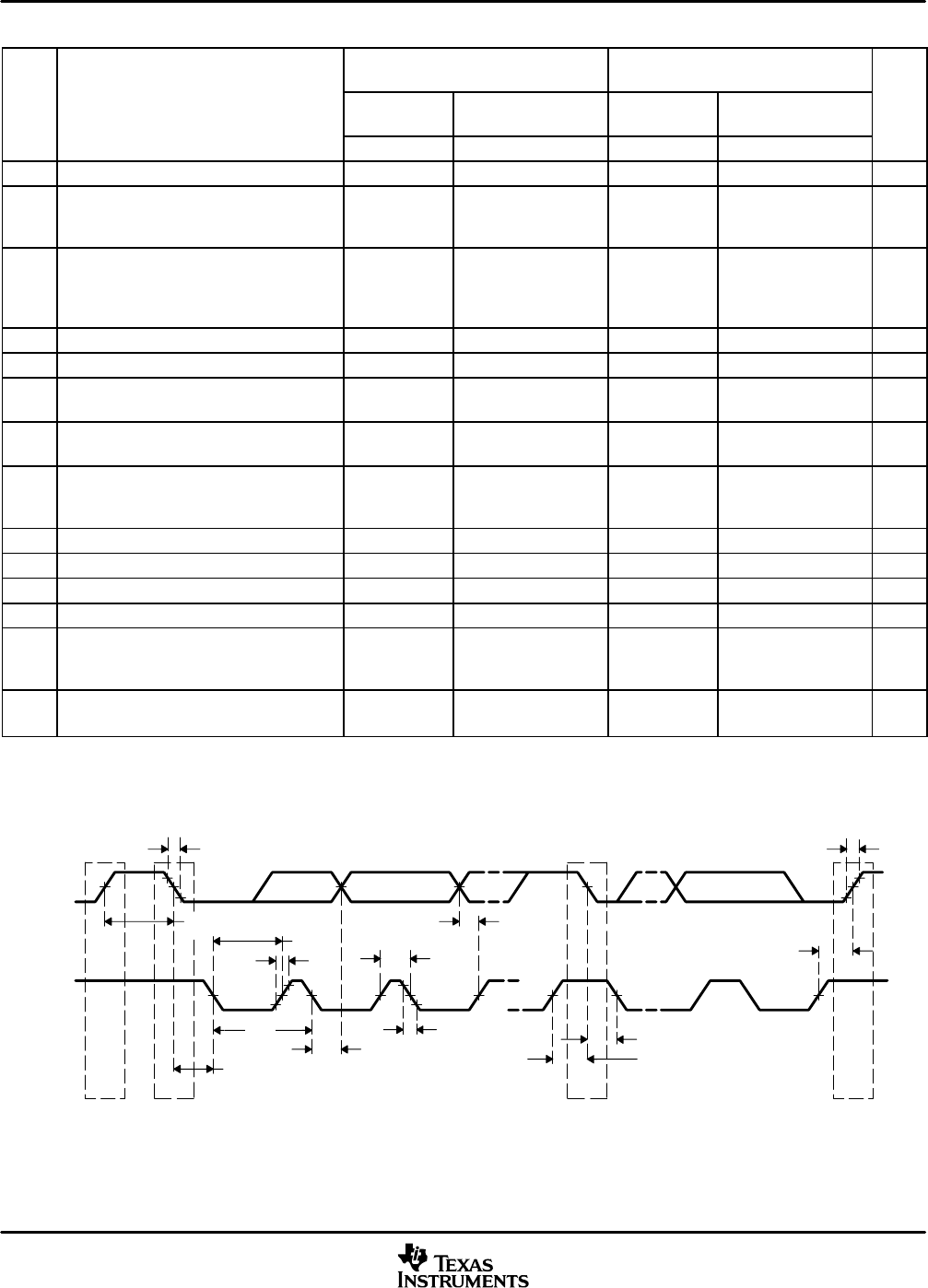

Electrical Specifications

133

November 2002 − Revised January 2005 SPRS205D

Table 5−40. I

2

C Signals (SDA and SCL) Switching Characteristics

CV

DD

= 1.2 V

CV

DD

= 1.35 V

CV

DD

= 1.6 V

NO. PARAMETER

STANDARD

MODE

FAST

MODE

STANDARD

MODE

FAST

MODE

UNIT

MIN MAX MIN MAX MIN MAX MIN MAX

IC16 t

c(SCL)

Cycle time, SCL 10 2.5 10 2.5 µs

IC17 t

d(SCLH-SDAL)

Delay time, SCL high to

SDA low for a repeated

START condition

4.7 0.6 4.7 0.6 µs

IC18 t

d(SDAL-SCLL)

Delay time, SDA low to

SCL low for a START and

a repeated START

condition

4 0.6 4 0.6 µs

IC19 t

w(SCLL)

Pulse duration, SCL low 4.7 1.3 4.7 1.3 µs

IC20 t

w(SCLH)

Pulse duration, SCL high 4 0.6 4 0.6 µs

IC21 t

d(SDA-SCLH)

Delay time, SDA valid to

SCL high

250 100 250 100 ns

IC22 t

v(SCLL-SDAV)

Valid time, SDA valid

after SCL low

0 0 0.9 0 0 0.9 µs

IC23 t

w(SDAH)

Pulse duration, SDA high

between STOP and

START conditions

4.7 1.3 4.7 1.3 µs

IC24 t

r(SDA)

Rise time, SDA 1000 20 + 0.1C

b

†

300 1000 20 + 0.1C

b

†

300 ns

IC25 t

r(SCL)

Rise time, SCL 1000 20 + 0.1C

b

†

300 1000 20 + 0.1C

b

†

300 ns

IC26 t

f(SDA)

Fall time, SDA 300 20 + 0.1C

b

†

300 300 20 + 0.1C

b

†

300 ns

IC27 t

f(SCL)

Fall time, SCL 300 20 + 0.1C

b

†

300 300 20 + 0.1C

b

†

300 ns

IC28 t

d(SCLH-SDAH)

Delay time, SCL high to

SDA high for a STOP

condition

4 0.6 4 0.6 µs

IC29 C

p

Capacitance for each

I

2

C pin

10 10 10 10 pF

†

C

b

= total capacitance of one bus line in pF. If mixed with HS-mode devices, faster fall-times are allowed.

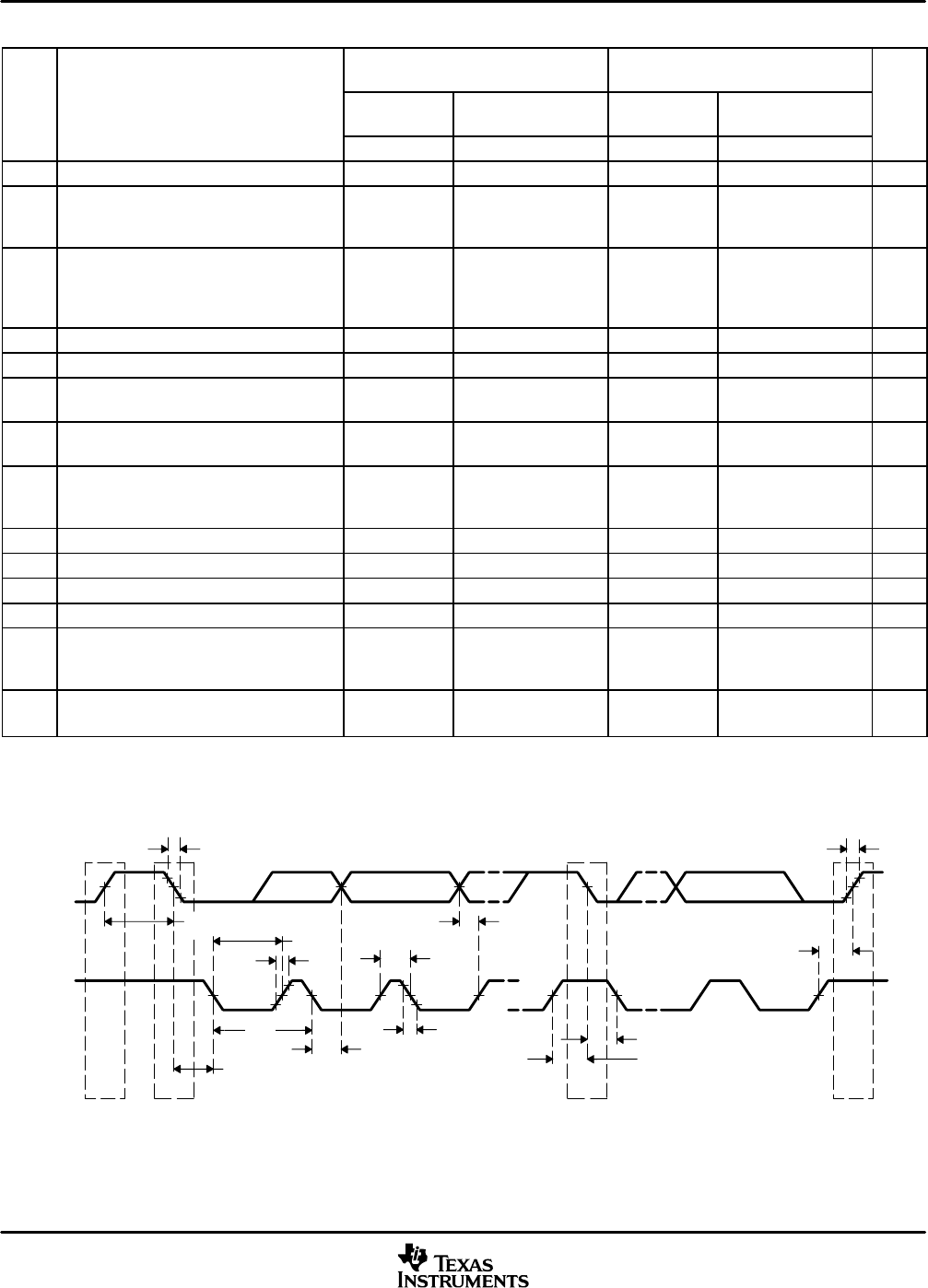

IC25

IC23

IC19

IC18

IC22

IC27

IC20

IC21

IC17

IC18

IC28

Stop Start Repeated

Start

Stop

SDA

SCL

IC16

IC26 IC24

Figure 5−38. I

2

C Transmit Timings