Electrical Specifications

128

November 2002 − Revised January 2005SPRS205D

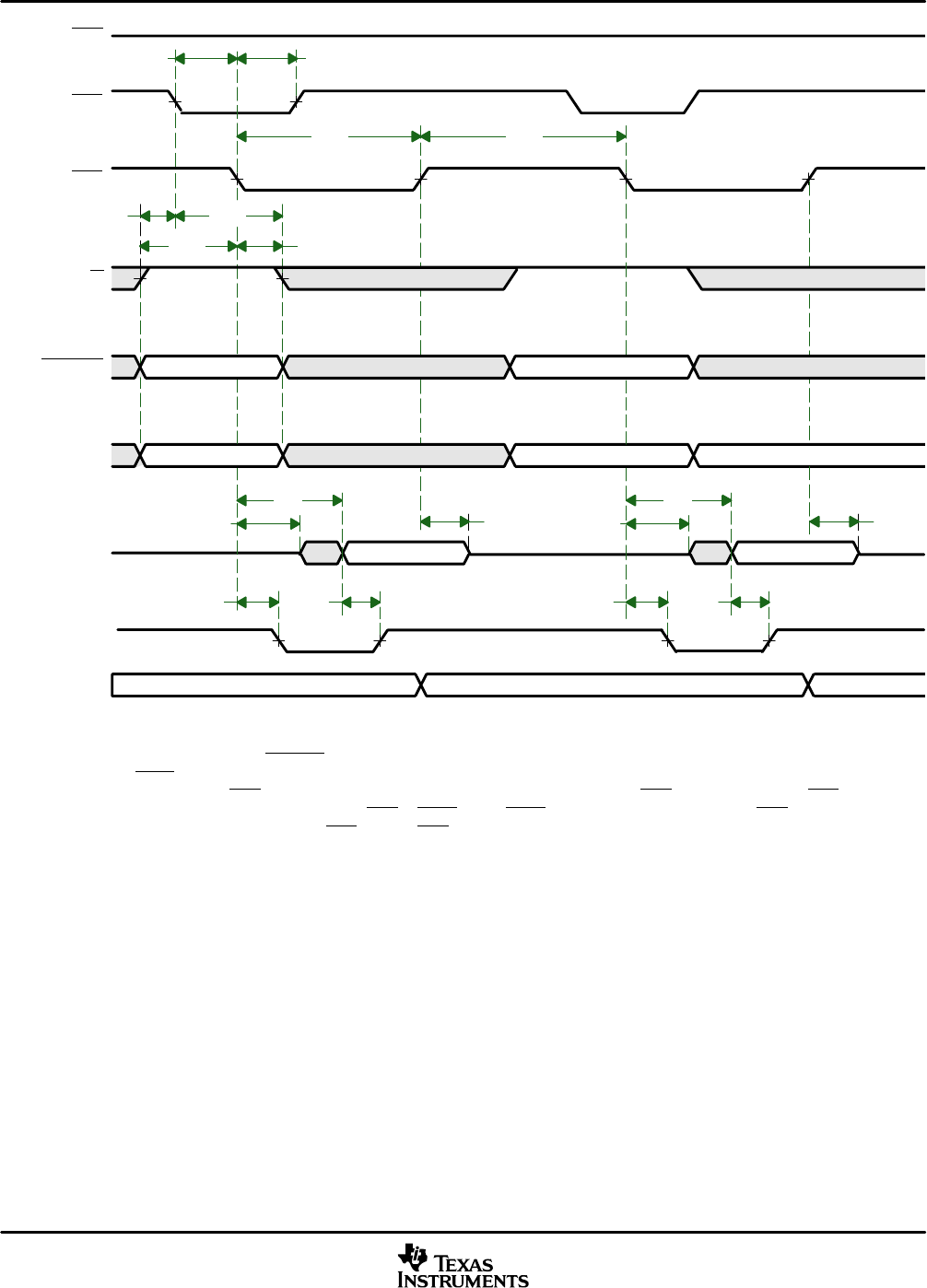

HR/W

Read Data

n

HRDY

HDS

HAS

HCS

HD[15:0]

(read)

PIA contents

n + 1

n + 2

E11 E12

E15 E16

E20

E13

E1

E2

E19

E14

E6

E8E7

Read Data

E1

E2

E6

E8E7

HCNTL[1:0]

Valid (01) Valid (01)

HBE[1:0]

Valid Valid

NOTES: A. During autoincrement mode, although the EHPI internally increments the memory address, reads of the HPIA register by the hos

will always indicate the base address.

B. In autoincrement mode, if HBE[1:0] are used to access the data as 8-bit-wide units, the HPIA increments only following each high

byte (HBE1 low) access.

C. The falling edge of HCS must occur concurrent with or before the falling edge of HDS. The rising edge of HCS must occu

concurrent with or after the rising edge of HDS. If HDS1 and/or HDS2 are tied permanently active and HCS is used as a strobe

the timing requirements shown for HDS apply to HCS. HRDY is always driven to the same value as its internal state.

Figure 5−34. EHPI Multiplexed Memory (HPID) Read Timings With Autoincrement