Electrical Specifications

125

November 2002 − Revised January 2005 SPRS205D

5.15 Enhanced Host-Port Interface (EHPI) Timings

Table 5−37 and Table 5−38 assume testing over recommended operating conditions (see Figure 5−31

through Figure 5−36).

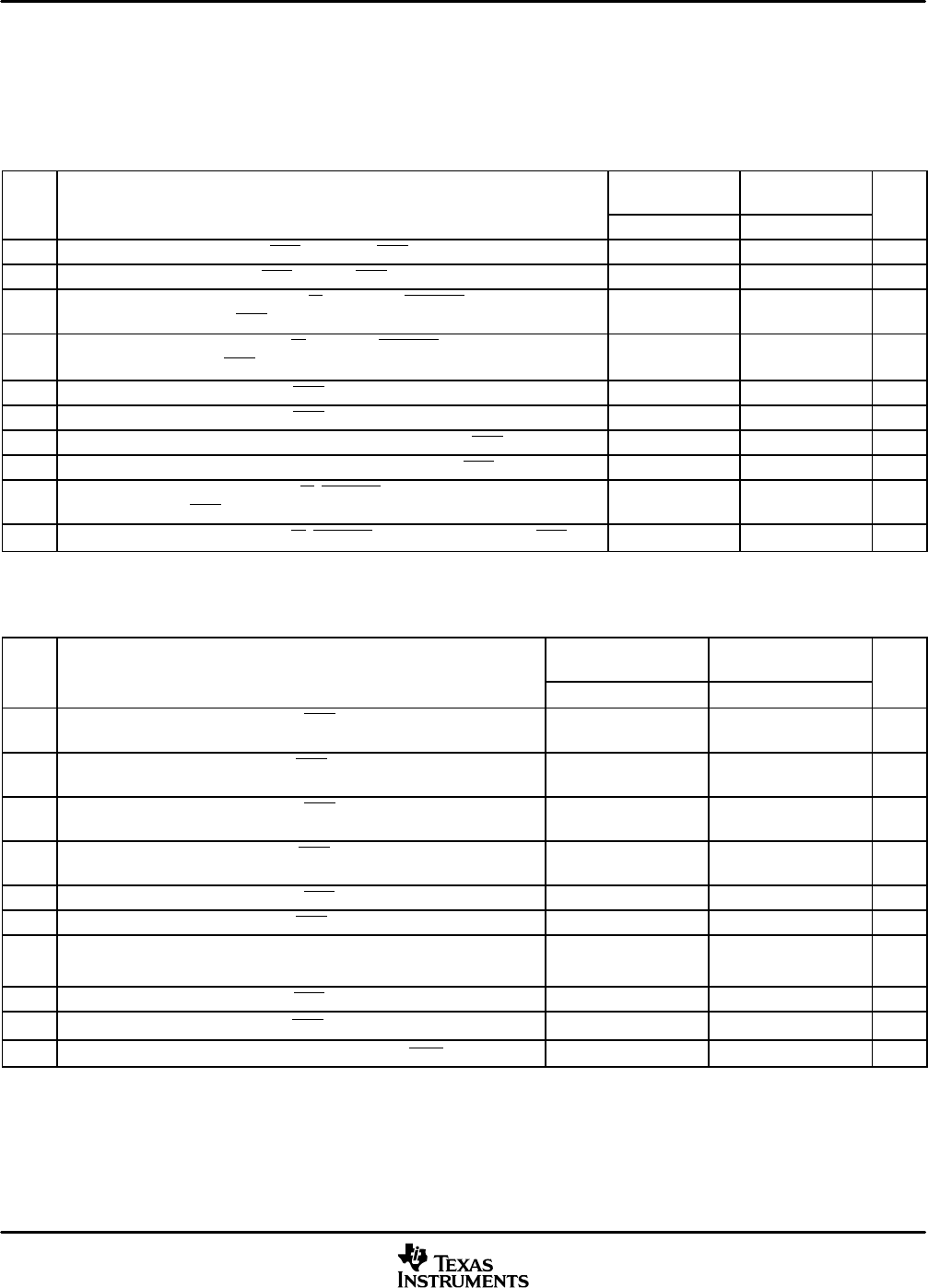

Table 5−37. EHPI Timing Requirements

CV

DD

= 1.2 V

CV

DD

= 1.35 V

CV

DD

= 1.6 V

MIN MAX MIN MAX

E11 t

su(HASL-HDSL)

Setup time, HAS low before HDS low 4 4 ns

E12 t

h(HDSL-HASL)

Hold time, HAS low after HDS low 3 3 ns

E13 t

su(HCNTLV-HDSL)

Setup time, (HR/W, HA[13:0], HBE[1:0], HCNTL[1:0]) valid

before HDS low

2 2 ns

E14 t

h(HDSL-HCNTLIV)

Hold time, (HR/W, HA[13:0], HBE[1:0], HCNTL[1:0]) invalid

after HDS low

4 4 ns

E15 t

w(HDSL)

Pulse duration, HDS low 4P

†

4P

†

ns

E16 t

w(HDSH)

Pulse duration, HDS high 4P

†

4P

†

ns

E17 t

su(HDV-HDSH)

Setup time, HD bus write data valid before HDS high 3 3 ns

E18 t

h(HDSH-HDIV)

Hold time, HD bus write data invalid after HDS high 4 4 ns

E19 t

su(HCNTLV-HASL)

Setup time, (HR/W, HBE[1:0], HCNTL[1:0]) valid before

HAS low

3 3 ns

E20 t

h(HASL-HCNTLIV)

Hold time, (HR/W, HBE[1:0], HCNTL[1:0]) valid after HAS low 4 4 ns

†

P = 1/CPU clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

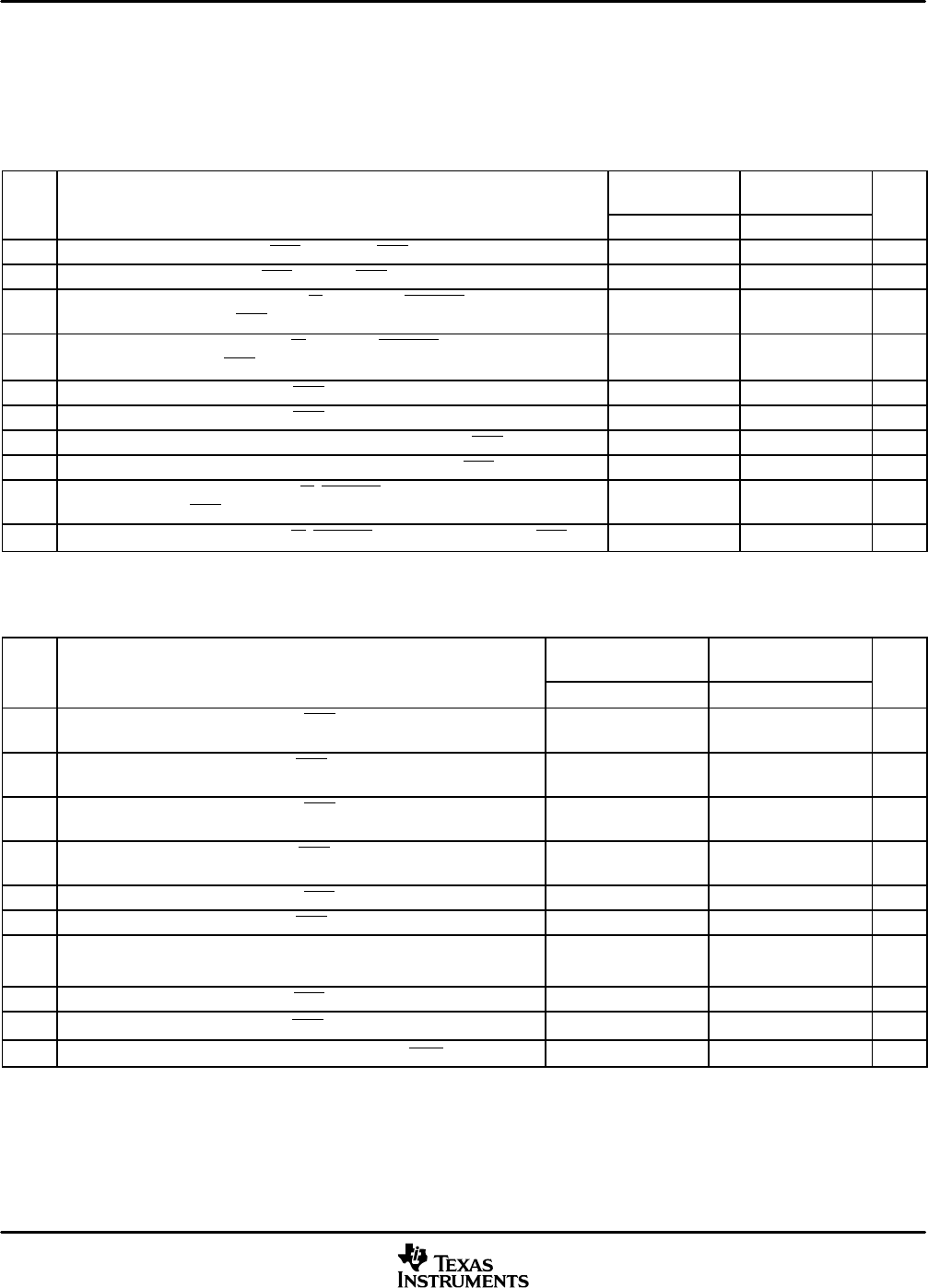

Table 5−38. EHPI Switching Characteristics

.

CV

DD

= 1.2 V

CV

DD

= 1.35 V

CV

DD

= 1.6 V

MIN MAX MIN MAX

E1 t

en(HDSL-HDD)M

Enable time, HDS low to HD bus enabled

(memory access)

6 26 6 19 ns

E2 t

d(HDSL-HDV)M

Delay time, HDS low to HD bus read data valid

(memory access)

14P

†‡

14P

†‡

ns

E4 t

en(HDSL-HDD)R

Enable time, HDS low to HD enabled

(register access)

6 26 6 19 ns

E5 t

d(HDSL-HDV)R

Delay time, HDS low to HD bus read data valid

(register access)

26 19 ns

E6 t

dis(HDSH-HDIV)

Disable time, HDS high to HD bus read data invalid 6 26 6 19 ns

E7 t

d(HDSL-HRDYL)

Delay time, HDS low to HRDY low (during reads) 18 15 ns

E8

t

d(HDV-HRDYH)

Delay time, HD bus valid to HRDY high

(during reads)

2 2 ns

E9 t

d(HDSH-HRDYL)

Delay time, HDS high to HRDY low (during writes) 18 15 ns

E10

t

d(HDSH-HRDYH)

Delay time, HDS high to HRDY high (during writes) 14P

†‡

14P

†‡

ns

E21

t

d(COH-HINT)

Delay time, CLKOUT high to HINT high/low 0 11 0 8 ns

†

P = 1/CPU clock frequency in ns. For example, when running parts at 200 MHz, use P = 5 ns.

‡

EHPI latency is dependent on the number of DMA channels active, their priorities and their source/destination ports. The latency shown assumes

no competing CPU or DMA activity to the memory resource being accessed by the EHPI.