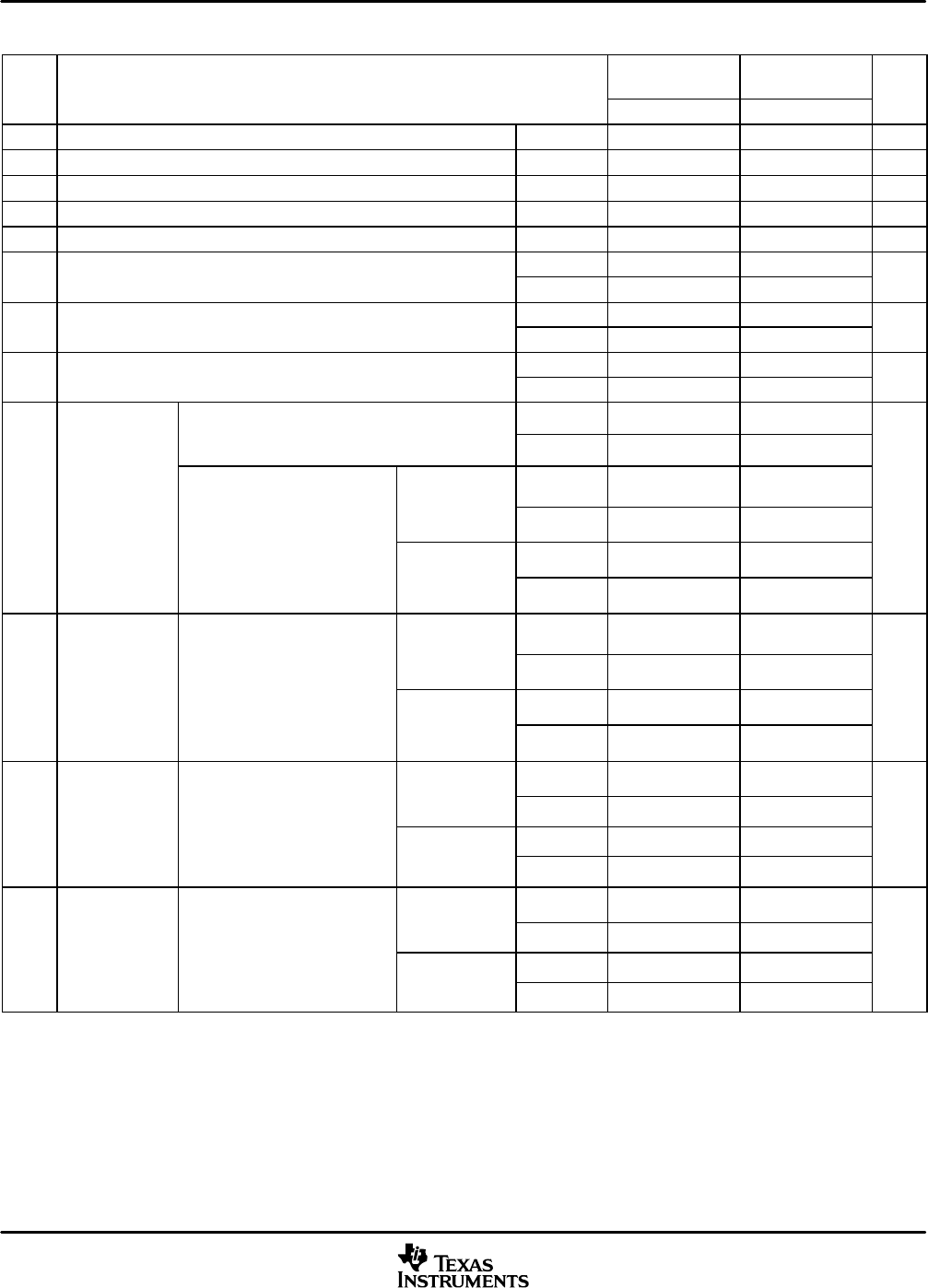

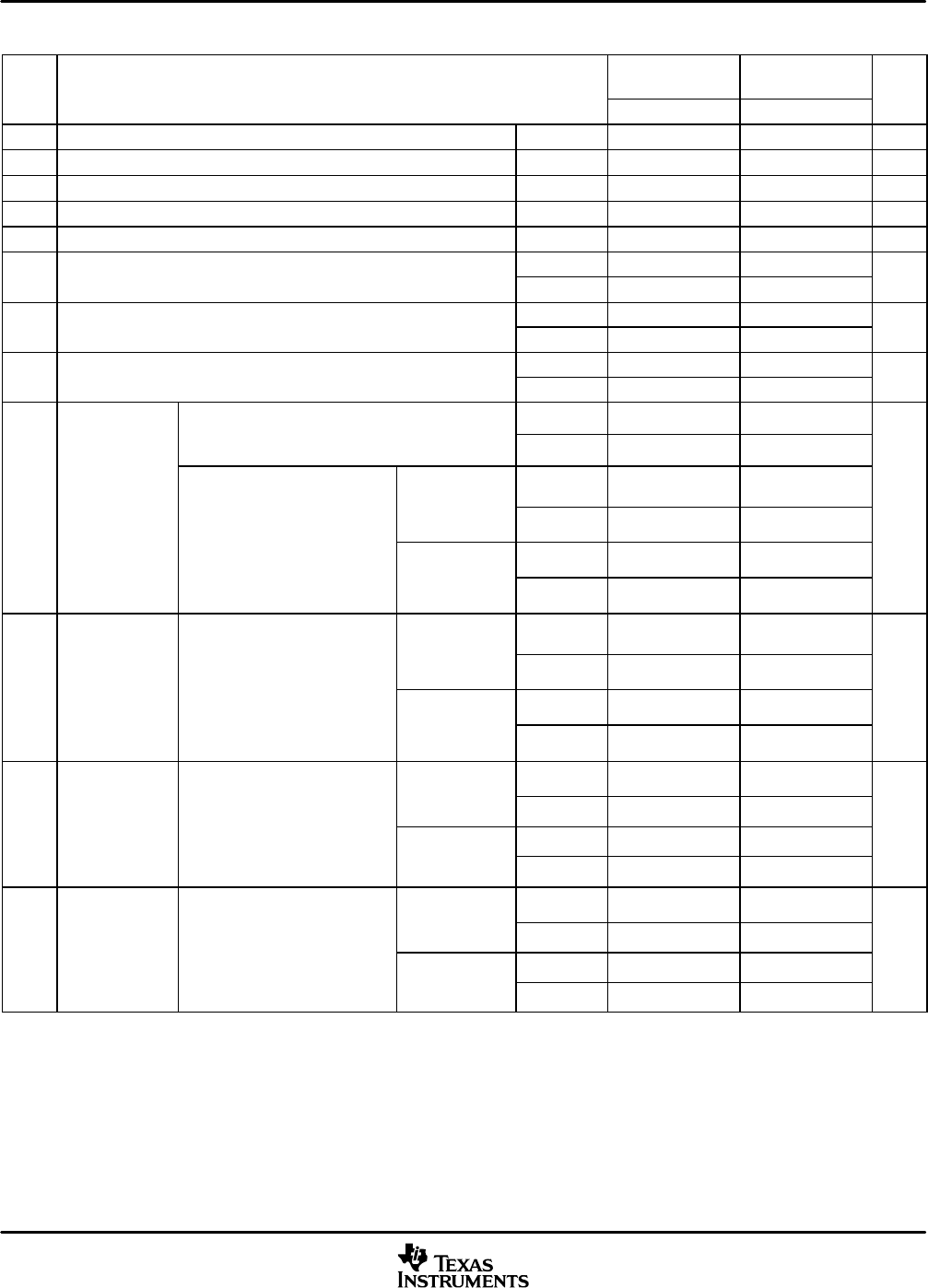

Electrical Specifications

112

November 2002 − Revised January 2005SPRS205D

Table 5−24. McBSP0 Switching Characteristics

†‡

CV

DD

= 1.2 V

CV

DD

= 1.35 V

CV

DD

= 1.6 V

MIN MAX MIN MAX

MC1 t

c(CKRX)

Cycle time, CLKR/X CLKR/X int 2P 2P ns

MC3 t

r(CKRX)

Rise time, CLKR/X CLKR/X int 1 1 ns

MC4 t

f(CKRX)

Fall time, CLKR/X CLKR/X int 1 1 ns

MC11 t

w(CKRXH)

Pulse duration, CLKR/X high CLKR/X int D−2

§

D+2

§

D−1

§

D+1

§

ns

MC12 t

w(CKRXL)

Pulse duration, CLKR/X low CLKR/X int C−2

§

C+2

§

C−1

§

C+1

§

ns

Delay time, CLKR high to internal FSR valid

CLKR int −2 1 −2 1

d(CKRH-FRV)

Delay time, CLKR high to internal FSR valid

CLKR ext 4 13 4 8

Delay time, CLKX high to internal FSX valid

CLKX int −2 2 −2 2

d(CKXH-FXV)

Delay time, CLKX high to internal FSX valid

CLKX ext 4 15 4 9

Disable time, DX high-impedance from CLKX high

CLKX int 0 5 −5 1

dis(CKXH-DXHZ)

Disable time, DX high-impedance from CLKX high

following last data bit

CLKX ext 10 18 3 11

Delay time, CLKX high to DX valid.

This applies to all bits except the first bit

CLKX int 5 4

This applies to all bits except the first bit

transmitted.

CLKX ext 15 9

Delay time, CLKX high to DX

¶

CLKX int 4 2

d(CKXH-DXV)

valid

¶

Only applies to first bit

CLKX ext 13 7

Only applies to first b

transmitted when in Data Dela

y

1 or 2 (XDATDLY = 01b or 10b)

CLKX int 2P + 1 2P + 1

transmitted when in Data Delay

1 or 2 (XDATDLY = 01b or 10b

modes

CLKX ext 2P + 4 2P + 3

Enable time, DX driven from

¶

CLKX int −1 −3

CLKX high

¶

Only applies to first bit

CLKX ext 6 3

en(CKXH-DX)

Only applies to first b

transmitted when in Data Dela

y

1 or 2 (XDATDLY= 01b or 10b)

CLKX int P − 1 P − 3

transmitted when in Data Delay

1 or 2 (XDATDLY= 01b or 10b

modes

CLKX ext P + 6 P + 3

Delay time, FSX high to DX

¶

FSX int 2 2

FSX ext 13 8

d(FXH-DXV)

Only applies to first b

it

transmitted when in Data Delay

FSX int 2P + 1 2P + 1

transmitted when in Data Delay

0 (XDATDLY= 00b) mode.

FSX ext 2P + 10 2P + 10

Enable time, DX driven from

¶

FSX int 0 0

FSX ext 8 3

en(FXH-DX)

Only applies to first b

it

transmitted when in Data Delay

FSX int P − 3 P − 3

transmitted when in Data Delay

0 (XDATDLY= 00b) mode

FSX ext P + 8 P + 4

†

Polarity bits CLKRP = CLKXP = FSRP = FSXP = 0. If the polarity of any of the signals is inverted, then the timing references of that signal are

also inverted.

‡

P = 1/CPU clock frequency. For example, when running parts at 200 MHz, use P = 5 ns. In addition to CPU frequency, the maximum operating

frequency of the serial port also depends on meeting the rest of the switching characteristics and timing requirements parameters specified.

§

T=CLKRX period = (1 + CLKGDV) * P

C=CLKRX low pulse width = T/2 when CLKGDV is odd or zero and = (CLKGDV/2) * P when CLKGDV is even

D=CLKRX high pulse width = T/2 when CLKGDV is odd or zero and = (CLKGDV/2 + 1) * P when CLKGDV is even

¶

See the TMS320C55x DSP Peripherals Overview Reference Guide (literature number SPRU317) for a description of the DX enable (DXENA)

and data delay features of the McBSP.