Electrical Specifications

93

November 2002 − Revised January 2005 SPRS205D

5.7 Memory Interface Timings

5.7.1 Asynchronous Memory Timings

Table 5−7 and Table 5−8 assume testing over recommended operating conditions (see Figure 5−6 and

Figure 5−7).

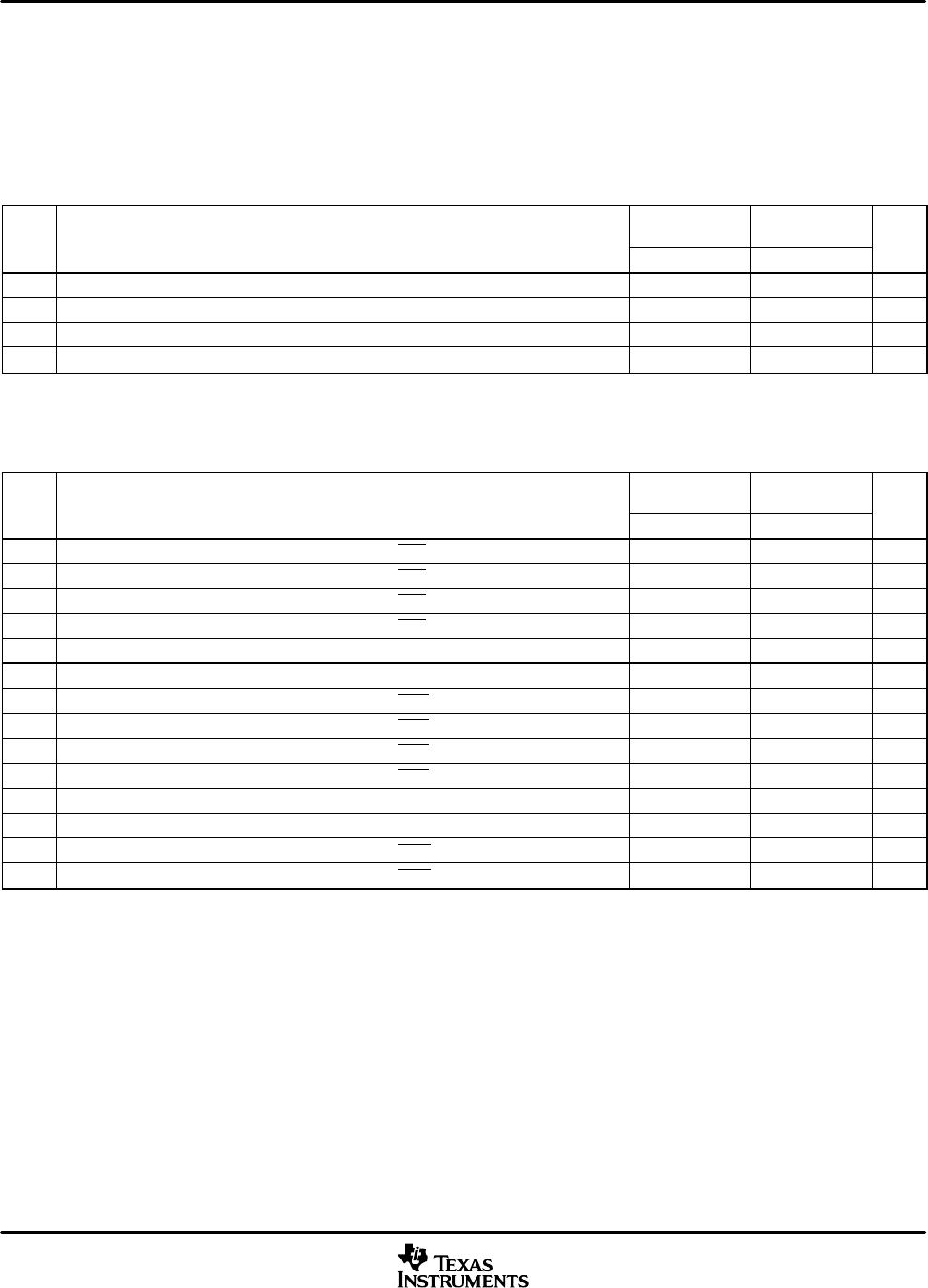

Table 5−7. Asynchronous Memory Cycle Timing Requirements

CV

DD

= 1.2 V

CV

DD

= 1.35 V

CV

DD

= 1.6 V

MIN MAX MIN MAX

M1 t

su(DV-COH)

Setup time, read data valid before CLKOUT high

†

6 5 ns

M2 t

h(COH-DV)

Hold time, read data valid after CLKOUT high 0 0 ns

M3 t

su(ARDY-COH)

Setup time, ARDY valid before CLKOUT high

†

10 7 ns

M4 t

h(COH-ARDY)

Hold time, ARDY valid after CLKOUT high 0 0 ns

†

To ensure data setup time, simply program the strobe width wide enough. ARDY is internally synchronized. If ARDY does meet setup or hold

time, it may be recognized in the current cycle or the next cycle. Thus, ARDY can be an asynchronous input.

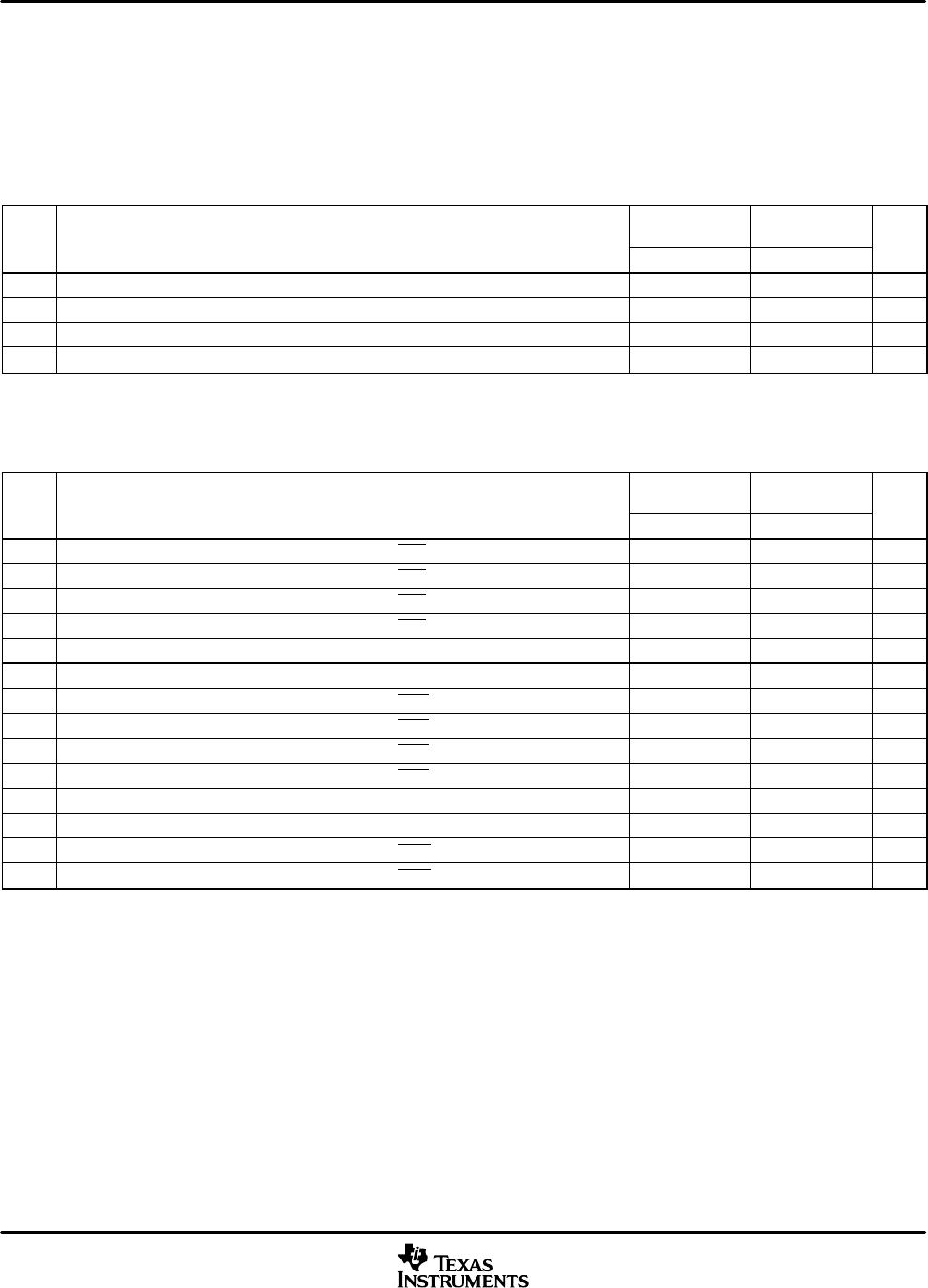

Table 5−8. Asynchronous Memory Cycle Switching Characteristics

CV

DD

= 1.2 V

CV

DD

= 1.35 V

CV

DD

= 1.6 V

MIN MAX MIN MAX

M5 t

d(COH-CEV)

Delay time, CLKOUT high to CEx valid −2 4 −2 4 ns

M6 t

d(COH-CEIV)

Delay time, CLKOUT high to CEx invalid −2 4 −2 4 ns

M7 t

d(COH-BEV)

Delay time, CLKOUT high to BEx valid 4 4 ns

M8 t

d(COH-BEIV)

Delay time, CLKOUT high to BEx invalid −2 −2 ns

M9 t

d(COH-AV)

Delay time, CLKOUT high to address valid 4 4 ns

M10 t

d(COH-AIV)

Delay time, CLKOUT high to address invalid −2 −2 ns

M11 t

d(COH-AOEV)

Delay time, CLKOUT high to AOE valid −2 4 −2 4 ns

M12 t

d(COH-AOEIV)

Delay time, CLKOUT high to AOE invalid −2 4 −2 4 ns

M13 t

d(COH-AREV)

Delay time, CLKOUT high to ARE valid −2 4 −2 4 ns

M14 t

d(COH-AREIV)

Delay time, CLKOUT high to ARE invalid −2 4 −2 4 ns

M15 t

d(COH-DV)

Delay time, CLKOUT high to data valid 4 4 ns

M16 t

d(COH-DIV)

Delay time, CLKOUT high to data invalid −2 −2 ns

M17 t

d(COH-AWEV)

Delay time, CLKOUT high to AWE valid −2 4 −2 4 ns

M18 t

d(COH-AWEIV)

Delay time, CLKOUT high to AWE invalid −2 4 −2 4 ns