Electrical Specifications

90

November 2002 − Revised January 2005SPRS205D

5.6.3 Clock Generation in Bypass Mode (DPLL Disabled)

The frequency of the reference clock provided at the X2/CLKIN pin can be divided by a factor of one, two, or

four to generate the internal CPU clock cycle. The divide factor (D) is set in the BYPASS_DIV field of the clock

mode register. The contents of this field only affect clock generation while the device is in bypass mode. In

this mode, the digital phase-locked loop (DPLL) clock synthesis is disabled.

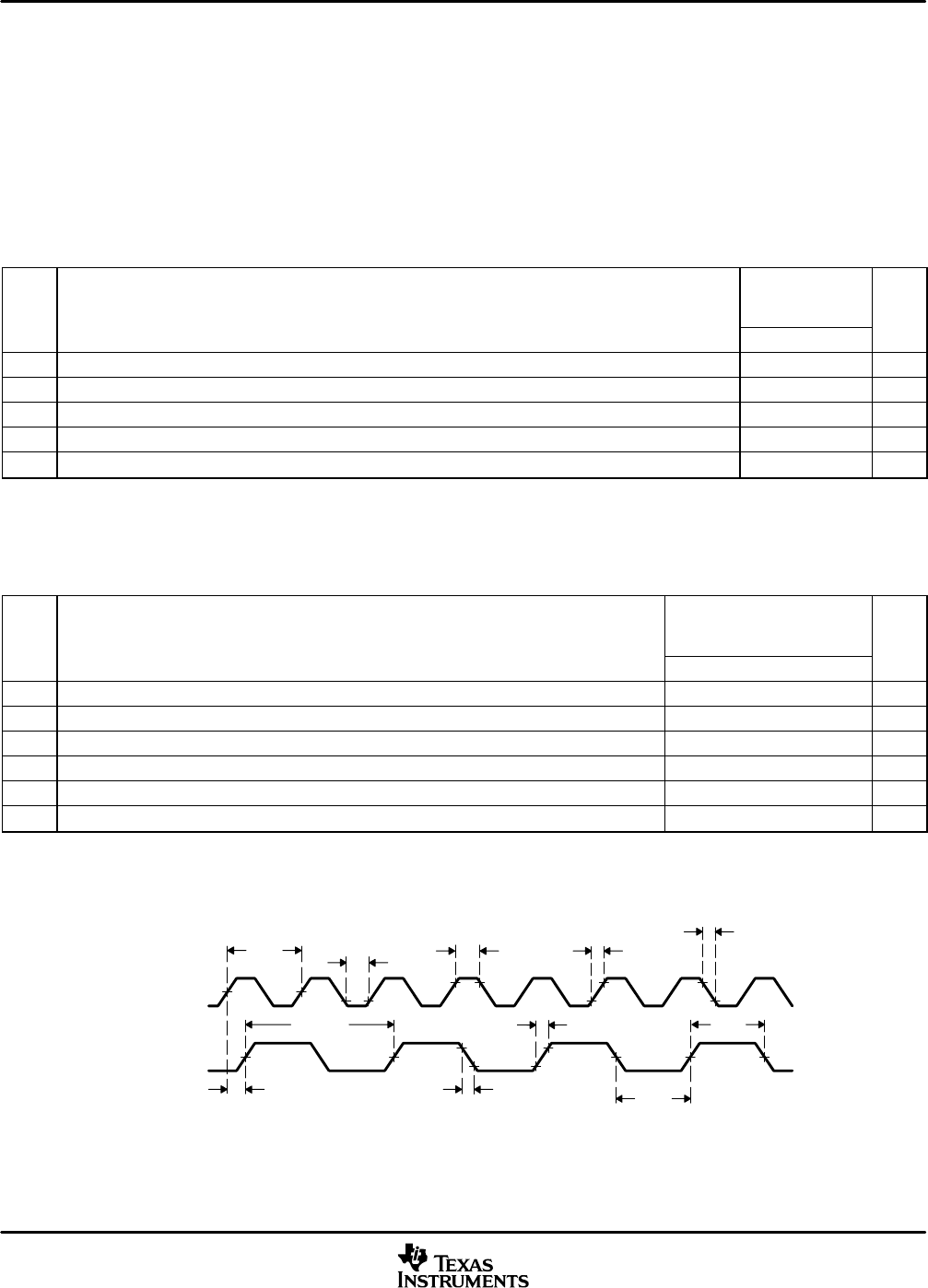

Table 5−2 and Table 5−3 assume testing over recommended operating conditions and H = 0.5t

c(CO)

(see

Figure 5−3).

Table 5−2. CLKIN Timing Requirements

NO.

CV

DD

= 1.2 V

CV

DD

= 1.35 V

CV

DD

= 1.6 V

UNIT

MIN MAX

C1 t

c(CI)

Cycle time, X2/CLKIN 20 400

†

ns

C2 t

f(CI)

Fall time, X2/CLKIN 4 ns

C3 t

r(CI)

Rise time, X2/CLKIN 4 ns

C10 t

w(CIL)

Pulse duration, CLKIN low 6 ns

C11 t

w(CIH)

Pulse duration, CLKIN high 6 ns

†

This device utilizes a fully static design and therefore can operate with t

c(CI)

approaching ∞. If an external crystal is used, the X2/CLKIN cycle

time is limited by the crystal frequency range listed in Table 5−1.

Table 5−3. CLKOUT Switching Characteristics

NO.

PARAMETER

CV

DD

= 1.2 V

CV

DD

= 1.35 V

CV

DD

= 1.6 V

UNIT

MIN TYP MAX

C4 t

c(CO)

Cycle time, CLKOUT 20

‡

D*t

c(CI)

§

1600

†

ns

C5 t

d(CI-CO)

Delay time, X2/CLKIN high to CLKOUT high/low 5 15 25 ns

C6 t

f(CO)

Fall time, CLKOUT 1 ns

C7 t

r(CO)

Rise time, CLKOUT 1 ns

C8 t

w(COL)

Pulse duration, CLKOUT low H − 1 H + 1 ns

C9 t

w(COH)

Pulse duration, CLKOUT high H − 1 H + 1 ns

†

This device utilizes a fully static design and therefore can operate with t

c(CO)

approaching ∞. If an external crystal is used, the X2/CLKIN cycle

time is limited by the crystal frequency range listed in Table 5−1.

‡

It is recommended that the DPLL synthesised clocking option be used to obtain maximum operating frequency.

§

D = 1/(PLL Bypass Divider)

C3

C2

C1

C4

C5

C7

C6

C8

C9

X2/CLKIN

CLKOUT

C10

C11

NOTE A: The relationship of X2/CLKIN to CLKOUT depends on the PLL bypass divide factor chosen for the CLKMD register. The waveform

relationship shown in Figure 5−3 is intended to illustrate the timing parameters based on CLKOUT = 1/2(CLKIN) configuration.

Figure 5−3. Bypass Mode Clock Timings