Electrical Specifications

81

November 2002 − Revised January 2005 SPRS205D

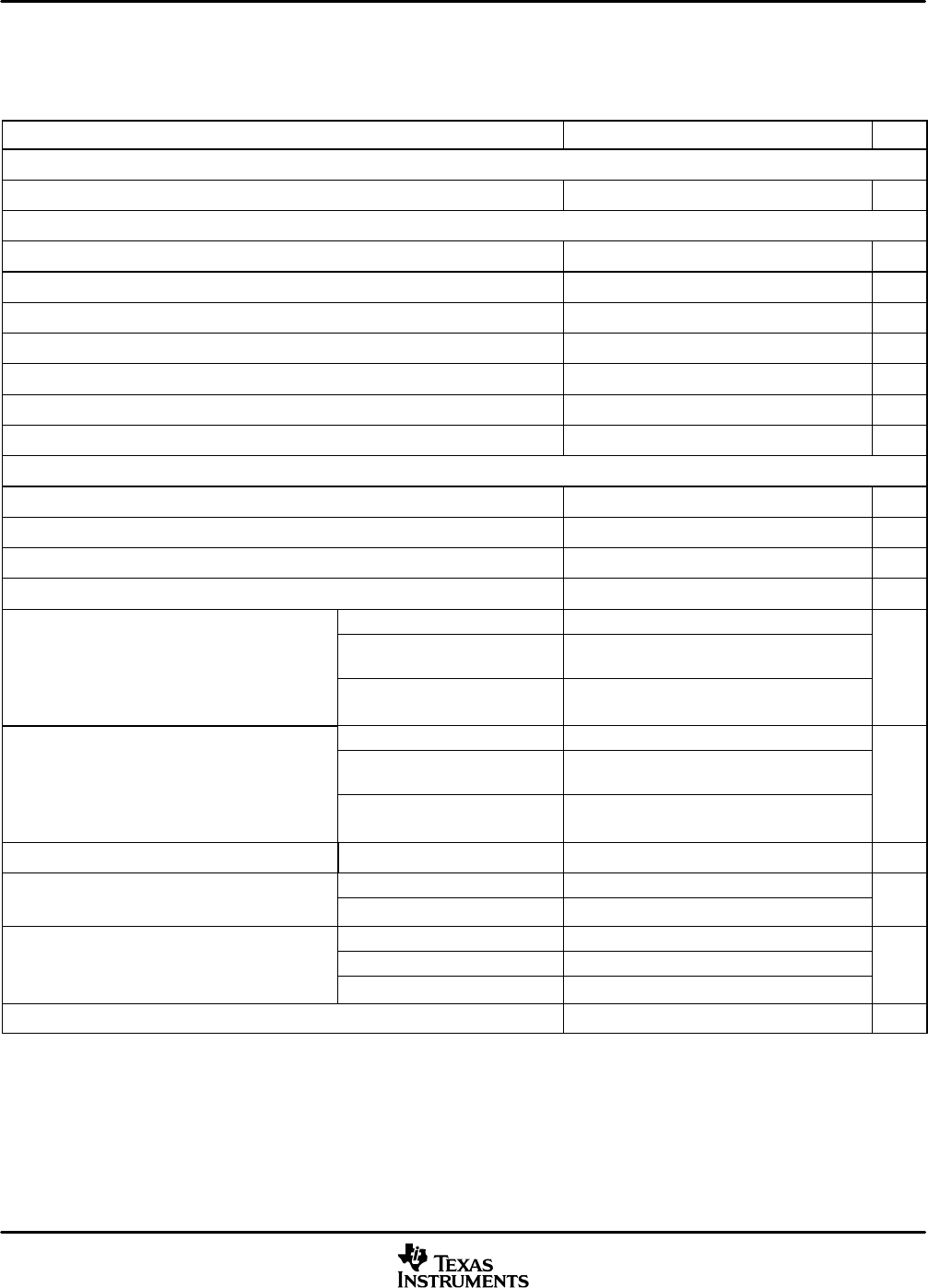

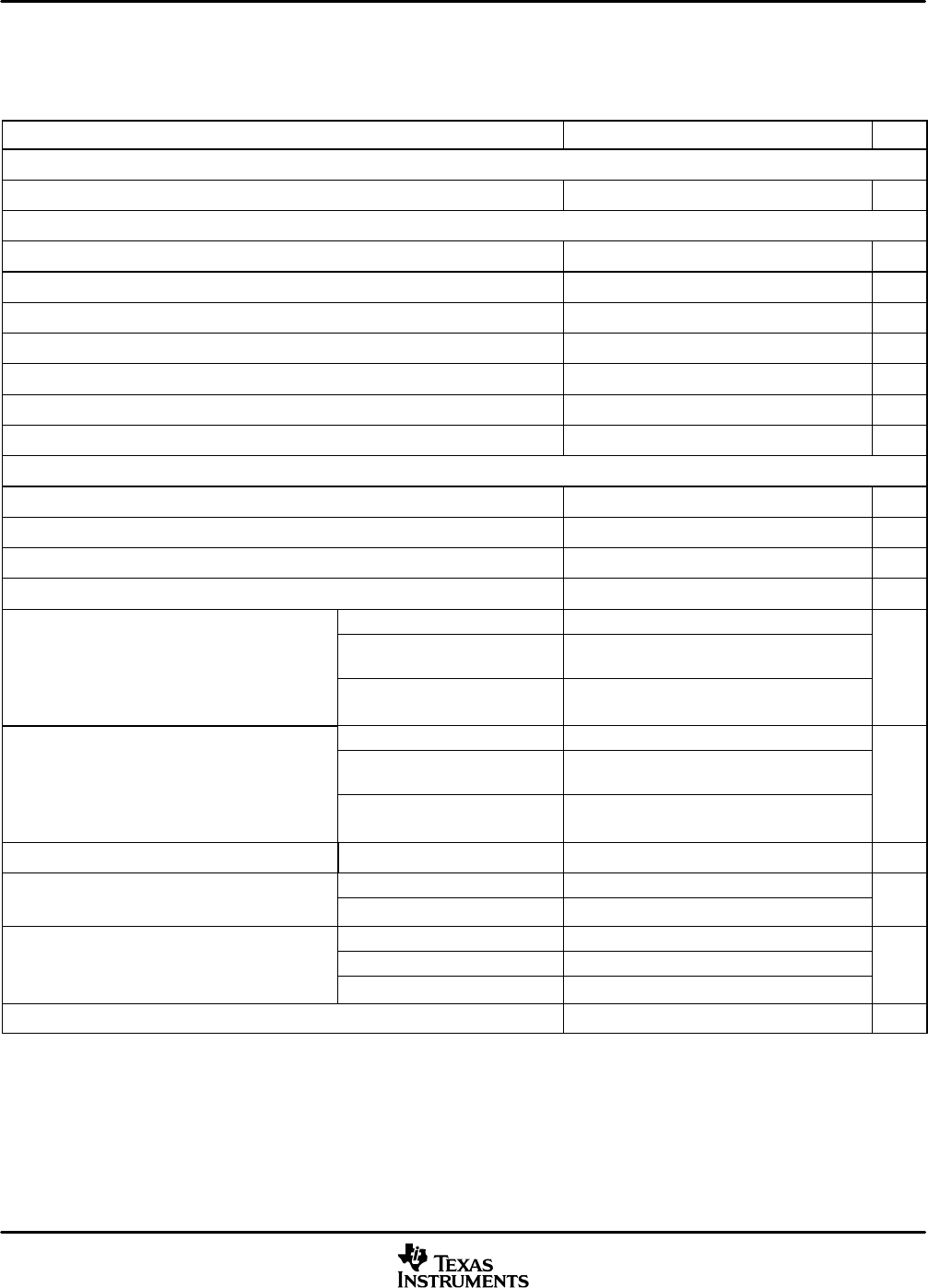

5.2 Recommended Operating Conditions

5.2.1 Recommended Operating Conditions for CV

DD

= 1.2 V (108 MHz)

MIN NOM MAX UNIT

Core

CV

DD

Device supply voltage 1.14 1.2 1.26 V

Peripherals

RCV

DD

RTC module supply voltage, core 1.14 1.2 1.26 V

RDV

DD

RTC module supply voltage, I/O (RTCINX1 and RTCINX2) 1.14 1.2 1.26 V

USBPLLV

DD

USBPLL supply voltage

†

1.14 1.2 1.26 V

USBV

DD

USB module supply voltage, I/O (DP, DN, and PU) 3 3.3 3.6 V

DV

DD

Device supply voltage, I/O (except DP, DN, PU, SDA, SCL)

‡

2.7 3.3 3.6 V

ADV

DD

A/D module digital supply voltage 2.7 3.3 3.6 V

AV

DD

A/D module analog supply voltage 2.7 3.3 3.6 V

Grounds

V

SS

Supply voltage, GND, I/O, and core 0 V

ADV

SS

Supply voltage, GND, A/D module, digital 0 V

AV

SS

Supply voltage, GND, A/D module, analog 0 V

USBPLLV

SS

Supply voltage, GND, USBPLL 0 V

DN and DP

§

2.0

V

High-level input voltage, I/O

SDA & SCL: V

DD

related input

levels

‡

0.7*DV

DD

DV

DD

(max) +0.5

V

High-level input voltage, I/O

All other inputs

(including hysteresis inputs)

2.0 DV

DD

+ 0.3

DN and DP

§

0.8

V

Low-level input voltage, I/O

SDA &SCL: V

DD

related input

levels

‡

−0.5 0.3 * DV

DD

V

Low-level input voltage, I/O

All other inputs

(including hysteresis inputs)

−0.3 0.8

V

hys

Hysteresis level Inputs with hysteresis only 0.1*DV

DD

V

High-level output current

DN and DP

§

(V

OH

= 2.45 V) −17.0

OH

High-level output current

All other outputs −4

DN and DP

§

(V

OL

= 0.36 V) 17.0

I

Low-level output current

SDA and SCL

‡

3

mA

All other outputs 4

T

C

Operating case temperature −40 85

_C

†

USB PLL is susceptible to power supply ripple. The maximum allowable supply ripple is 1% for 1 Hz to 5 kHz; 1.5% for 5 kHz to 10 MHz; 3%

for 10 MHz to 100 MHz, and less than 5% for 100 MHz or greater.

‡

The I

2

C pins SDA and SCL do not feature fail-safe I/O buffers. These pins could potentially draw current when the device is powered down.

Due to the fact that different voltage devices can be connected to the I

2

C bus, the level of logic 0 (low) and logic 1 (high) are not fixed and

depends on the associated V

DD

.

§

USB I/O pins DP and DN can tolerate a short circuit at D+ and D− to 0 V or 5 V, as long as the recommended series resistors (see Figure 5−42)

are connected between the D+ and DP (package), and the D− and DN (package). Do not apply a short circuit to the USB I/O pins DP and DN

in absence of the series resistors.