Functional Overview

64

November 2002 − Revised January 2005SPRS205D

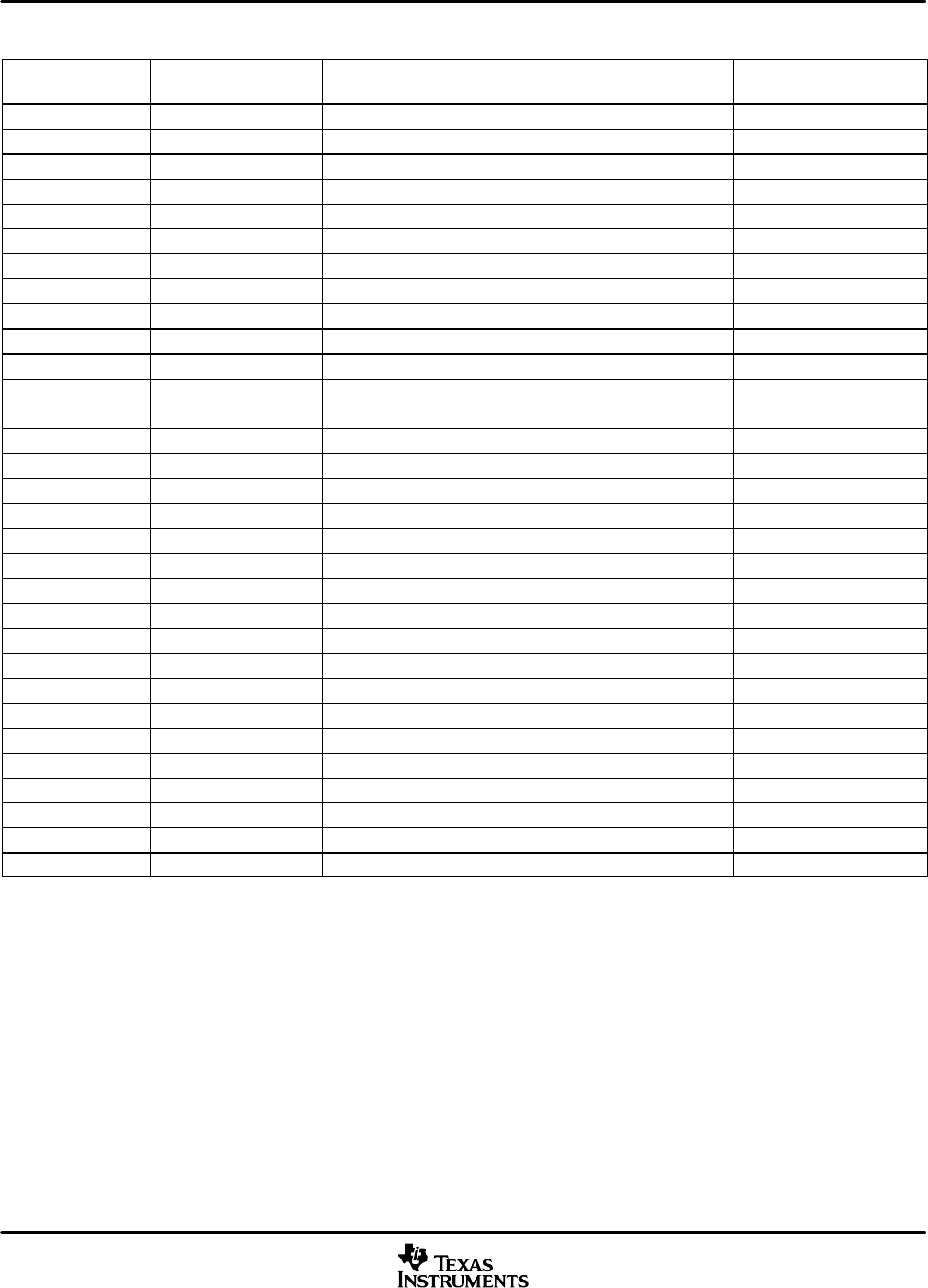

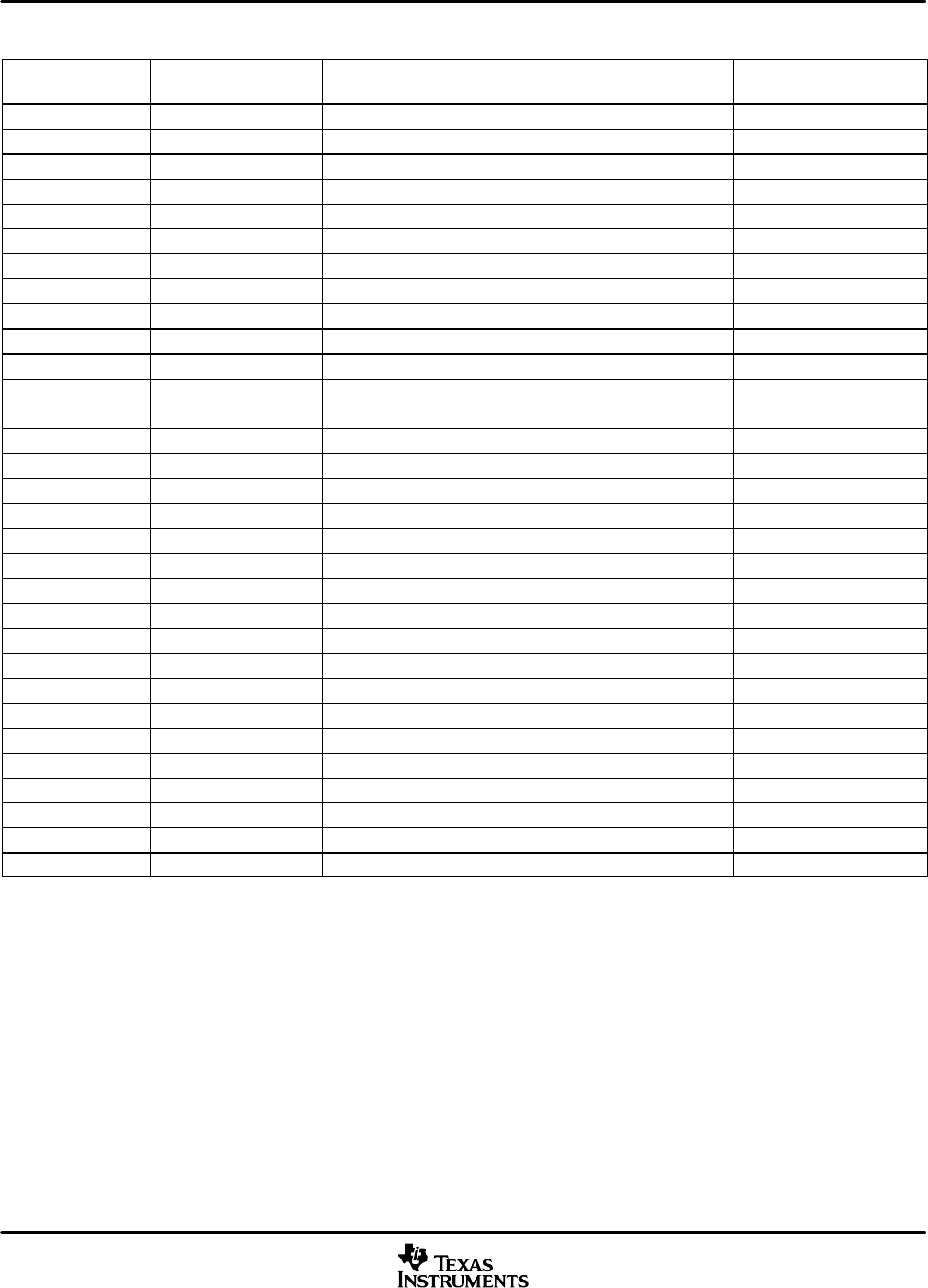

Table 3−28. Multichannel Serial Port #0

PORT ADDRESS

(WORD)

REGISTER NAME DESCRIPTION RESET VALUE

†

0x2800 DRR2_0[15:0] Data Receive Register 2, McBSP #0 0000 0000 0000 0000

0x2801 DRR1_0[15:0] Data Receive Register 1, McBSP #0 0000 0000 0000 0000

0x2802 DXR2_0[15:0] Data Transmit Register 2, McBSP #0 0000 0000 0000 0000

0x2803 DXR1_0[15:0] Data Transmit Register 1, McBSP #0 0000 0000 0000 0000

0x2804 SPCR2_0[15:0] Serial Port Control Register 2, McBSP #0 0000 0000 0000 0000

0x2805 SPCR1_0[15:0] Serial Port Control Register 1, McBSP #0 0000 0000 0000 0000

0x2806 RCR2_0[15:0] Receive Control Register 2, McBSP #0 0000 0000 0000 0000

0x2807 RCR1_0[15:0] Receive Control Register 1, McBSP #0 0000 0000 0000 0000

0x2808 XCR2_0[15:0] Transmit Control Register 2, McBSP #0 0000 0000 0000 0000

0x2809 XCR1_0[15:0] Transmit Control Register 1, McBSP #0 0000 0000 0000 0000

0x280A SRGR2_0[15:0] Sample Rate Generator Register 2, McBSP #0 0020 0000 0000 0000

0x280B SRGR1_0[15:0] Sample Rate Generator Register 1, McBSP #0 0000 0000 0000 0001

0x280C MCR2_0[15:0] Multichannel Control Register 2, McBSP #0 0000 0000 0000 0000

0x280D MCR1_0[15:0] Multichannel Control Register 1, McBSP #0 0000 0000 0000 0000

0x280E RCERA_0[15:0] Receive Channel Enable Register Partition A, McBSP #0 0000 0000 0000 0000

0x280F RCERB_0[15:0] Receive Channel Enable Register Partition B, McBSP #0 0000 0000 0000 0000

0x2810 XCERA_0[15:0] Transmit Channel Enable Register Partition A, McBSP #0 0000 0000 0000 0000

0x2811 XCERB_0[15:0] Transmit Channel Enable Register Partition B, McBSP #0 0000 0000 0000 0000

0x2812 PCR0[15:0] Pin Control Register, McBSP #0 0000 0000 0000 0000

0x2813 RCERC_0[15:0] Receive Channel Enable Register Partition C, McBSP #0 0000 0000 0000 0000

0x2814 RCERD_0[15:0] Receive Channel Enable Register Partition D, McBSP #0 0000 0000 0000 0000

0x2815 XCERC_0[15:0] Transmit Channel Enable Register Partition C, McBSP #0 0000 0000 0000 0000

0x2816 XCERD_0[15:0] Transmit Channel Enable Register Partition D, McBSP #0 0000 0000 0000 0000

0x2817 RCERE_0[15:0] Receive Channel Enable Register Partition E, McBSP #0 0000 0000 0000 0000

0x2818 RCERF_0[15:0] Receive Channel Enable Register Partition F, McBSP #0 0000 0000 0000 0000

0x2819 XCERE_0[15:0] Transmit Channel Enable Register Partition E, McBSP #0 0000 0000 0000 0000

0x281A XCERF_0[15:0] Transmit Channel Enable Register Partition F, McBSP #0 0000 0000 0000 0000

0x281B RCERG_0[15:0] Receive Channel Enable Register Partition G, McBSP #0 0000 0000 0000 0000

0x281C RCERH_0[15:0] Receive Channel Enable Register Partition H, McBSP #0 0000 0000 0000 0000

0x281D XCERG_0[15:0] Transmit Channel Enable Register Partition G, McBSP #0 0000 0000 0000 0000

0x281E XCERH_0[15:0] Transmit Channel Enable Register Partition H, McBSP #0 0000 0000 0000 0000

†

Hardware reset; x denotes a “don’t care.”