Functional Overview

63

November 2002 − Revised January 2005 SPRS205D

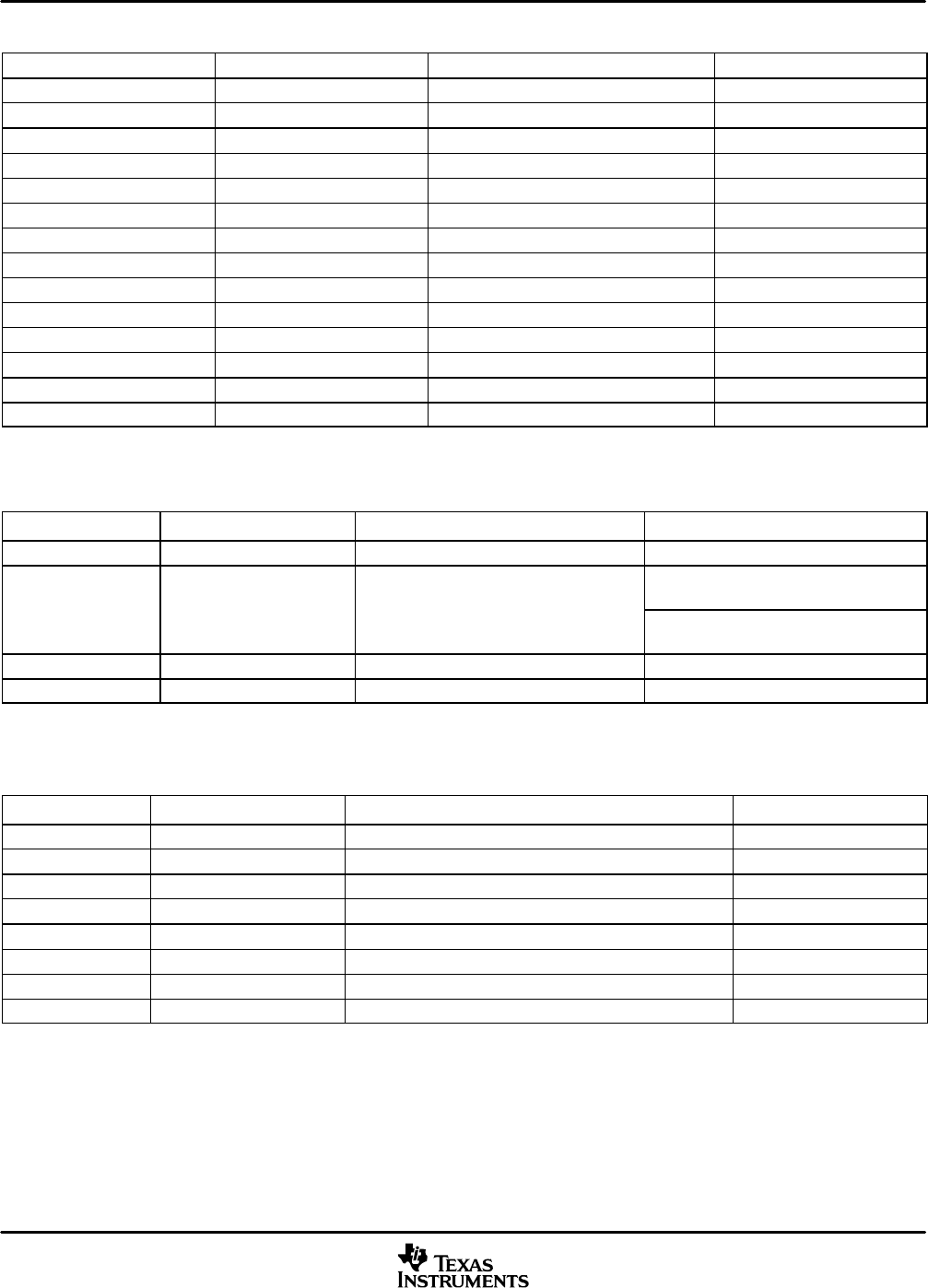

Table 3−25. Real-Time Clock Registers

WORD ADDRESS REGISTER NAME DESCRIPTION RESET VALUE

†

0x1800 RTCSEC Seconds Register 0000 0000 0000 0000

0x1801 RTCSECA Seconds Alarm Register 0000 0000 0000 0000

0x1802 RTCMIN Minutes Register 0000 0000 0000 0000

0x1803 RTCMINA Minutes Alarm Register 0000 0000 0000 0000

0x1804 RTCHOUR Hours Register 0000 0000 0000 0000

0x1805 RTCHOURA Hours Alarm Register 0000 0000 0000 0000

0x1806 RTCDAYW Day of the Week Register 0000 0000 0000 0000

0x1807 RTCDAYM Day of the Month (date) Register 0000 0000 0000 0000

0x1808 RTCMONTH Month Register 0000 0000 0000 0000

0x1809 RTCYEAR Year Register 0000 0000 0000 0000

0x180A RTCPINTR Periodic Interrupt Selection Register 0000 0000 0000 0000

0x180B RTCINTEN Interrupt Enable Register 0000 0000 1000 0000

0x180C RTCINTFL Interrupt Flag Register 0000 0000 0000 0000

0x180D−0x1BFF Reserved

†

Hardware reset; x denotes a “don’t care.”

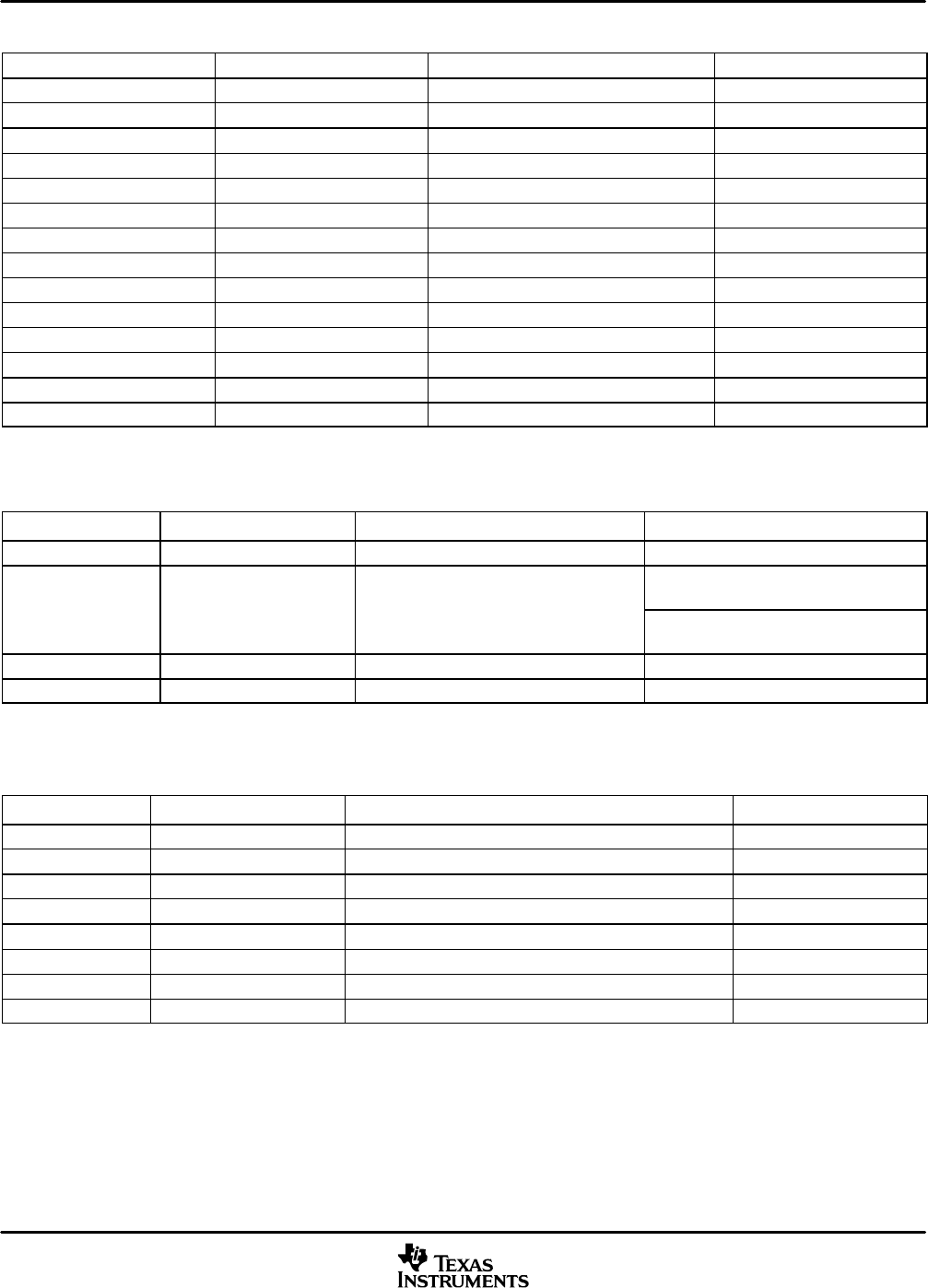

Table 3−26. Clock Generator

WORD ADDRESS REGISTER NAME DESCRIPTION

RESET VALUE

†

0x1C00 CLKMD[14:0] Clock Mode Register 0010 0000 0000 0010 DIV1 mode

USB DPLL Control Register

If non-USB boot mode:

0010 0000 0000 0110 DIV2 mode

USB DPLL Control Register

If USB boot mode:

0010 0010 0001 0011 PLL MULT4 mode

0x1E80 USBPLLSEL[2:0] USB PLL Selection Register 0000 0000 0000 0100

0x1F00 USBAPLL[15:0] USB APLL Control Register 0000 0000 0000 0000

†

Hardware reset; x denotes a “don’t care.”

‡

DPLL is the power-up default USB clock source.

Table 3−27. Timers

WORD ADDRESS REGISTER NAME DESCRIPTION

RESET VALUE

†

0x1000 TIM0[15:0] Timer Count Register, Timer #0 1111 1111 1111 1111

0x1001 PRD0[15:0] Period Register, Timer #0 1111 1111 1111 1111

0x1002 TCR0[15:0] Timer Control Register, Timer #0 0000 0000 0001 0000

0x1003 PRSC0[15:0] Timer Prescaler Register, Timer #0 xxxx 0000 xxxx 0000

0x2400 TIM1[15:0] Timer Count Register, Timer #1 1111 1111 1111 1111

0x2401 PRD1[15:0] Period Register, Timer #1 1111 1111 1111 1111

0x2402 TCR1[15:0] Timer Control Register, Timer #1 0000 0000 0001 0000

0x2403 PRSC1[15:0] Timer Prescaler Register, Timer #1 xxxx 0000 xxxx 0000

†

Hardware reset; x denotes a “don’t care.”