Functional Overview

59

November 2002 − Revised January 2005 SPRS205D

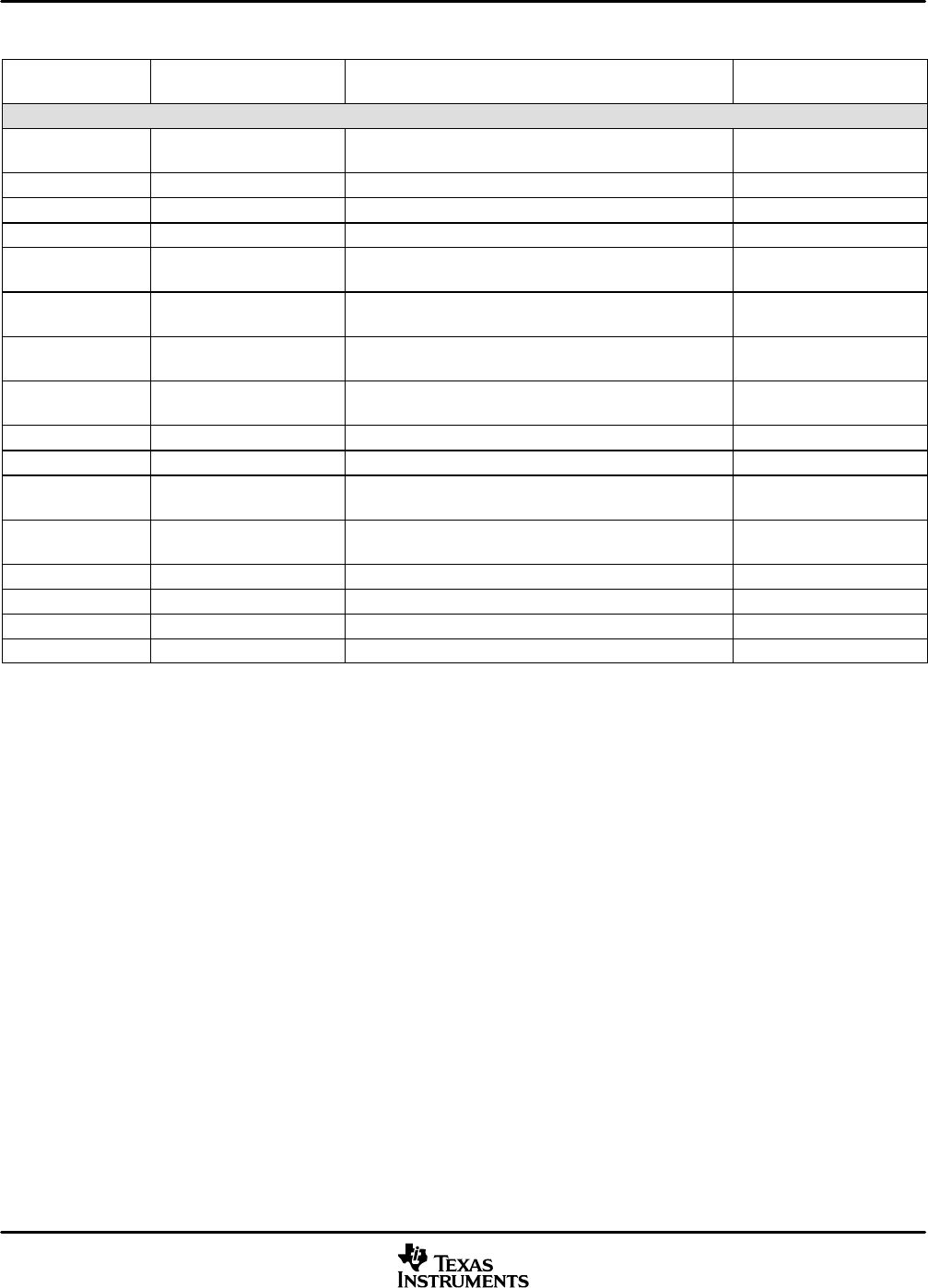

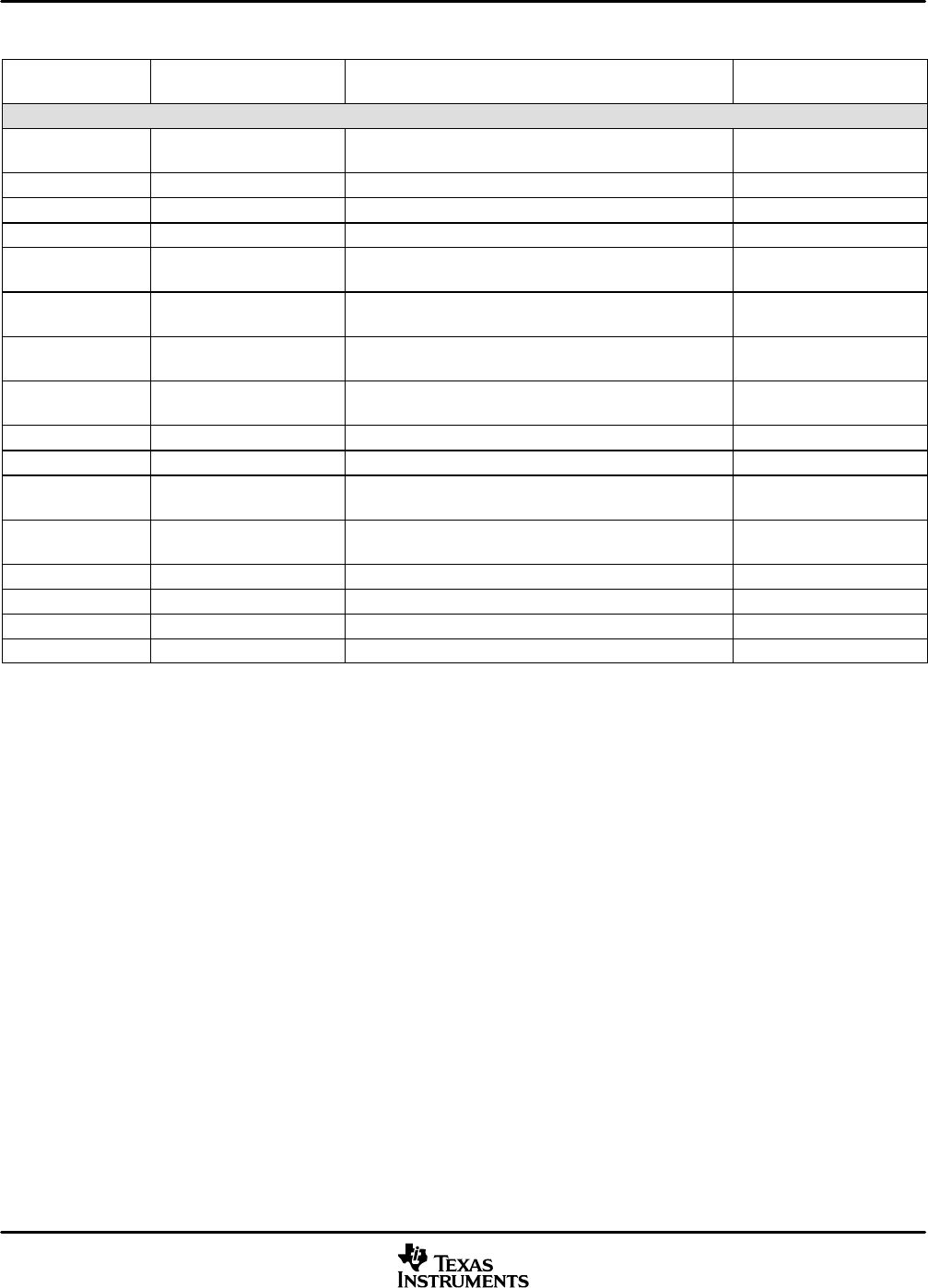

Table 3−24. DMA Configuration Registers (Continued)

PORT ADDRESS

(WORD)

RESET VALUE

†

DESCRIPTIONREGISTER NAME

CHANNEL #2 REGISTERS

0x0C40 DMA_CSDP2 DMA Channel 2 Source Destination

Parameters Register

0000 0000 0000 0000

0x0C41 DMA_CCR2[15:0] DMA Channel 2 Control Register 0000 0000 0000 0000

0x0C42 DMA_CICR2[5:0] DMA Channel 2 Interrupt Control Register xxxx xxxx xx00 0011

0x0C43 DMA_CSR2[6:0] DMA Channel 2 Status Register xxxx xxxx xx00 0000

0x0C44 DMA_CSSA_L2 DMA Channel 2 Source Start Address Register

(lower bits)

Undefined

0x0C45 DMA_CSSA_U2 DMA Channel 2 Source Start Address Register

(upper bits)

Undefined

0x0C46 DMA_CDSA_L2 DMA Channel 2 Source Destination Address Register

(lower bits)

Undefined

0x0C47 DMA_CDSA_U2 DMA Channel 2 Source Destination Address Register

(upper bits)

Undefined

0x0C48 DMA_CEN2 DMA Channel 2 Element Number Register Undefined

0x0C49 DMA_CFN2 DMA Channel 2 Frame Number Register Undefined

0x0C4A DMA_CFI2/

DMA_CSFI2

‡

DMA Channel 2 Frame Index Register/

DMA Channel 2 Source Frame Index Register

‡

Undefined

0x0C4B DMA_CEI2/

DMA_CSEI2

§

DMA Channel 2 Element Index Register/

DMA Channel 2 Source Element Index Register

§

Undefined

0x0C4C DMA_CSAC2 DMA Channel 2 Source Address Counter Undefined

0x0C4D DMA_CDAC2 DMA Channel 2 Destination Address Counter Undefined

0x0C4E DMA_CDEI2 DMA Channel 2 Destination Element Index Register Undefined

0x0C4F DMA_CDFI2 DMA Channel 2 Destination Frame Index Register Undefined

†

Hardware reset: x denotes a “don’t care.”

‡

On the TMS320VC5509, the channel frame index applies to both source and destination and this register behaves as DMA_CFIn. On the

TMS320VC5509A, DMA_CSFIn and DMA_CDFIn provide separate source and destination frame indexing. The 5509A can be programmed

for software compatibility with the 5509 through the Software Compatibility Register (DMA_GSCR).

§

On the TMS320VC5509, the channel element index applies to both source and destination and this register behaves as DMA_CEIn. On the

TMS320VC5509A, DMA_CSEIn and DMA_CDEIn provide separate source and destination frame indexing. The 5509A can be programmed

for software compatibility with the 5509 through the Software Compatibility Register (DMA_GSCR).