Functional Overview

49

November 2002 − Revised January 2005 SPRS205D

3.6.3 EHPI General-Purpose I/O

Six control lines of the External Parallel Bus can also be set as general-purpose I/O when the Parallel Port

Mode bit field of the External Bus Selection Register is set to Nonmultiplexed EHPI (10) or Multiplexed EHPI

mode (11). These pins are controlled by three registers: the enable register, EHPIGPIOEN, determines if the

pins serve as GPIO or address (Figure 3−13); the direction register, EHPIGPIODIR, determines if the GPIO

enabled pin is an input or output (Figure 3−14); and the data register, EHPIGPIODATA, determines the logic

states of the pins in GPIO mode (Figure 3−15).

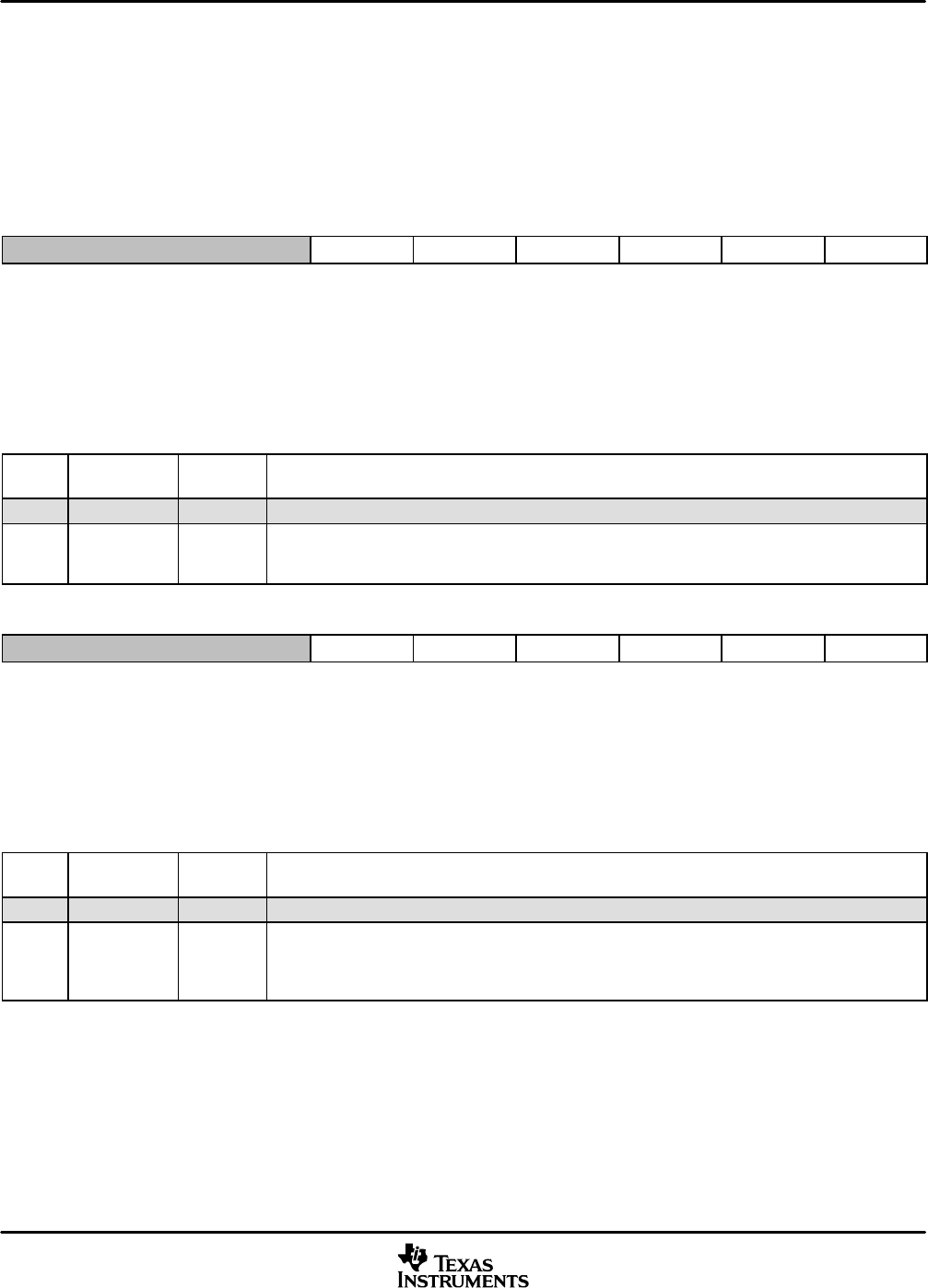

15 6543210

Reserved GPIOEN13 GPIOEN12 GPIOEN11 GPIOEN10 GPIOEN9 GPIOEN8

R, 0000 0000 00 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0

LEGEND: R = Read, W = Write, n = value after reset

Figure 3−13. EHPI GPIO Enable Register (EHPIGPIOEN) Bit Layout

Table 3−14. EHPI GPIO Enable Register (EHPIGPIOEN) Bit Functions

BIT

NO.

BIT

NAME

RESET

VALUE

FUNCTION

15−6 Reserved 0 Reserved

5−0

GPIOEN13−

GPIOEN8

0

Enable or disable GPIO function of EHPI Control Bus.

GPIOENx = 0 GPIO function of GPIOx line is disabled

GPIOENx = 1 GPIO function of GPIOx line is enabled

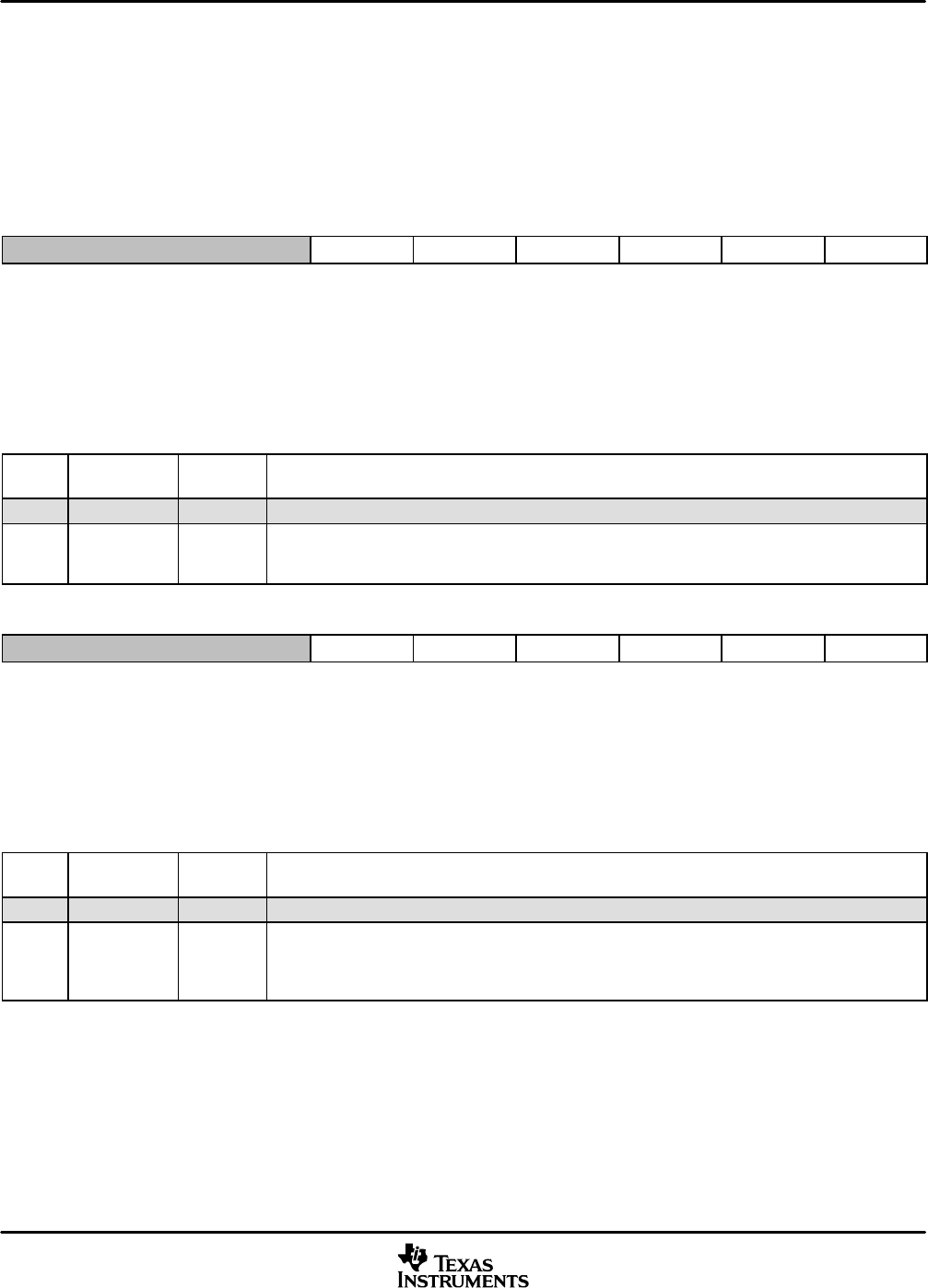

15 6543210

Reserved GPIODIR13 GPIODIR12 GPIODIR11 GPIODIR10 GPIODIR9 GPIODIR8

R, 0000 0000 00 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0

LEGEND: R = Read, W = Write, n = value after reset

Figure 3−14. EHPI GPIO Direction Register (EHPIGPIODIR) Bit Layout

Table 3−15. EHPI GPIO Direction Register (EHPIGPIODIR) Bit Functions

BIT

NO.

BIT

NAME

RESET

VALUE

FUNCTION

15−6 Reserved 0 Reserved

5−0

GPIODIR13−

GPIODIR8

0

Data direction bits that configure the EHPI Control Bus configured as I/O pins as either input or output

pins.

GPIODIRx = 0 Configure corresponding pin as an input.

GPIODIRx = 1 Configure corresponding pin as an output.