Functional Overview

47

November 2002 − Revised January 2005 SPRS205D

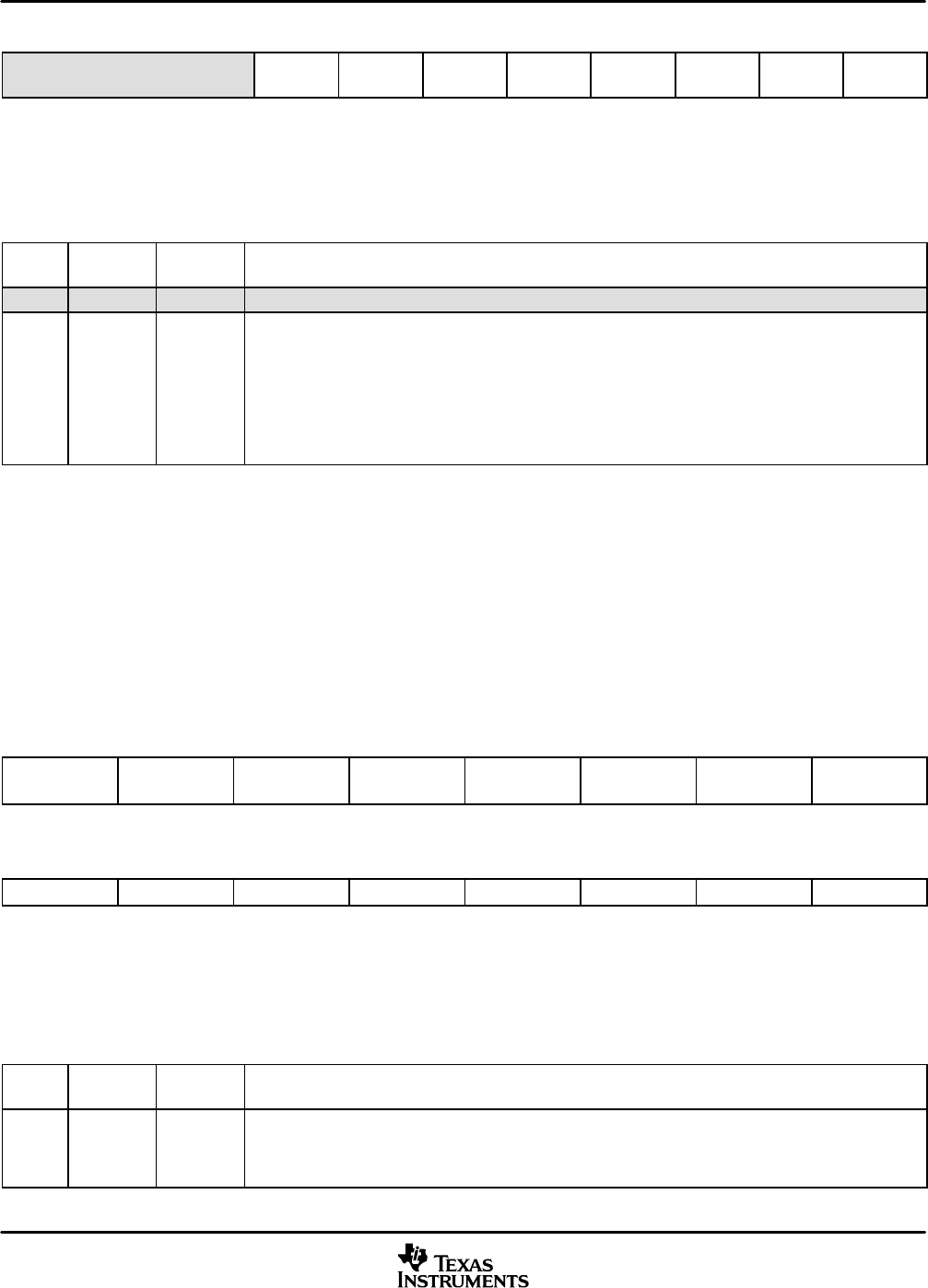

15 876543210

Reserved IO7D IO6D

IO5D

(BGA)

IO4D IO3D IO2D IO1D IO0D

R−00000000 R/W−pin R/W−pin R/W−pin R/W−pin R/W−pin R/W−pin R/W−pin R/W−pin

LEGEND: R = Read, W = Write, pin = value present on the pin (IO7−IO0 default to inputs after reset)

Figure 3−9. I/O Data Register (IODATA) Bit Layout

Table 3−10. I/O Data Register (IODATA) Bit Functions

BIT

NO.

BIT

NAME

RESET

VALUE

FUNCTION

15−8 Reserved 0 These bits are reserved and are unaffected by writes.

7−0 IOxD pin

†‡

IOx Data Bit.

If IOx is configured as an input (IOxDIR = 0 in IODIR):

IOxD = 0 The signal on the IOx pin is low.

IOxD = 1 The signal on the IOx pin is high.

If IOx is configured as an output (IOxDIR = 1 in IODIR):

IOxD = 0 Drive the signal on the IOx pin low.

IOxD = 1 Drive the signal on the IOx pin high.

†

The GPIO5 pin is available on the BGA package only.

‡

pin = value present on the pin (IO7−IO0 default to inputs after reset)

3.6.2 Address Bus General-Purpose I/O

The 16 address signals, EMIF.A[15−0], can also be individually enabled as GPIO when the Parallel Port Mode

bit field of the External Bus Selection Register is set for Data EMIF (00) or Multiplexed EHPI mode (11). These

pins are controlled by three registers: the enable register, AGPIOEN, determines if the pins serve as GPIO

or address (Figure 3−10); the direction register, AGPIODIR, determines if the GPIO enabled pin is an input

or output (Figure 3−11); and the data register, AGPIODATA, determines the logic states of the pins in

general-purpose I/O mode (Figure 3−12). Note that the AGPIOEN bits should be set prior to setting the

AGPIODIR bits.

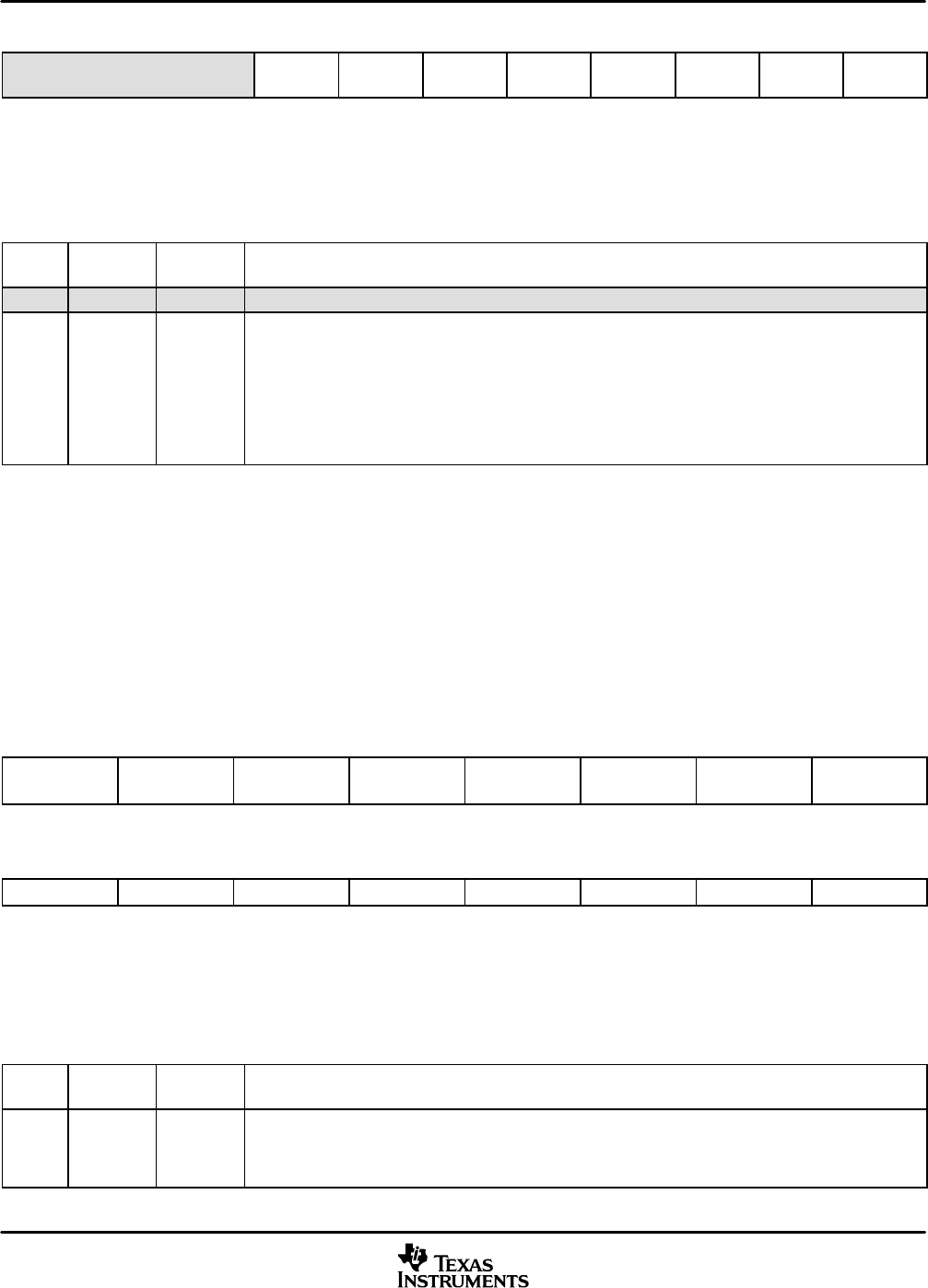

15 14 13 12 11 10 9 8

AIOEN15

(BGA)

AIOEN14

(BGA)

AIOEN13 AIOEN12 AIOEN11 AIOEN10 AIOEN9 AIOEN8

R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0

76543210

AIOEN7 AIOEN6 AIOEN5 AIOEN4 AIOEN3 AIOEN2 AIOEN1 AIOEN0

R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0 R/W, 0

LEGEND: R = Read, W = Write, n = value after reset

Figure 3−10. Address/GPIO Enable Register (AGPIOEN) Bit Layout

Table 3−11. Address/GPIO Enable Register (AGPIOEN) Bit Functions

BIT

NO.

BIT

NAME

RESET

VALUE

FUNCTION

15−0 AIOENx 0

Enable or disable GPIO function of Address Bus of EMIF. AIOEN15 and AIOEN14 are only available in

BGA package.

AIOENx = 0 GPIO function of Ax line is disabled; i.e., Ax has address function.

AIOENx = 1 GPIO function of Ax line is enabled; i.e., Ax has GPIO function.