Functional Overview

39

November 2002 − Revised January 2005 SPRS205D

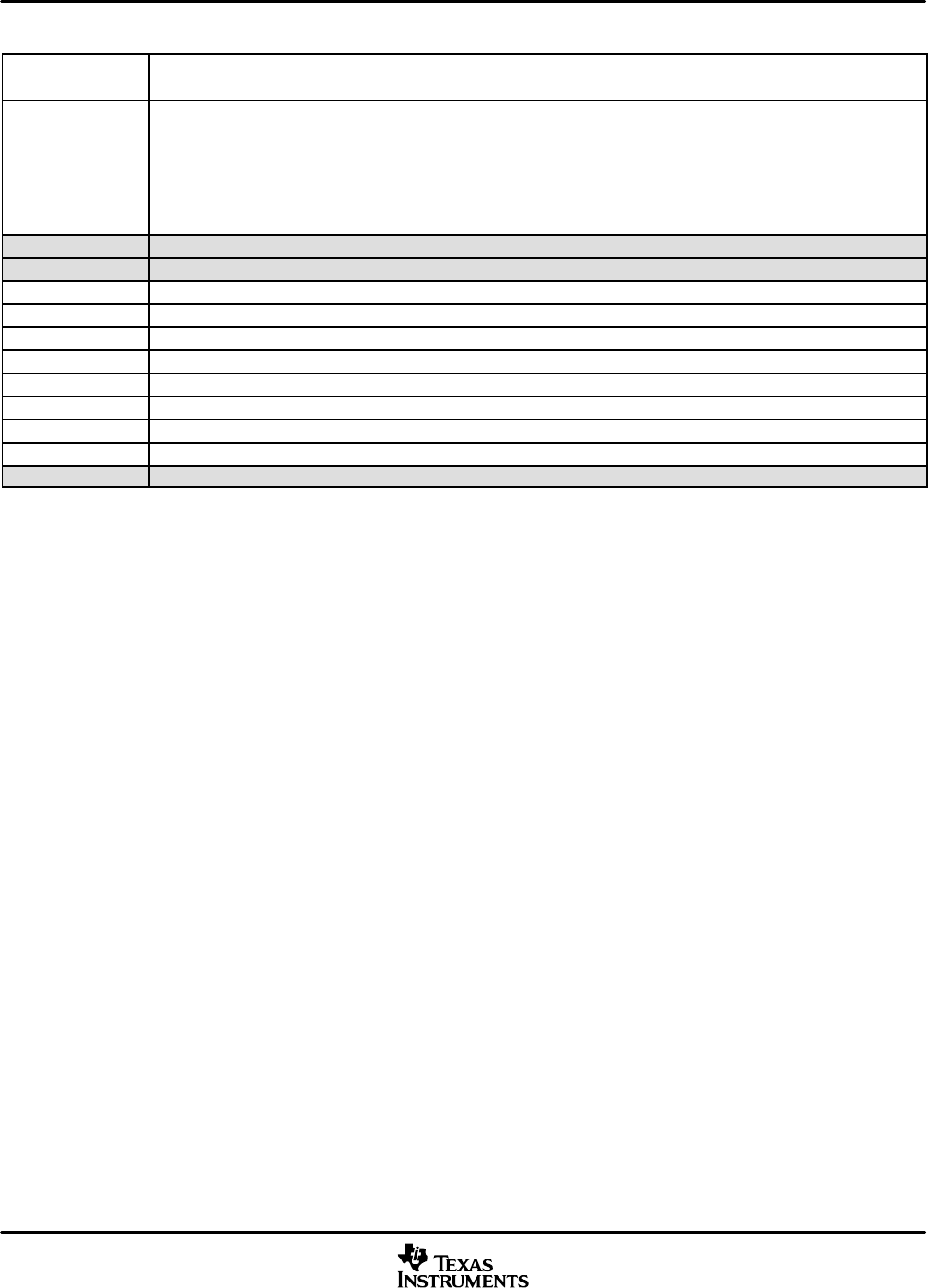

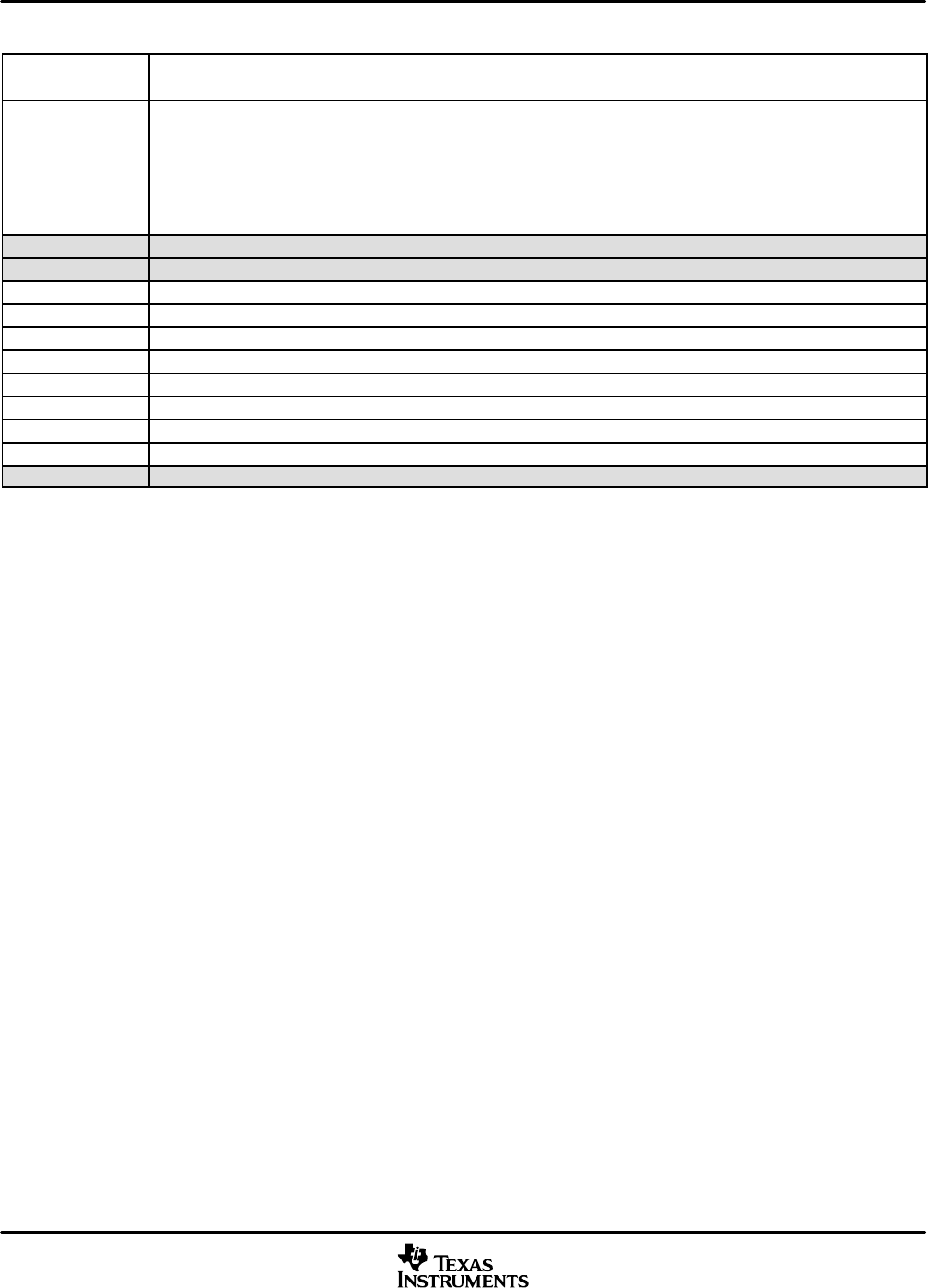

Table 3−4. Synchronization Control Function (Continued)

SYNC FIELD IN

DMA_CCR

SYNCHRONIZATION MODE

01010b

McBSP2/MMC−SD2 Transmit Event

Serial Port 2 Mode:

00 = McBSP2 Transmit Event (XEVT2)

01 = MMC/SD2 Transmit Event (XMMCEVT2)

10 = Reserved

11 = Reserved

01011b Reserved. These bits should always be written with 0.

01100b Reserved. These bits should always be written with 0.

01101b Timer 0 Interrupt Event

01110b Timer 1 Interrupt Event

01111b External Interrupt 0

10000b External Interrupt 1

10001b External Interrupt 2

10010b External Interrupt 3

10011b External Interrupt 4 / I

2

C Receive Event (REVTI2C)

†

10100b I

2

C Transmit Event (XEVTI2C)

Other values Reserved (Do not use these values)

†

The I

2

C receive event (REVTI2C) and external interrupt 4 (INT4) share a synchronization input to the DMA. When the SYNC field of the

DMA_CCR is set to 10011b, the logical OR of these two sources is used for DMA synchronization.

3.4 I

2

C Interface

The TMS320VC5509A includes an I

2

C serial port. The I

2

C port supports:

• Compatible with Philips I

2

C Specification Revision 2.1 (January 2000)

• Operates at 100 Kbps or 400 Kbps

• 7-bit addressing mode

• Master (transmit/receive) and slave (transmit/receive) modes of operation

• Events: DMA, interrupt, or polling

The I

2

C module clock must be in the range from 7 MHz to 12 MHz. This is necessary for proper operation of

the I

2

C module. With the I

2

C module clock in this range, the noise filters on the SDA and SCL pins suppress

noise that has a duration of 50 ns or shorter. The I

2

C module clock is derived from the DSP clock divided by

a programmable prescaler.

NOTE: I/O buffers are not fail-safe. The SDA and SCL pins could potentially draw current if the

device is powered down and SDA and SCL are driven by other devices connected to the I

2

C bus.

3.5 Configurable External Buses

The 5509A offers several combinations of configurations for its external parallel port and two serial ports. This

allows the system designer to choose the appropriate media interface for its application without the need of

a large-pin-count package. The External Bus Selection Register controls the routing of the parallel and serial

port signals.