Functional Overview

36

November 2002 − Revised January 2005SPRS205D

3.1.5 Boot Configuration

The on-chip bootloader provides a method to transfer application code and tables from an external source to

the on-chip RAM memory at power up. These options include:

• Enhanced host-port interface (HPI) in multiplexed or nonmultiplexed mode

• External asynchronous memory boot (via the EMIF) from 8-bit-wide or 16-bit-wide memory

• Serial port boot (from McBSP0) with 8-bit or 16-bit data length

• Serial EPROM boot (from McBSP0) supporting EPROMs with 16-bit or 24-bit address

• USB boot

• I

2

C EEPROM

• Direct execution from external 16-bit-wide asynchronous memory

External pins select the boot configuration. The values of GPIO[3:0] are sampled, following reset, upon

execution of the on-chip bootloader code. It is not possible to disable the bootloader at reset because the

5509A always starts execution from the on-chip ROM following a hardware reset. A summary of boot

configurations is shown in Table 3−3. For more information on using the bootloader, see the Using the

TMS320VC5503/VC5507/VC5509/VC5509A Bootloader Application Report (literature number SPRA375).

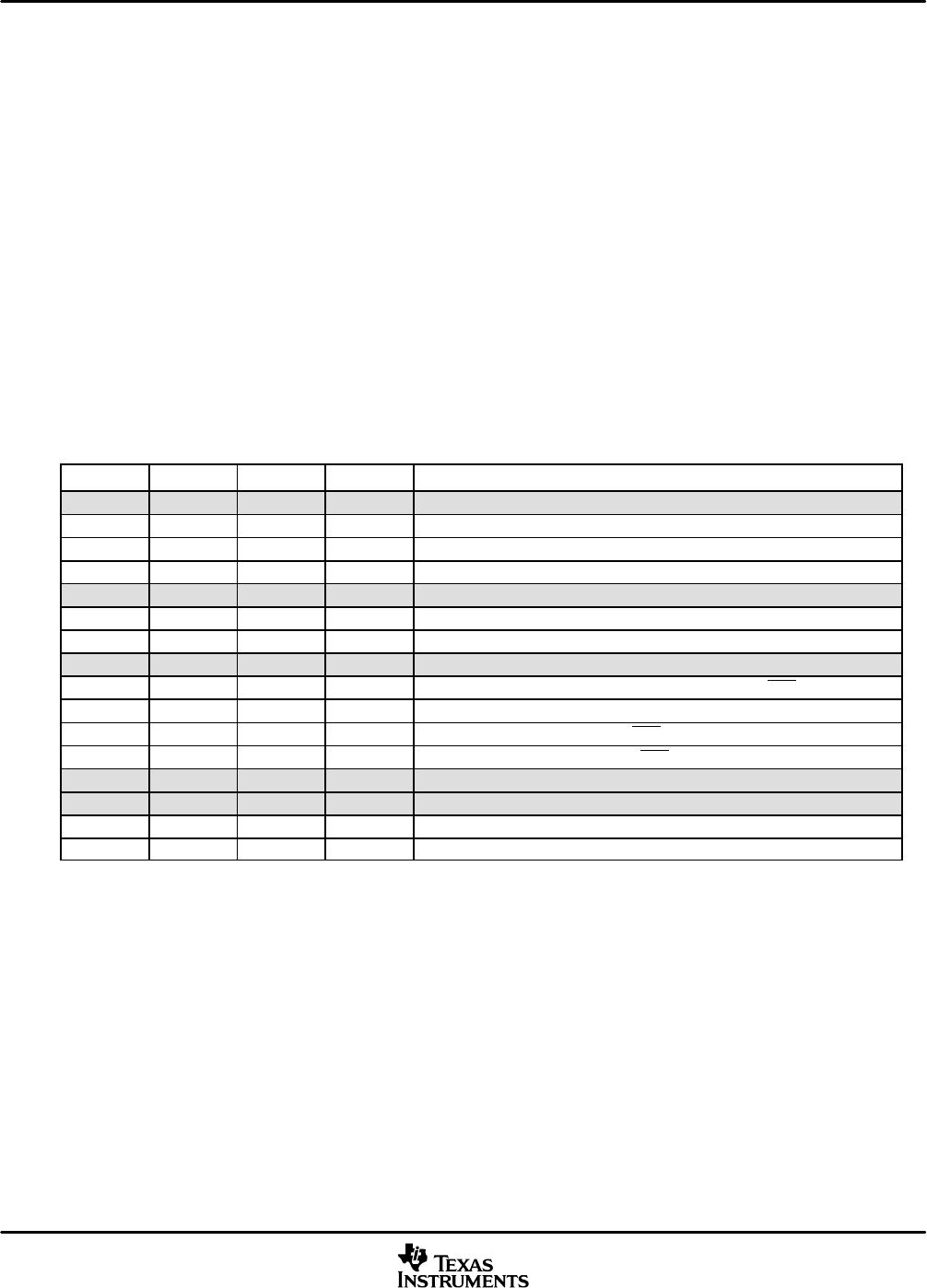

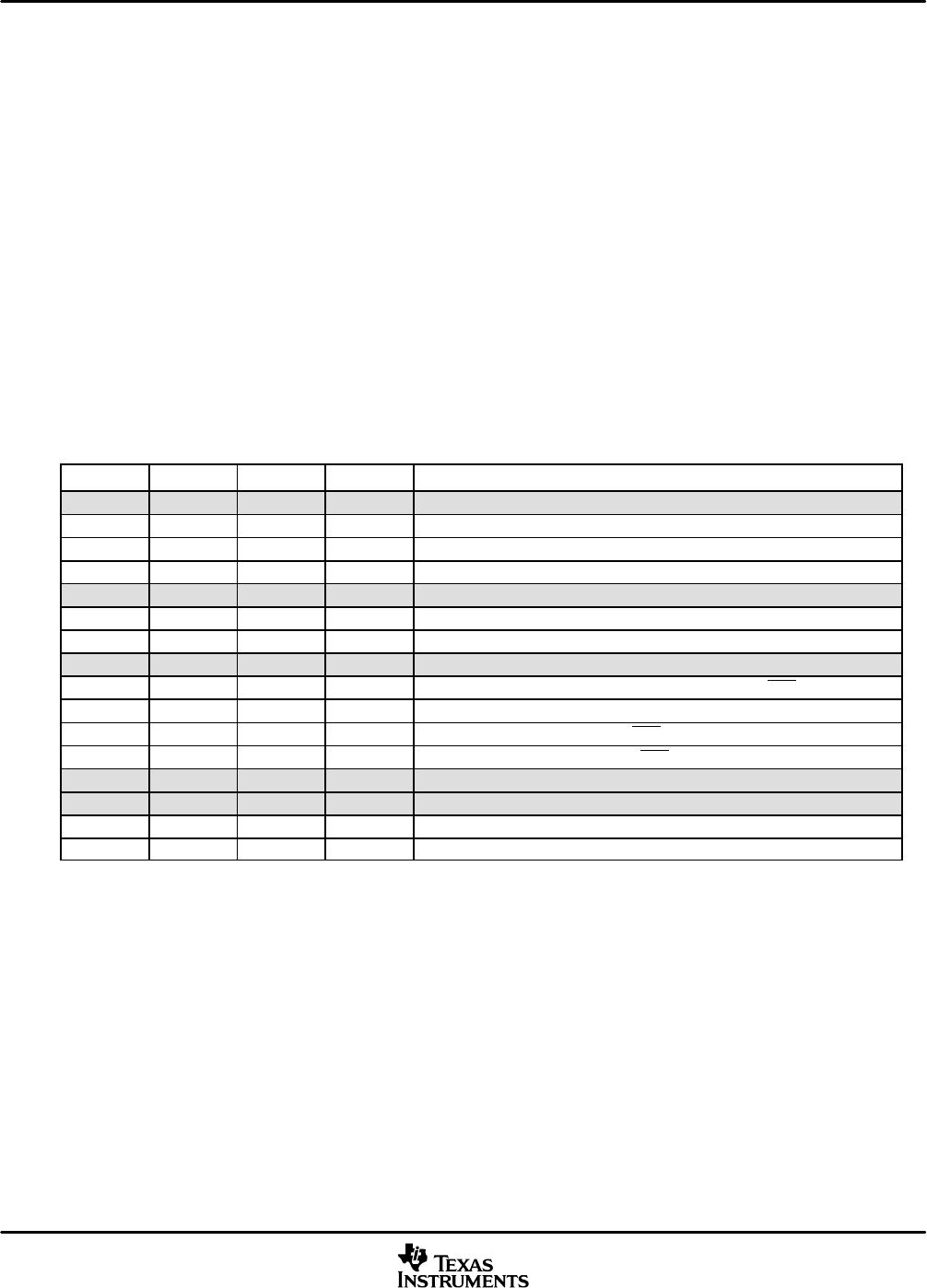

Table 3−3. Boot Configuration Summary

GPIO0 GPIO3 GPIO2

GPIO1

BOOT MODE PROCESS

0 0 0 0 Reserved

0 0 0 1 Serial (SPI) EPROM Boot (24-bit address) via McBSP0

0 0 1 0 USB

0 0 1 1 I

2

C EEPROM (7-bit address)

0 1 0 0 Reserved

0 1 0 1 HPI – multiplexed mode

0 1 1 0 HPI – nonmultiplexed mode

0 1 1 1 Reserved

1 0 0 0 Execute from 16-bit-wide asynchronous memory (on CE1 space)

1 0 0 1 Serial (SPI) EPROM Boot (16-bit address) via McBSP0

1 0 1 0 8-bit asynchronous memory (on CE1 space)

1 0 1 1 16-bit asynchronous memory (on CE1 space)

1 1 0 0 Reserved

1 1 0 1 Reserved

1 1 1 0 Standard serial boot via McBSP0 (16-bit data)

1 1 1 1 Standard serial boot via McBSP0 (8-bit data)