Functional Overview

32

November 2002 − Revised January 2005SPRS205D

3.1 Memory

The 5509A supports a unified memory map (program and data accesses are made to the same physical

space). The total on-chip memory is 320K bytes (128K 16-bit words of RAM and 32K 16-bit words of ROM).

3.1.1 On-Chip Dual-Access RAM (DARAM)

The DARAM is located in the byte address range 000000h−00FFFFh and is composed of eight blocks of

8K bytes each (see Table 3−1). Each DARAM block can perform two accesses per cycle (two reads, two

writes, or a read and a write). DARAM can be accessed by the internal program, data, or DMA buses. The

HPI can only access the first four (32K bytes) DARAM blocks.

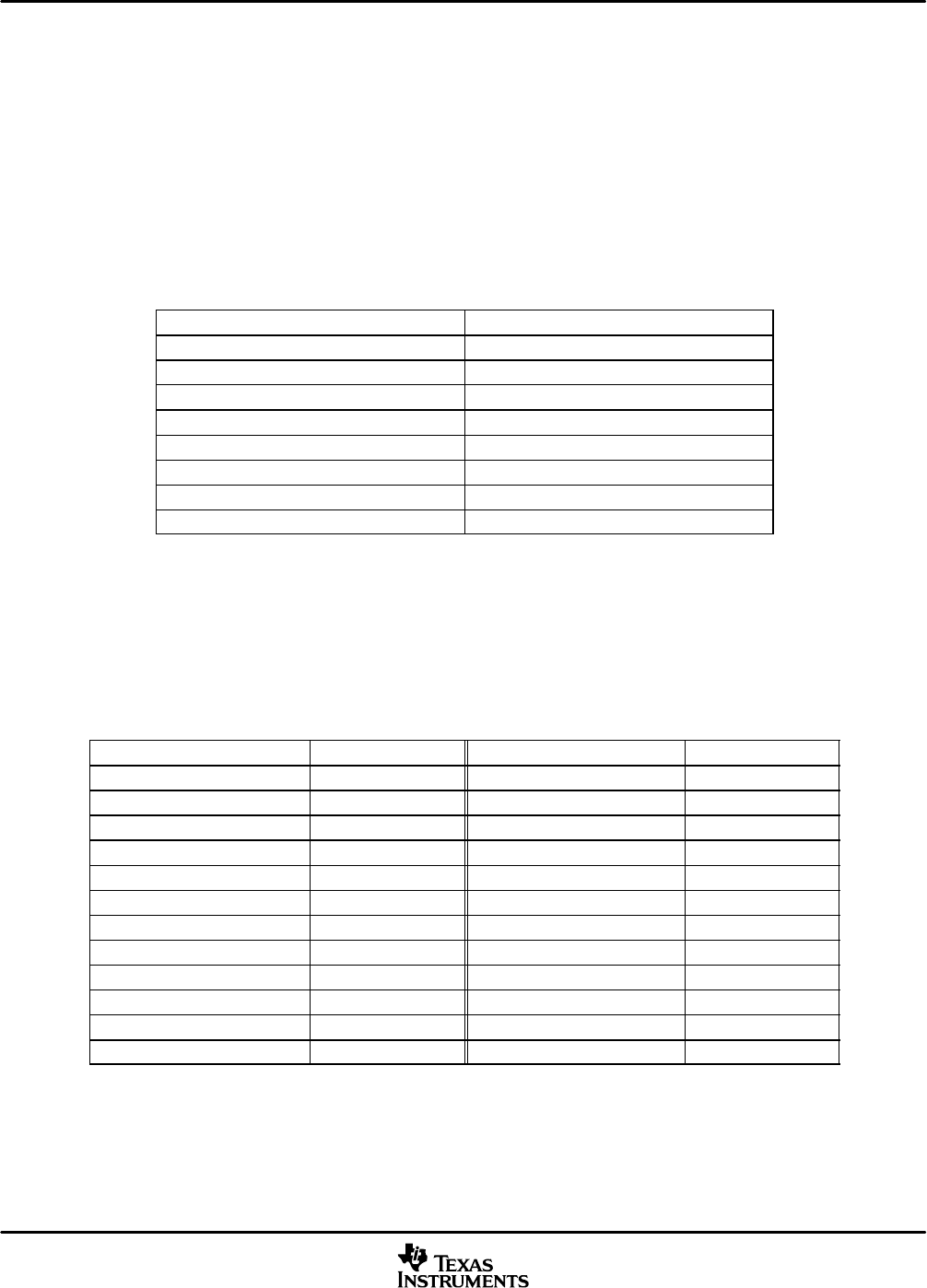

Table 3−1. DARAM Blocks

BYTE ADDRESS RANGE MEMORY BLOCK

000000h − 001FFFh DARAM 0 (HPI accessible)

†

002000h − 003FFFh DARAM 1 (HPI accessible)

004000h − 005FFFh DARAM 2 (HPI accessible)

006000h − 007FFFh DARAM 3 (HPI accessible)

008000h − 009FFFh DARAM 4

00A000h − 00BFFFh DARAM 5

00C000h − 00DFFFh DARAM 6

00E000h − 00FFFFh DARAM 7

†

First 192 bytes are reserved for Memory-Mapped Registers (MMRs).

3.1.2 On-Chip Single-Access RAM (SARAM)

The SARAM is located at the byte address range 010000h−03FFFFh and is composed of 24 blocks of 8K bytes

each (see Table 3−2). Each SARAM block can perform one access per cycle (one read or one write). SARAM

can be accessed by the internal program, data, or DMA buses.

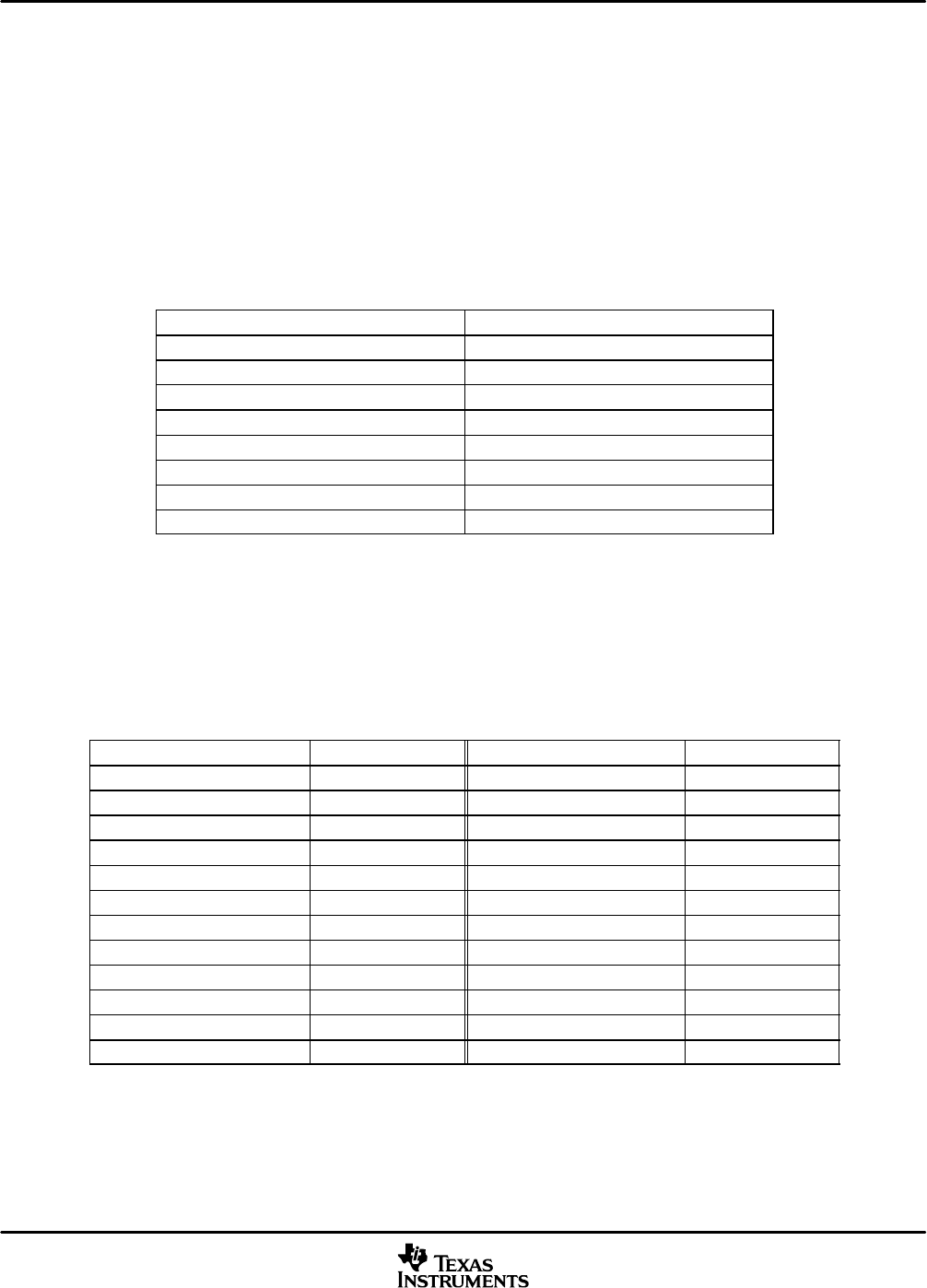

Table 3−2. SARAM Blocks

BYTE ADDRESS RANGE MEMORY BLOCK BYTE ADDRESS RANGE MEMORY BLOCK

010000h − 011FFFh SARAM 0 028000h − 029FFFh SARAM 12

012000h − 013FFFh SARAM 1 02A000h − 02BFFFh SARAM 13

014000h − 015FFFh SARAM 2 02C000h − 02DFFFh SARAM 14

016000h − 017FFFh SARAM 3 02E000h − 02FFFFh SARAM 15

018000h − 019FFFh SARAM 4 030000h − 031FFFh SARAM 16

01A000h − 01BFFFh SARAM 5 032000h − 033FFFh SARAM 17

01C000h − 01DFFFh SARAM 6 034000h − 035FFFh SARAM 18

01E000h − 01FFFFh SARAM 7 036000h − 037FFFh SARAM 19

020000h − 021FFFh SARAM 8 038000h − 039FFFh SARAM 20

022000h − 023FFFh SARAM 9 03A000h − 03BFFFh SARAM 21

024000h − 025FFFh SARAM 10 03C000h − 03DFFFh SARAM 22

026000h − 027FFFh SARAM 11 03E000h − 03FFFFh SARAM 23