TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

29

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

timing registers (continued)

The individual timing parameters can be programmed into the XTIMING registers as described in Table 14.

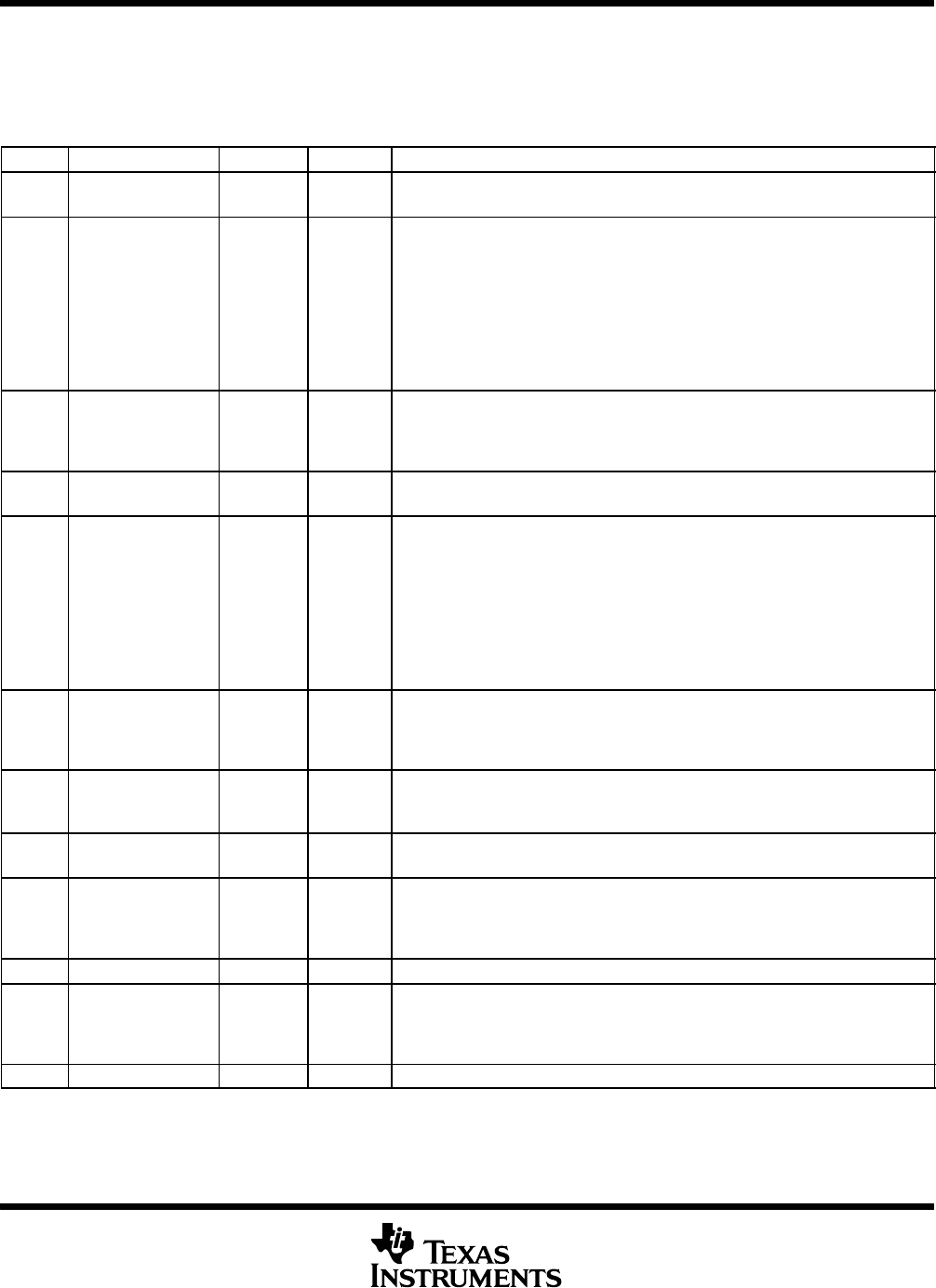

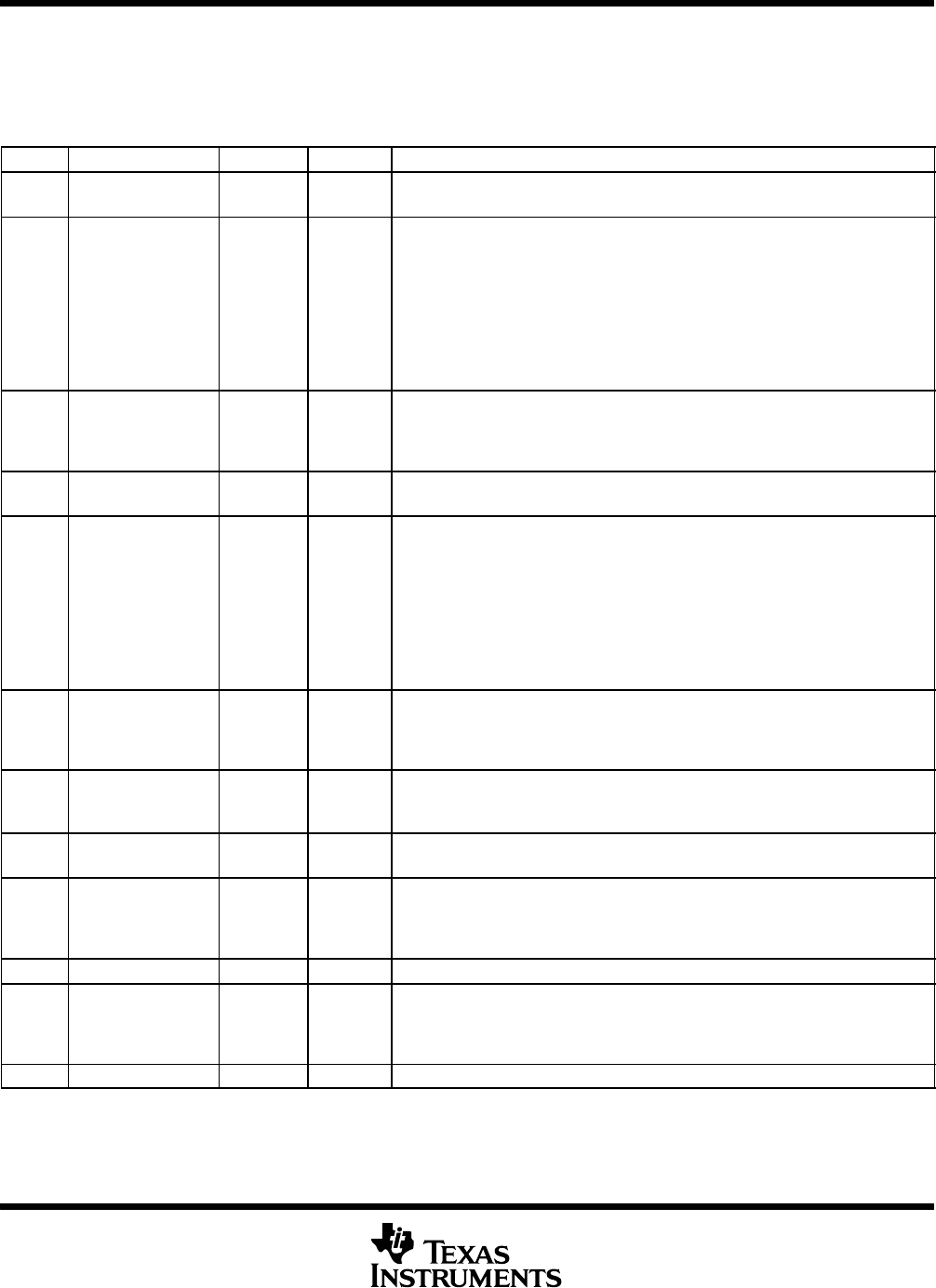

Table 14. XTIMING0/1/2/6/7 Register Bit Definitions

BIT NAME ACCESS RESET DESCRIPTION

1:0 XWRTRAIL R/W 1,1 Two-bit field that defines the write cycle trail period, in XTIMCLK cycles, from

0,1,2,3 (if X2TIMING bit is 0) or 0,2,4,6 (if X2TIMING bit is 1).

4:2 XWRACTIVE R/W 1,1,1 Three-bit field that defines the write cycle active wait-state period, in XTIMCLK

cycles, from 0,1,2,3,4,5,6,7 (if X2TIMING bit is 0) or 0,2,4,6,8,10,12,14 (if

X2TIMING bit is 1).

Notes: 1. If the USEREADY bit is set to 1 (using XREADY),

then XWRACTIVE must be ≥ 1.

2. The active period is by default 1 cycle. Hence the total active period

is 1 + XWRACTIVE value.

6:5 XWRLEAD R/W 1,1 Two-bit field that defines the write cycle lead period, in XTIMCLK cycles, from 1,2,3

(if X2TIMING bit is 0) or 2,4,6 (if X2TIMING bit is 1).

Note: XWRLEAD must be ≥ 1.

8:7 XRDTRAIL R/W 1,1 Two-bit field that defines the read cycle trail period, in XTIMCLK cycles, from

0,1,2,3 (if X2TIMING bit is 0) or 0,2,4,6 (if X2TIMING bit is 1).

11:9 XRDACTIVE R/W 1,1,1 Three-bit field that defines the read cycle active wait-state period, in XTIMCLK

cycles, from 0,1,2,3,4,5,6,7 (if X2TIMING bit is 0) or 0,2,4,6,8,10,12,14

(if X2TIMING bit is 1).

Notes: 1. If the USEREADY bit is set to 1 (using XREADY),

then XRDACTIVE must be ≥ 1.

2. The active period is by default 1 cycle. Hence the total active period

is 1 + XRDACTIVE value.

13:12 XRDLEAD R/W 1,1 Two-bit field that defines the read cycle lead period, in XTIMCLK cycles, from 1,2,3

(if X2TIMING bit is 0) or 2,4,6 (if X2TIMING bit is 1).

Note: XRDLEAD must be ≥ 1.

14 USEREADY R/W 1 When set, the XREADY signal can be used to further extend the active portion of

the cycle past the minimum defined by the XRDACTIVE and XWRACTIVE fields.

When cleared XREADY is ignored.

15 READYMODE R/W 1 When set, the XREADY input is asynchronous. When cleared, the XREADY input

is synchronous.

17:16 Reserved R/W 1,1 Reserved.

These two bits must always be written to as 1,1. Any other combination is reserved

and will result in incorrect XINTF behavior.

21:18 Reserved R 0 Reserved

22 X2TIMING R/W 1 This bit specifies the scaling factor of the LEAD, ACTIVE, TRAIL values in the

individual timing registers. If this bit is 0, the values are scaled 1:1. If this bit is 1,

the values are scaled 2:1 (doubled). The default mode of operation on power up

and reset is 2:1 scaling (doubled) mode.

31:23 Reserved R 0

PR

DU

T PREVIEW