TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

86

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

GPIO mux (continued)

If configured for ”Digital I/O” mode, additional registers are provided for setting individual I/O signals (via the

GPxSET registers), for clearing individual I/O signals (via the GPxCLEAR registers), for toggling individual I/O

signals (via the GPxTOGGLE registers), or for reading/writing to the individual I/O signals (via the GPxDAT

registers). Table 61 lists the GPIO Data Registers.

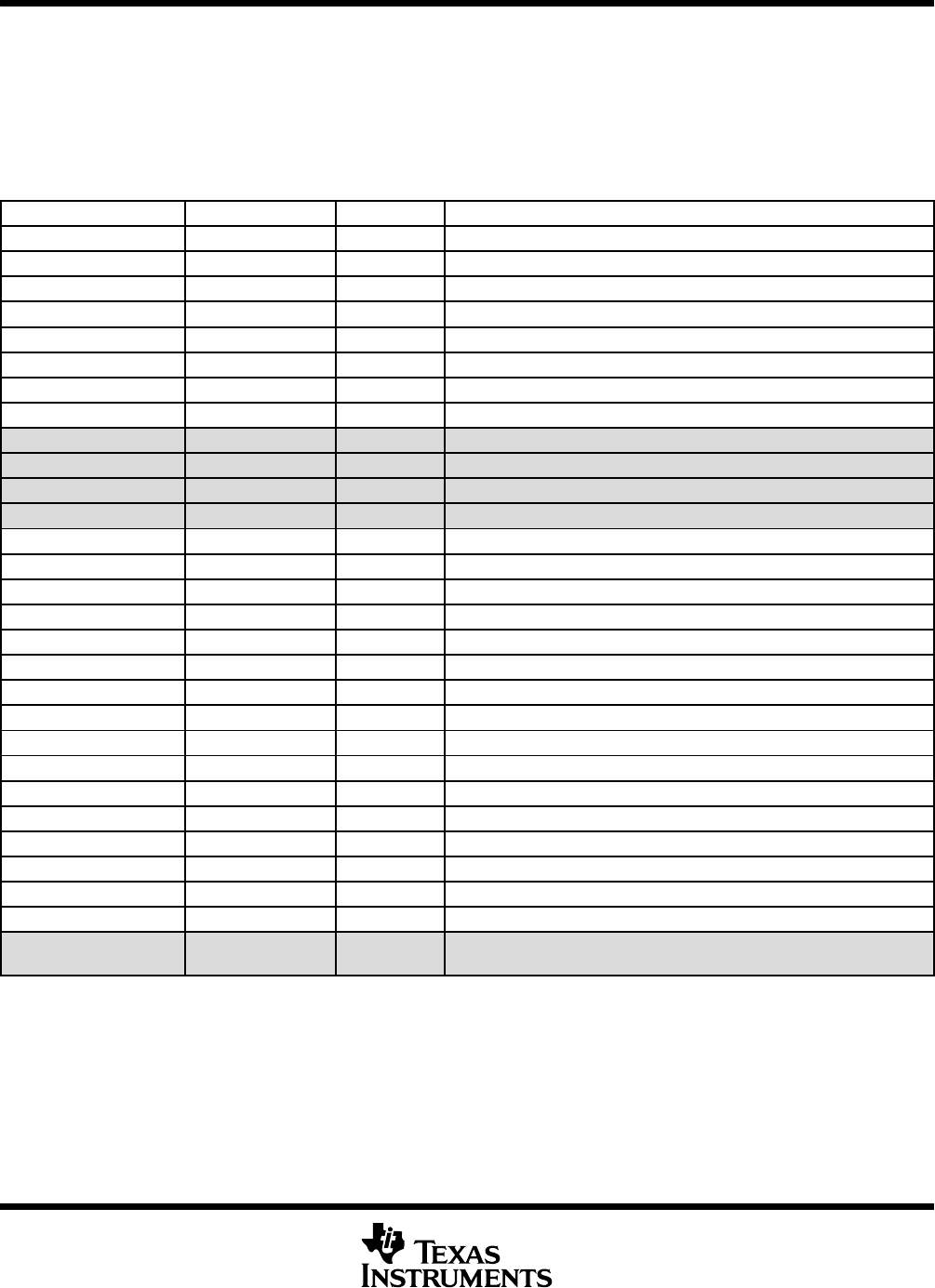

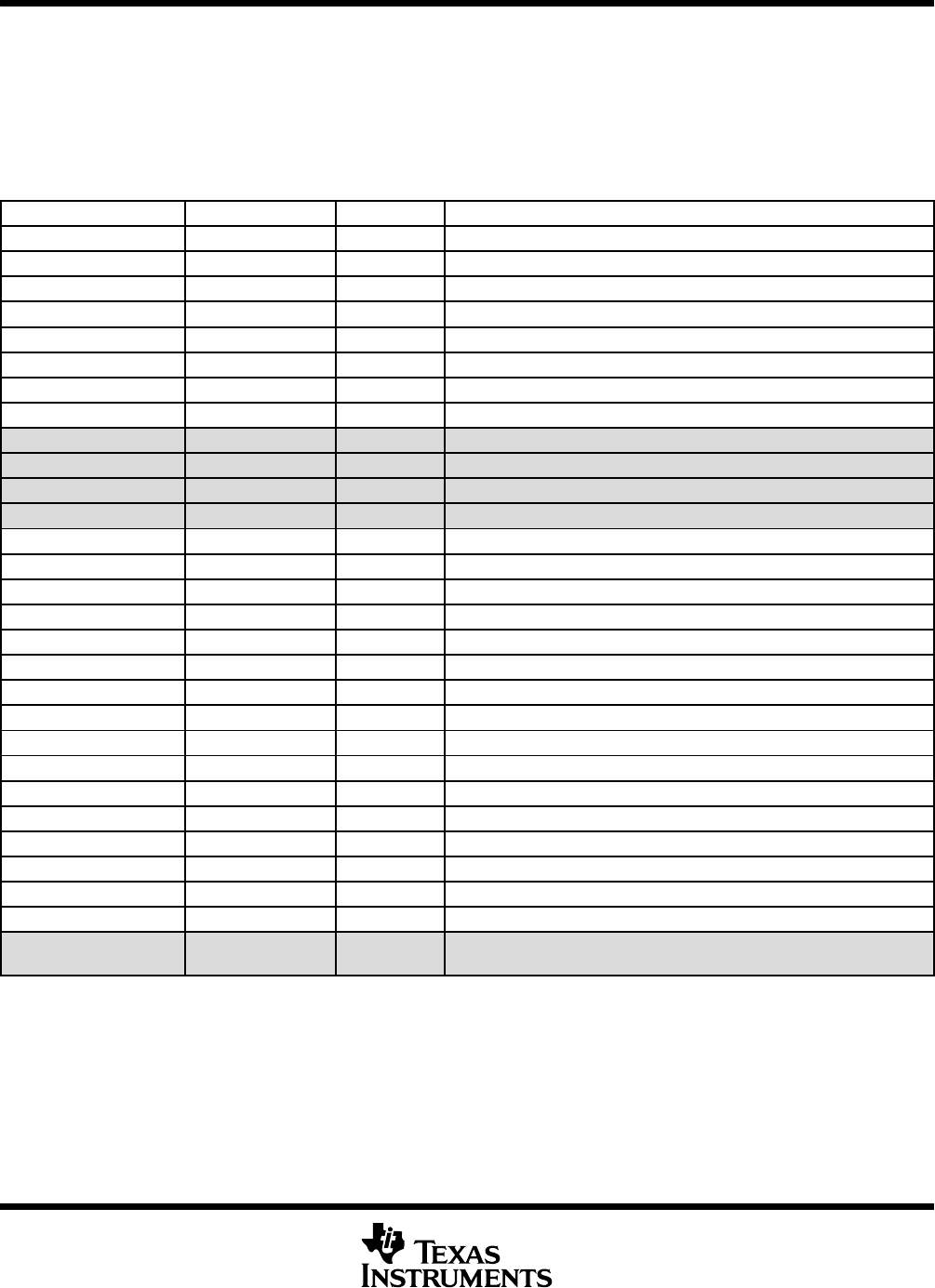

Table 61. GPIO Data Registers

†‡

NAME ADDRESS SIZE (x16) REGISTER DESCRIPTION

GPADAT 0x0000–70E0 1 GPIO A Data Register

GPASET 0x0000–70E1 1 GPIO A Set Register

GPACLEAR 0x0000–70E2 1 GPIO A Clear Register

GPATOGGLE 0x0000–70E3 1 GPIO A Toggle Register

GPBDAT 0x0000–70E4 1 GPIO B Data Register

GPBSET 0x0000–70E5 1 GPIO B Set Register

GPBCLEAR 0x0000–70E6 1 GPIO B Clear Register

GPBTOGGLE 0x0000–70E7 1 GPIO B Toggle Register

reserved 0x0000–70E8 1

reserved 0x0000–70E9 1

reserved 0x0000–70EA 1

reserved 0x0000–70EB 1

GPDDAT 0x0000–70EC 1 GPIO D Data Register

GPDSET 0x0000–70ED 1 GPIO D Set Register

GPDCLEAR 0x0000–70EE 1 GPIO D Clear Register

GPDTOGGLE 0x0000–70EF 1 GPIO D Toggle Register

GPEDAT 0x0000–70F0 1 GPIO E Data Register

GPESET 0x0000–70F1 1 GPIO E Set Register

GPECLEAR 0x0000–70F2 1 GPIO E Clear Register

GPETOGGLE 0x0000–70F3 1 GPIO E Toggle Register

GPFDAT 0x0000–70F4 1 GPIO F Data Register

GPFSET 0x0000–70F5 1 GPIO F Set Register

GPFCLEAR 0x0000–70F6 1 GPIO F Clear Register

GPFTOGGLE 0x0000–70F7 1 GPIO F Toggle Register

GPGDAT 0x0000–70F8 1 GPIO G Data Register

GPGSET 0x0000–70F9 1 GPIO G Set Register

GPGCLEAR 0x0000–70FA 1 GPIO G Clear Register

GPGTOGGLE 0x0000–70FB 1 GPIO G Toggle Register

reserved 0x0000–70FC

0x0000–70FF

4

†

Reserved locations will return undefined values and writes will be ignored.

‡

These registers are NOT EALLOW protected. The above registers will typically be accessed regularly by the user.

PR

DU

T PREVIEW