TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

74

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

enhanced controller area network (eCAN) module (continued)

The CAN registers listed in Table 55 are used by the CPU to configure and control the CAN controller and the

message objects.

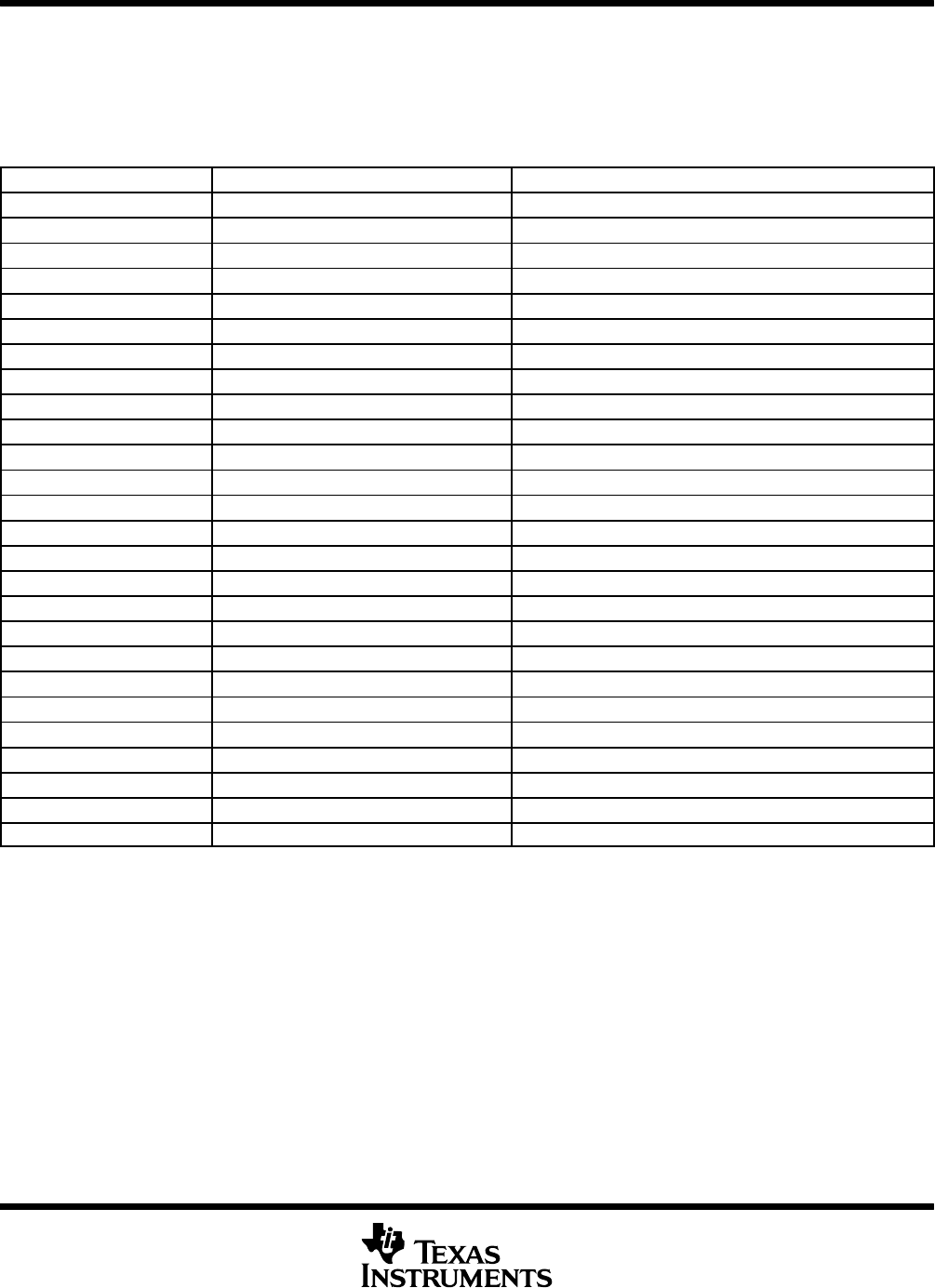

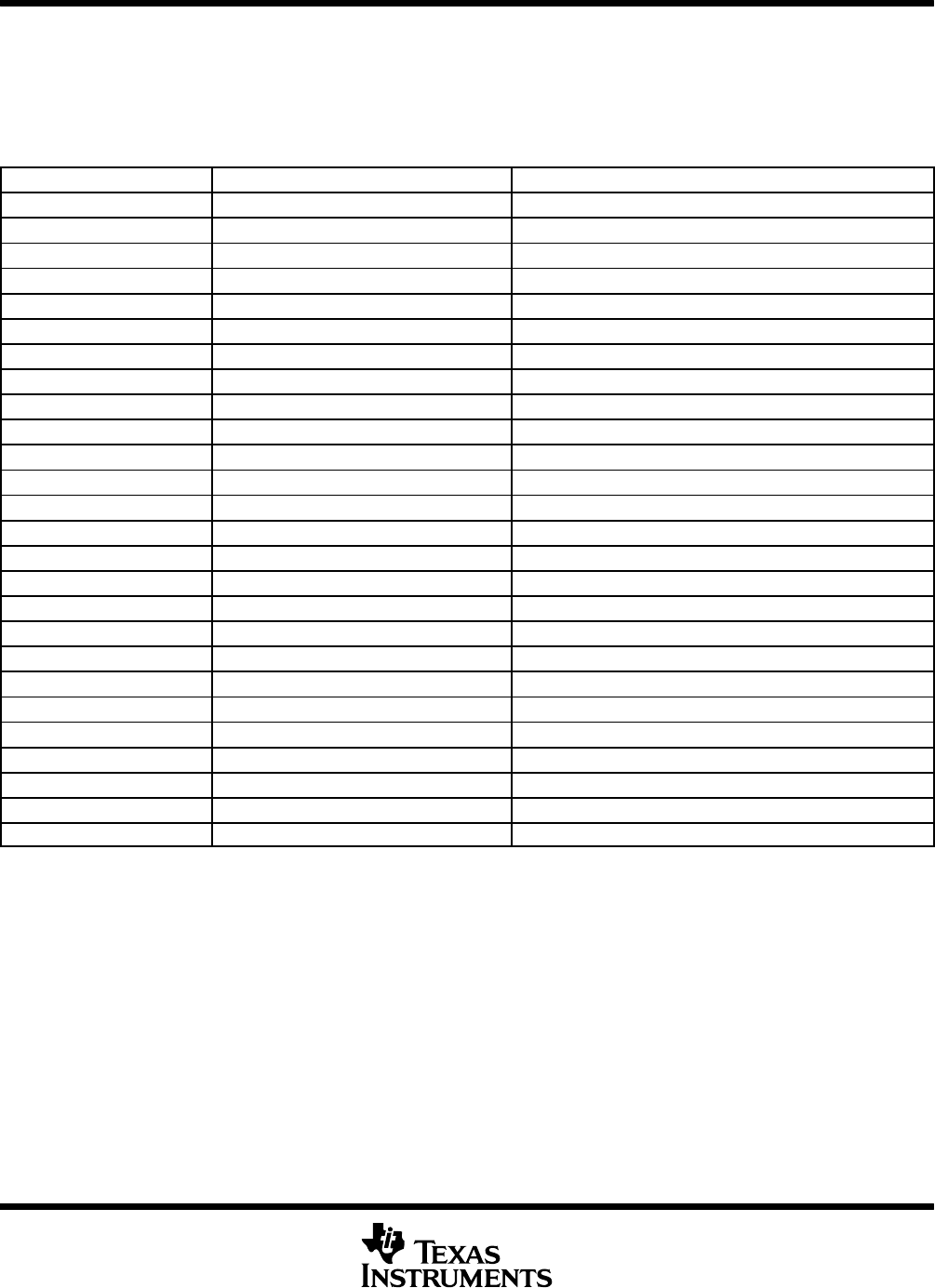

Table 55. CAN Registers Map

†

REGISTER NAME ADDRESS DESCRIPTION

CANME 0x00 6000 Mailbox enable

CANMD 0x00 6002 Mailbox direction

CANTRS 0x00 6004 Transmit request set

CANTRR 0x00 6006 Transmit request reset

CANTA 0x00 6008 Transmission acknowledge

CANAA 0x00 600A Abort acknowledge

CANRMP 0x00 600C Receive message pending

CANRML 0x00 600E Receive message lost

CANRFP 0x00 6010 Remote frame pending

Reserved 0x00 6012 Reserved

CANMC 0x00 6014 Master control

CANBTC 0x00 6016 Bit-timing configuration

CANES 0x00 6018 Error and status

CANTEC 0x00 601A Transmit error counter

CANREC 0x00 601C Receive error counter

CANGIF0 0x00 601E Global interrupt flag 0

CANGIM 0x00 6020 Global interrupt mask

CANGIF1 0x00 6022 Global interrupt flag 1

CANMIM 0x00 6024 Mailbox interrupt mask

CANMIL 0x00 6026 Mailbox interrupt level

CANOPC 0x00 6028 Overwrite protection control

CANTIOC 0x00 602A TX I/O control

CANRIOC 0x00 602C RX I/O control

CANLNT 0x00 602E Local network time (Reserved in SCC mode)

CANTOC 0x00 6030 Time-out control (Reserved in SCC mode)

CANTOS 0x00 6032 Time-out status (Reserved in SCC mode)

†

These registers are mapped to Peripheral Frame 1. This space allows 16-bit and 32-bit accesses.

PR

DU

T PREVIEW