TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

70

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

enhanced analog-to-digital converter (ADC) module (continued)

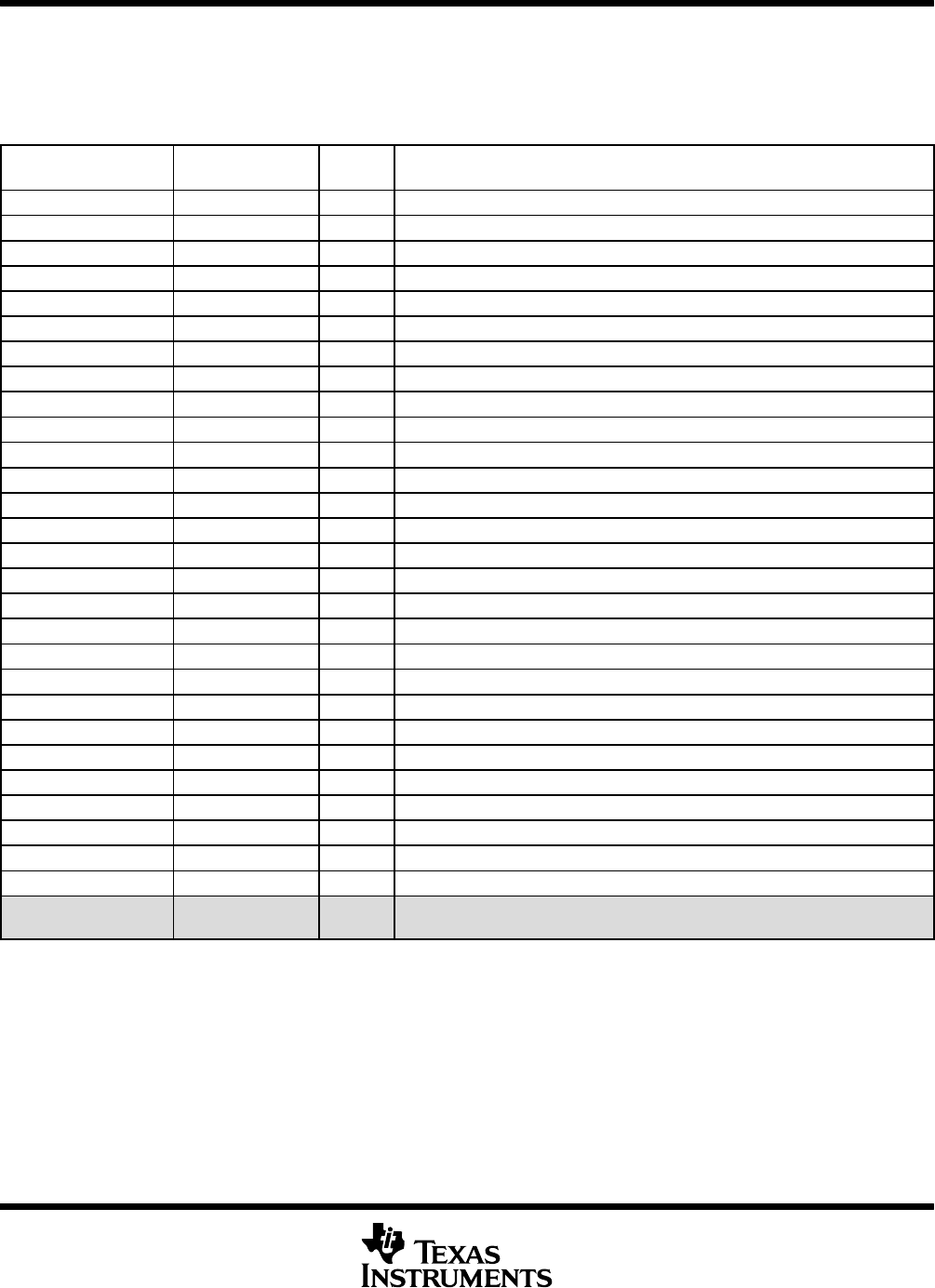

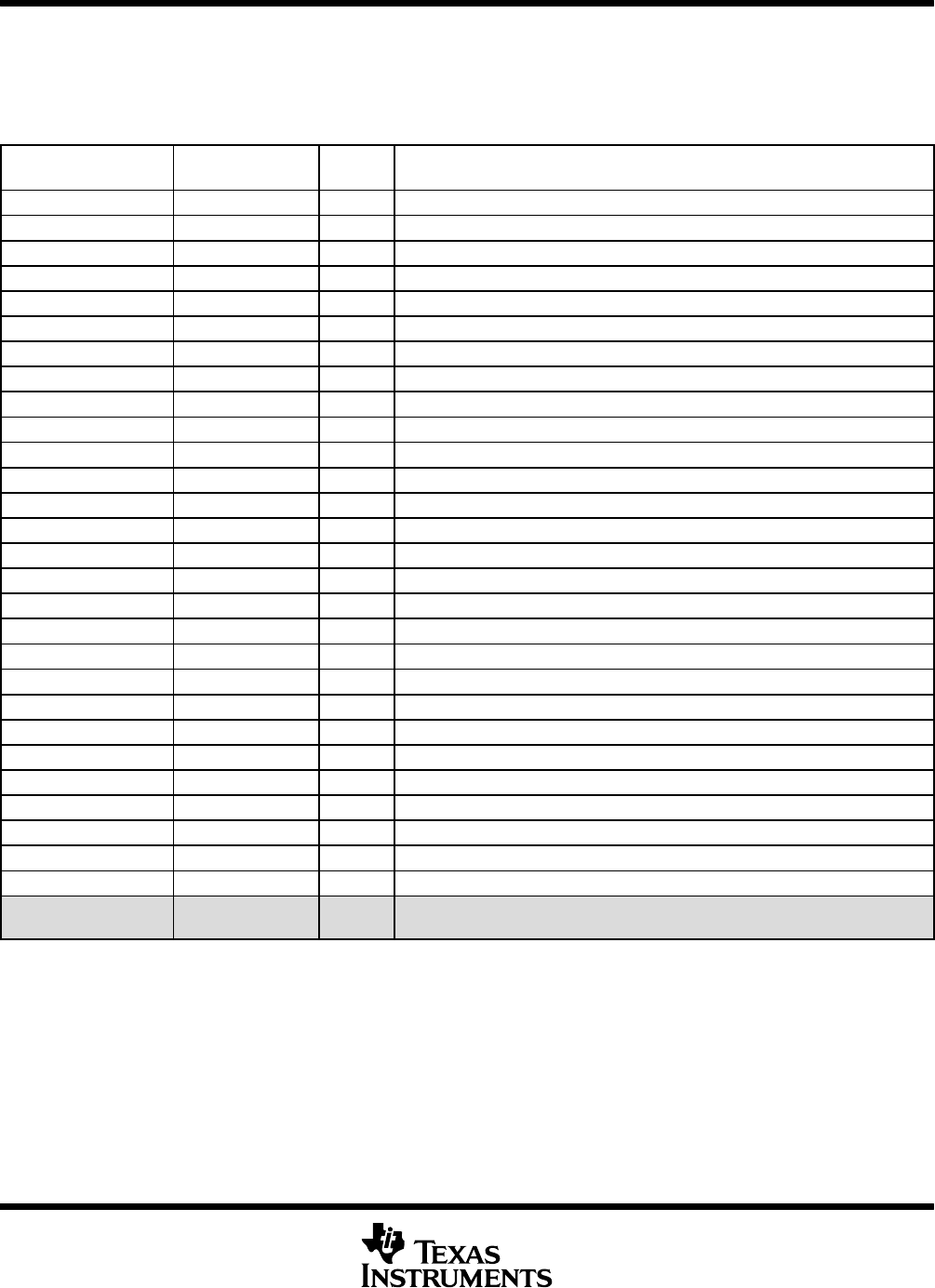

The ADC operation is configured, controlled, and monitored by the registers listed in Table 54.

Table 54. ADC Registers

†

NAME

ADDRESS

RANGE

SIZE

(x16)

DESCRIPTION

ADCTRL1 0x0000–7100 1 ADC Control Register 1

ADCTRL2 0x0000–7101 1 ADC Control Register 2

ADCMAXCONV 0x0000–7102 1 ADC Maximum Conversion Channels Register

ADCCHSELSEQ1 0x0000–7103 1 ADC Channel Select Sequencing Control Register 1

ADCCHSELSEQ2 0x0000–7104 1 ADC Channel Select Sequencing Control Register 2

ADCCHSELSEQ3 0x0000–7105 1 ADC Channel Select Sequencing Control Register 3

ADCCHSELSEQ4 0x0000–7106 1 ADC Channel Select Sequencing Control Register 4

ADCASEQSR 0x0000–7107 1 ADC Auto–Sequence Status Register

ADCRESULT0 0x0000–7108 1 ADC Conversion Result Buffer Register 0

ADCRESULT1 0x0000–7109 1 ADC Conversion Result Buffer Register 1

ADCRESULT2 0x0000–710A 1 ADC Conversion Result Buffer Register 2

ADCRESULT3 0x0000–710B 1 ADC Conversion Result Buffer Register 3

ADCRESULT4 0x0000–710C 1 ADC Conversion Result Buffer Register 4

ADCRESULT5 0x0000–710D 1 ADC Conversion Result Buffer Register 5

ADCRESULT6 0x0000–710E 1 ADC Conversion Result Buffer Register 6

ADCRESULT7 0x0000–710F 1 ADC Conversion Result Buffer Register 7

ADCRESULT8 0x0000–7110 1 ADC Conversion Result Buffer Register 8

ADCRESULT9 0x0000–7111 1 ADC Conversion Result Buffer Register 9

ADCRESULT10 0x0000–7112 1 ADC Conversion Result Buffer Register 10

ADCRESULT11 0x0000–7113 1 ADC Conversion Result Buffer Register 11

ADCRESULT12 0x0000–7114 1 ADC Conversion Result Buffer Register 12

ADCRESULT13 0x0000–7115 1 ADC Conversion Result Buffer Register 13

ADCRESULT14 0x0000–7116 1 ADC Conversion Result Buffer Register 14

ADCRESULT15 0x0000–7117 1 ADC Conversion Result Buffer Register 15

ADCCALOFF0 0x0000–7118 1 ADC Calibration Offset Result 0

ADCCALOFF1 0x0000–7119 1 ADC Calibration Offset Result 1

ADCTRL3 0x0000–711A 1 ADC Control Register 3

ADCST 0x0000–711B 1 ADC Status Register

reserved 0x0000–711C

0x0000–711F

4

†

The above registers are mapped to peripheral bus 16 space. This space only allows 16-bit accesses. 32-bit accesses produce undefined results.

PR

DU

T PREVIEW