TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

63

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

event manager modules (EVA, EVB) (continued)

EXTCONA is an added control register to enable and disable the added/modified features. It is required for

compatibility with 24x EV. EXTCONA enables and disables the additions and modifications in features. All

additions and modifications are disabled by default to keep compatibility with 24x EV (see Table 53).

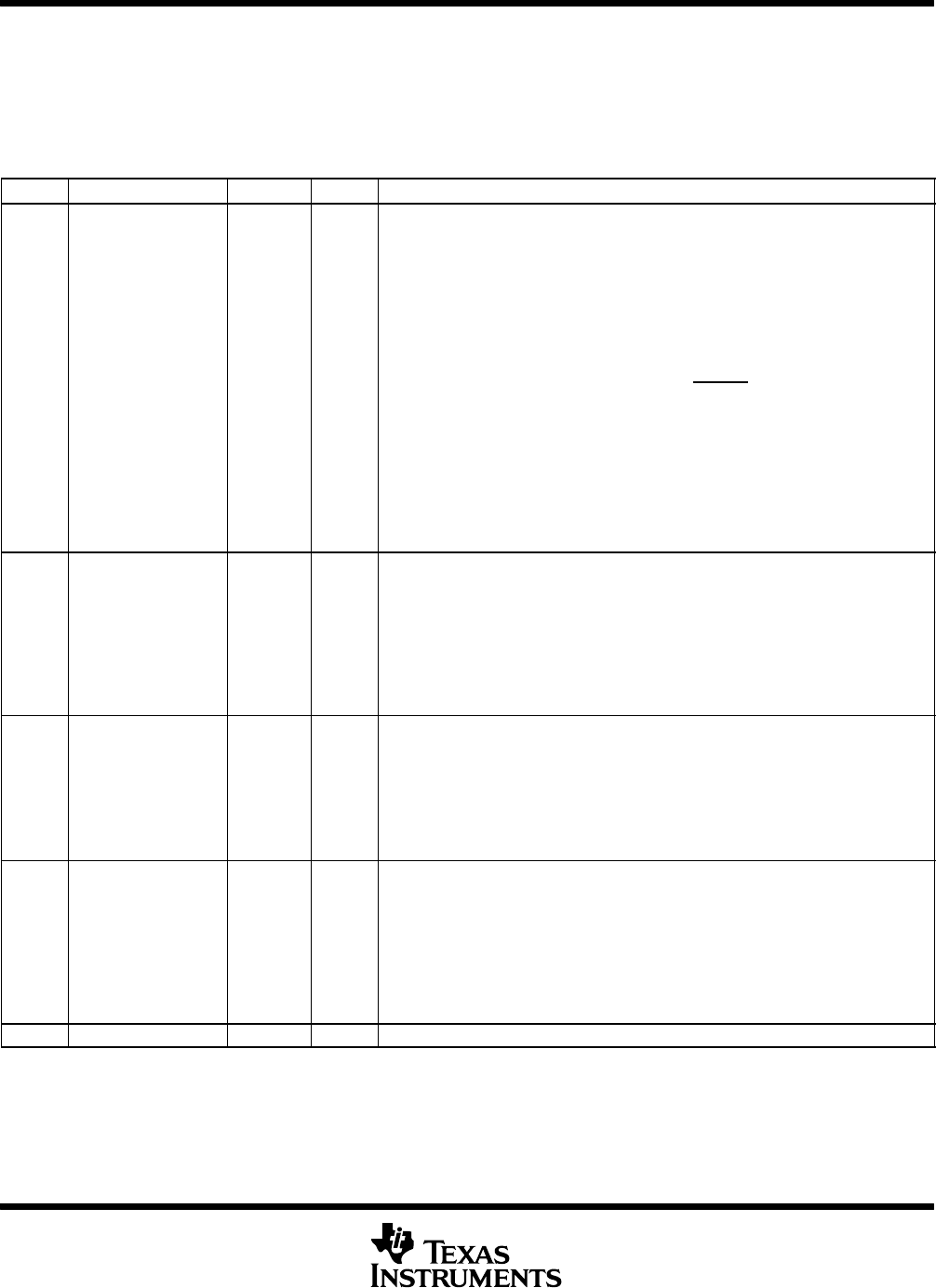

Table 53. EXTCONA Register Bit Definitions

BIT(S) NAME TYPE RESET DESCRIPTION

0 INDCOE R/W 0 Independent Compare Output Enable Mode: This bit, when set to one, allows

compare outputs to be enabled and disabled independently.

0

1

Independent Compare Output Enable mode is disabled. Time 1 and 2

compare outputs are enabled and disabled at the same time by

GPTCONA(6). Full Compare 1, 2, and 3 outputs are enabled and disabled

at the same time by COMCONA(9). GPTCONA(12,11,5,4) and

COMCONA(7:5, 2:0) are reserved. EVIFRA(0) enables and disables all

the compare outputs at the same time. EVIMR(0) enables and disables

PDP interrupt and the direct path of PDPINT

signal at the same time.

Independent Compare Output Enable mode is enabled. Compare outputs

are enabled and disabled respectively by GPTCONA(5,4) and

COMCONA(7:5). Compare trips are enabled and disabled respectively

by GPTCONA(12,11) and COMCONA(2:0). GPTCONA(6) and

COMCONA(9) are reserved. EVIFRA[0] is set to one when any trip input

is low and is also enabled. EVIMRA(0) functions only as interrupt enable

and disable.

1 QEPIQUAL R/W 0 QEP/CAP3 Index Qualification Mode: This bit turns on and off QEP index

qualifier.

0

1

QEPI/CAP3 qualification mode is off. QEPI/CAP3 is allowed to pass the

qualifier unaffected.

QEPI/CAP3 qualification mode is on. A zero-to-one transition is allowed

to pass the qualifier only when both QEPA and QEPB are high. Otherwise

the output of the qualifier stays low.

2 QEPIE R/W 0 QEP Index Enable: This bit enables and disables the QEPI input. The QEPI input

when enabled can cause Timer 2 to reset:

0

1

Disable QEPI. Transitions on QEPI don’t affect Timer 2.

Enable QEPI. Either a zero-to-one transition on QEPI alone (when

EXTCONA[1] = 0), or a zero-to-one transition plus QEPA and QEPB are

both high (when EXTCONA[1] = 1), causes Timer 2 to reset to zero.

3 EVSOCE R/W 0 EV Start-of-Conversion Output Enable. This bit enables and disables the EV ADC

start-of-conversion output. When enabled, a negative (active-low) pulse of

32 x HSPCLK is generated on selected EV ADC start-of-conversion event. This

bit does not affect the EVTOADC signal routed to the ADC module as optional

SOC trigger.

0

1

Disable EVSOC output. EVSOC is in Hi-Z state.

Enable EVSOC output.

15:4 reserved R = 0 0:0

PR

DU

T PREVIEW