TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

58

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

32-bit CPU-Timers 0/1/2 (continued)

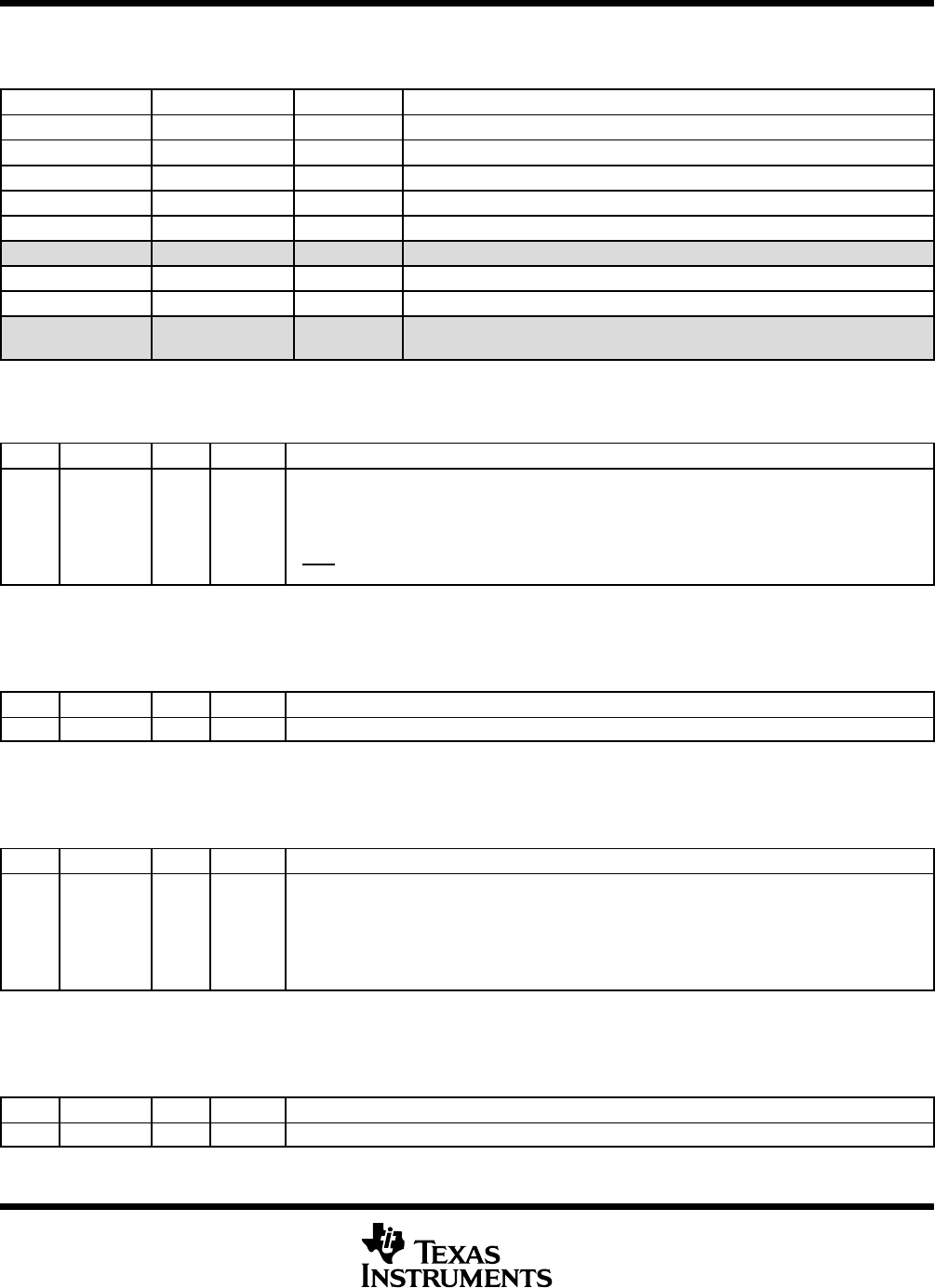

Table 43. CPU-Timers 0, 1, 2 Configuration and Control Registers (Continued)

NAME ADDRESS SIZE (x16) DESCRIPTION

TIMER2TIM 0x0000–0C10 1 CPU-Timer 2, Counter Register

TIMER2TIMH 0x0000–0C11 1 CPU-Timer 2, Counter Register High

TIMER2PRD 0x0000–0C12 1 CPU-Timer 2, Period Register

TIMER2PRDH 0x0000–0C13 1 CPU-Timer 2, Period Register High

TIMER2TCR 0x0000–0C14 1 CPU-Timer 2, Control Register

reserved 0x0000–0C15 1

TIMER2TPR 0x0000–0C16 1 CPU-Timer 2, Prescale Register

TIMER2TPRH 0x0000–0C17 1 CPU-Timer 2, Prescale Register High

reserved 0x0000–0C18

0x0000–0C3F

40

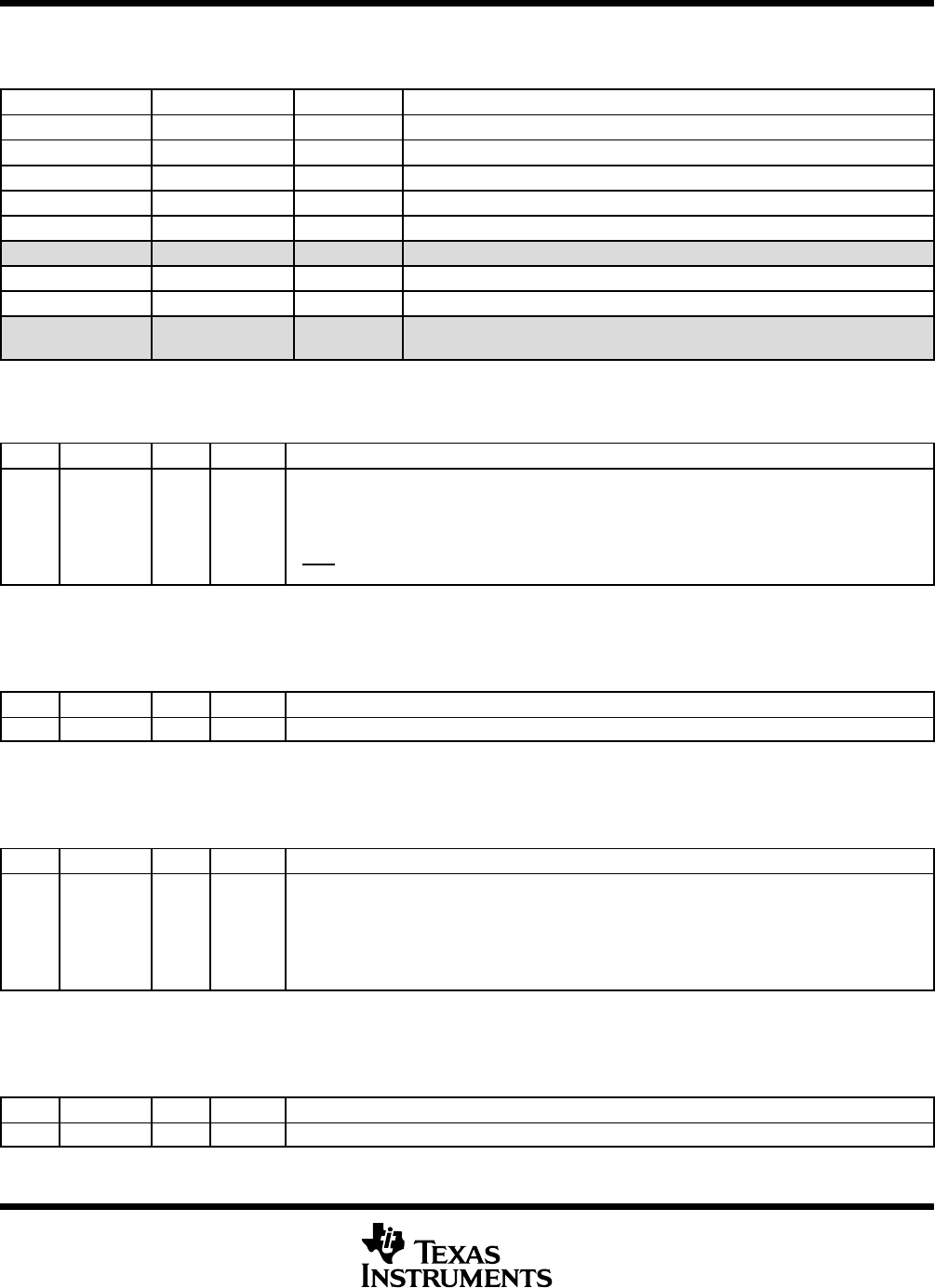

Table 44. TIMERxTIM Register Bit Definitions

†

BITS NAME R/W RESET DESCRIPTION

15:0 TIM R/W 0xFFFF Timer Counter Registers (TIMH:TIM): The TIM register holds the low 16 bits of the current 32-bit

count of the timer. The TIMH register holds the high 16 bits of the current 32-bit count of the timer.

The TIMH:TIM decrements by one every (TDDRH:TDDR+1) clock cycles, where TDDRH:TDDR

is the timer prescale divide-down value. When the TIMH:TIM decrements to zero, the TIMH:TIM

register is reloaded with the period value contained in the PRDH:PRD registers. The timer interrupt

(TINT

) signal is generated.

†

x = 0, 1, or 2

Table 45. TIMERxTIMH Register Bit Definitions

†

BITS NAME R/W RESET DESCRIPTION

15:0 TIMH R/W 0x0000 See description for TIMERxTIM.

†

x = 0, 1, or 2

Table 46. TIMERxPRD Register Bit Definitions

†

BITS NAME R/W RESET DESCRIPTION

15:0 PRD R/W 0xFFFF Timer Period Registers (PRDH:PRD): The PRD register holds the low 16 bits of the 32-bit period.

The PRDH register holds the high 16 bits of the 32-bit period. When the TIMH:TIM decrements to

zero, the TIMH:TIM register is reloaded with the period value contained in the PRDH:PRD

registers, at the start of the next timer input clock cycle (the output of the prescaler). The

PRDH:PRD contents are also loaded into the TIMH:TIM when you set the timer reload bit (TRB)

in the Timer Control Register (TCR).

†

x = 0, 1, or 2

Table 47. TIMERxPRDH Register Bit Definitions

†

BITS NAME R/W RESET DESCRIPTION

15:0 PRDH R/W 0x0000 See description for TIMERxPRD

†

x = 0, 1, or 2

PR

DU

T PREVIEW