TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

46

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

system control (continued)

The PCLKCR1 and PCLKCR2 registers basically enable/disable clocks to the various peripheral modules in

the F2810 and F2812 devices. Table 32 lists the bit descriptions of the PCLKCR1 and PCLKCR2 registers.

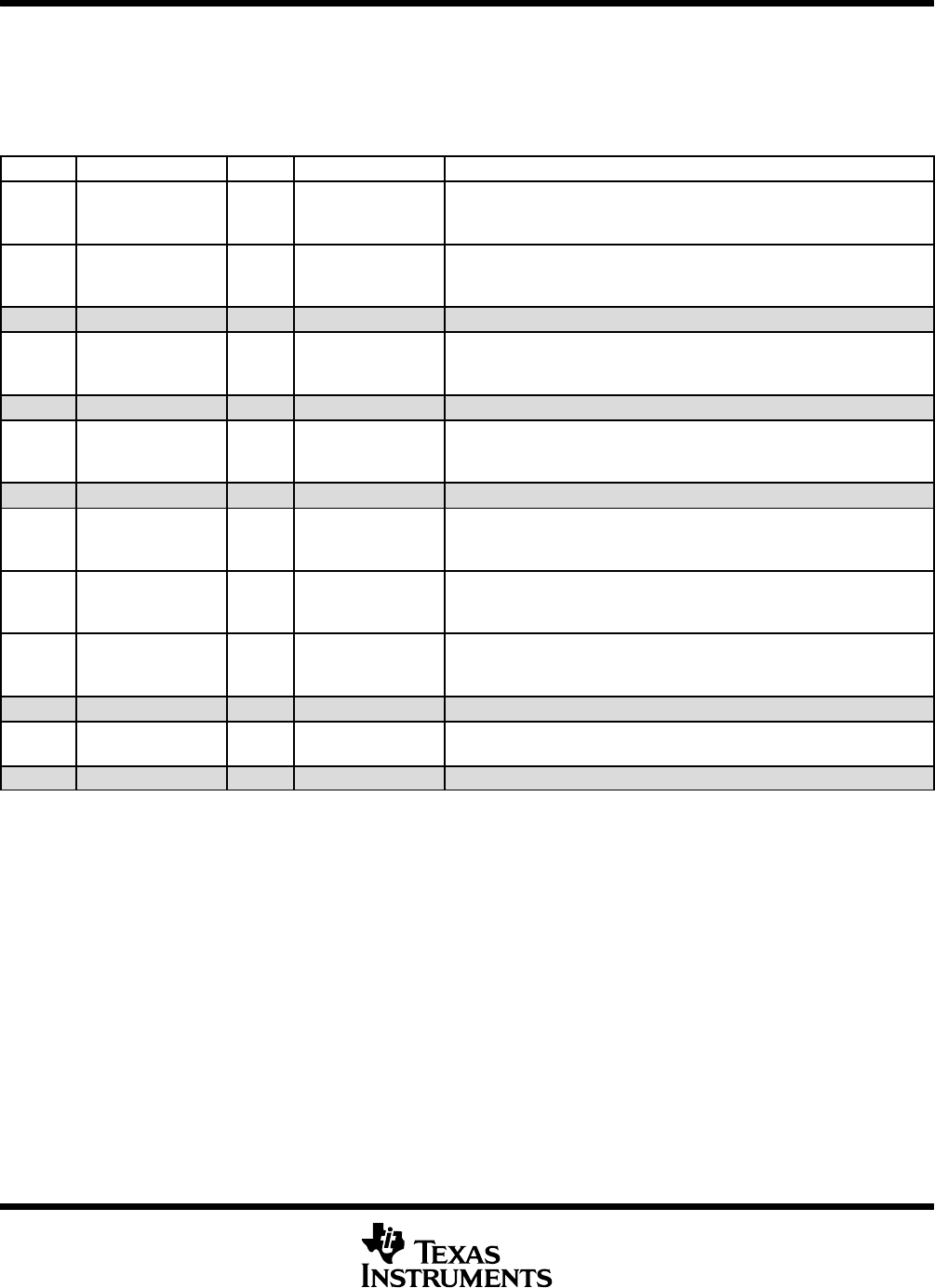

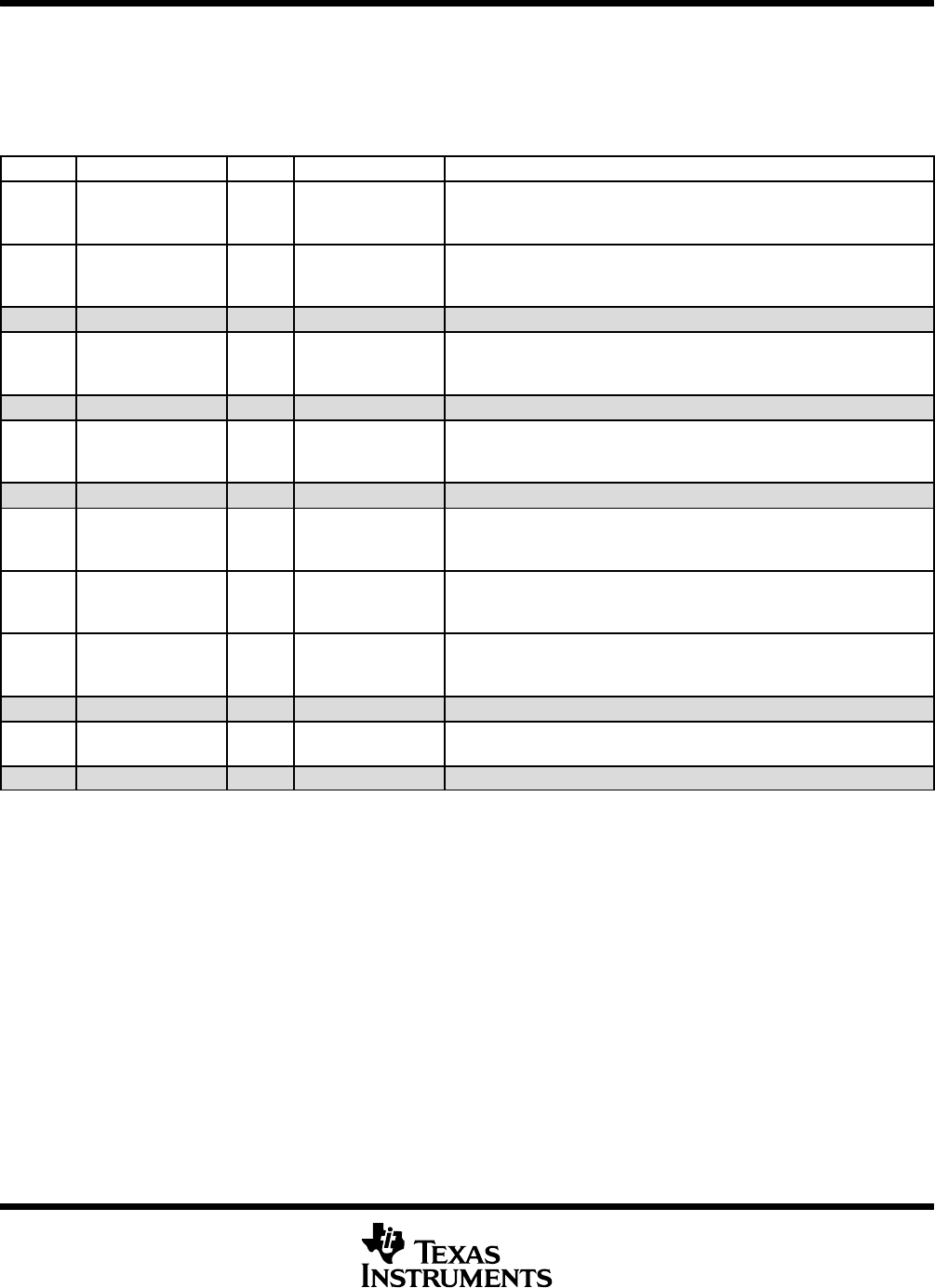

Table 32. PCLKCR Register Bit Definitions

†

BIT(S) NAME TYPE RESET DESCRIPTION

0 EVAENCLK R/W 0 If this bit is set, it enables the high-speed clock (HSPCLK) within the EV-A

peripheral. For low power operation, this bit is set to zero by the user or

by reset.

1 EVBENCLK R/W 0 If this bit is set, it enables the high-speed clock (HSPCLK) within the EV-B

peripheral. For low power operation, this bit is set to zero by the user or

by reset.

2 reserved R=0 0 reserved

3 ADCENCLK R/W 0 If this bit is set, it enables the high-speed clock (HSPCLK) within the ADC

peripheral. For low power operation, this bit is set to zero by the user or

by reset.

7:4 reserved R=0 0:0

8 SPIAENCLK R/W 0 If this bit is set, it enables the low-speed clock (LSPCLK) within the SPI

peripheral. For low power operation, this bit is set to zero by the user or

by reset.

9 reserved R=0 0 reserved

10 SCIAENCLK R/W 0 If this bit is set, it enables the low-speed clock (LSPCLK) within the SCI-A

peripheral. For low power operation, this bit is set to zero by the user or

by reset.

11 SCIBENCLK R/W 0 If this bit is set, it enables the low-speed clock (LSPCLK) within the SCI-B

peripheral. For low power operation, this bit is set to zero by the user or

by reset.

12 MAENCLK R/W 0 If this bit is set, it enables the low-speed clock (LSPCLK) within the

McBSP peripheral. For low power operation, this bit is set to zero by the

user or by reset.

13 reserved R=0 0 reserved

14 HECCAENCLK R/W 0 If this bit is set, it enables the system clock within the CAN peripheral. For

low power operation, this bit is set to zero by the user or by reset.

15 reserved R=0 0 reserved

†

If a peripheral block is not used, then the clock to that peripheral can be turned off to minimize power consumption.

PR

DU

T PREVIEW