TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

45

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

system control (continued)

The PLL, clocking, watchdog and low-power modes, are controlled by the registers listed in Table 31.

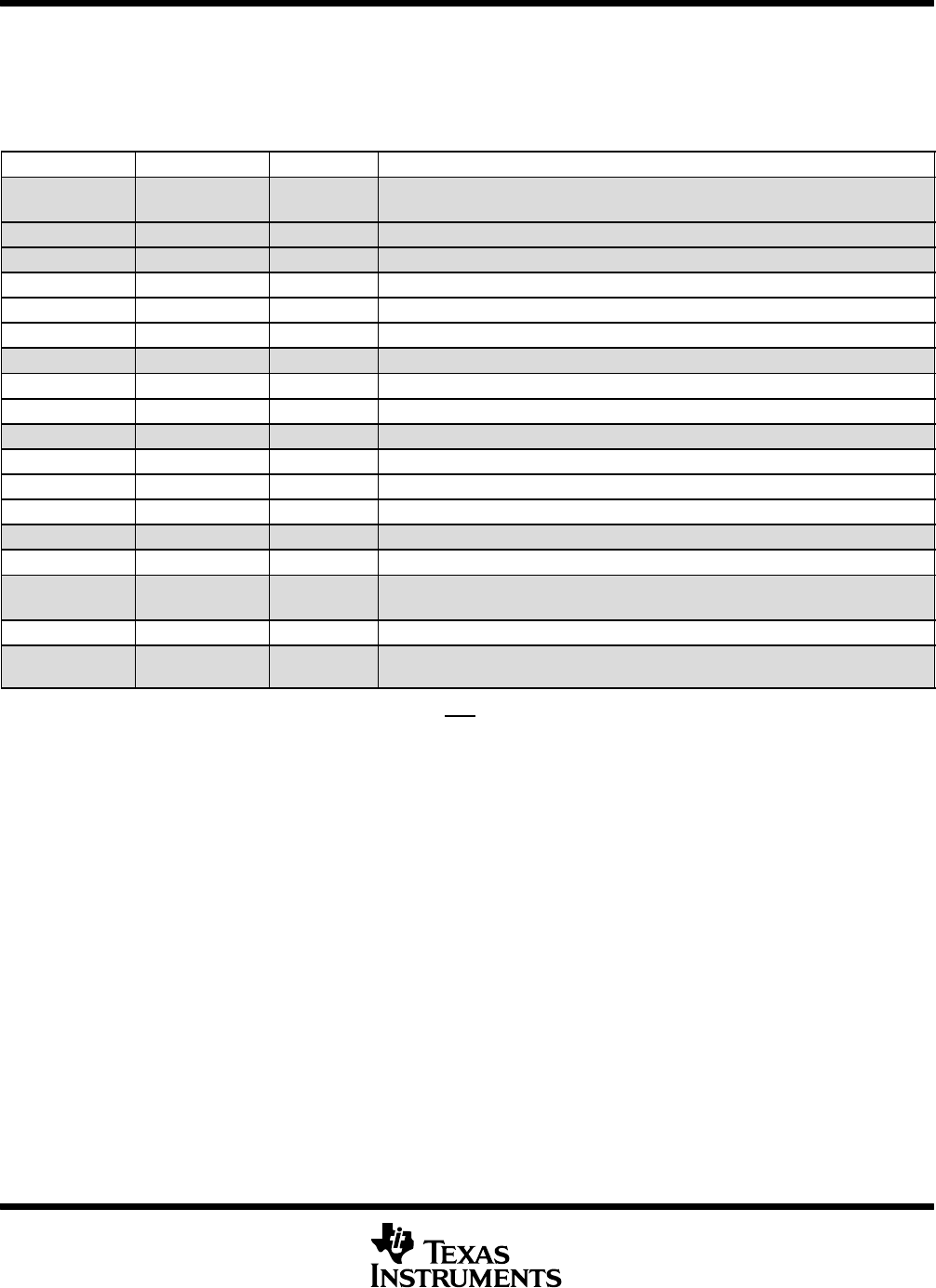

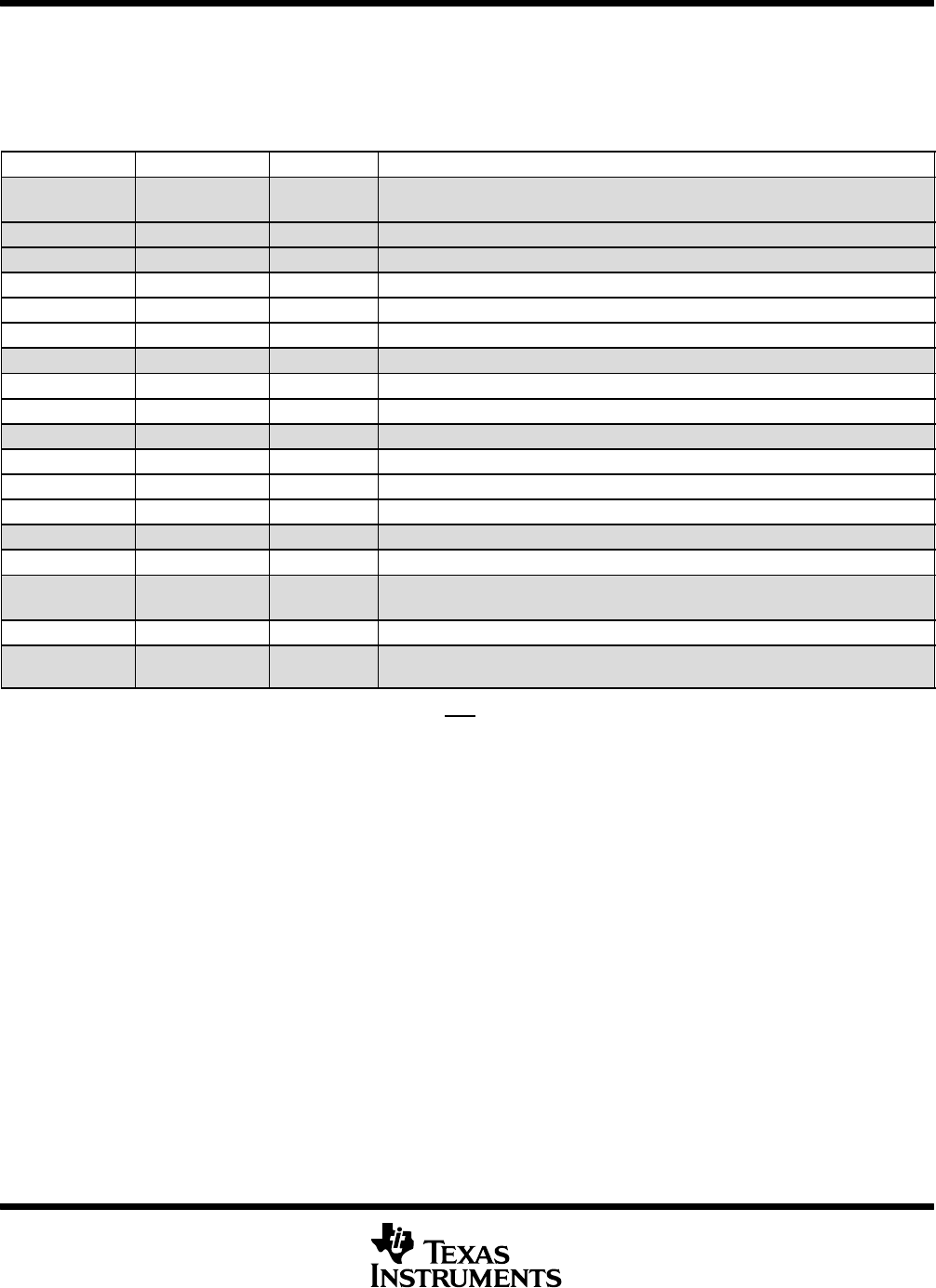

Table 31. PLL, Clocking, Watchdog, and Low-Power Mode Registers

†

NAME ADDRESS SIZE (x16) DESCRIPTION

reserved 0x0000–7010

0x0000–7017

8

reserved 0x0000–7018 1

reserved 0x0000–7019 1

HISPCP 0x0000–701A 1 High-Speed Peripheral Clock Prescaler Register for HSPCLK clock

LOSPCP 0x0000–701B 1 Low-Speed Peripheral Clock Prescaler Register for HSPCLK clock

PCLKCR 0x0000–701C 1 Peripheral Clock Control Register

reserved 0x0000–701D 1

LPMCR0 0x0000–701E 1 Low Power Mode Control Register 0

LPMCR1 0x0000–701F 1 Low Power Mode Control Register 1

reserved 0x0000–7020 1

PLLCR 0x0000–7021 1 PLL Control Register

‡

SCSR 0x0000–7022 1 System Control & Status Register

WDCNTR 0x0000–7023 1 Watchdog Counter Register

reserved 0x0000–7024 1

WDKEY 0x0000–7025 1 Watchdog Reset Key Register

reserved 0x0000–7026

0x0000–7028

3

WDCR 0x0000–7029 1 Watchdog Control Register

reserved 0x0000–702A

0x0000–702F

6

†

All of the above registers can only be accessed, by executing the EALLOW instruction.

‡

The PLL control register (PLLCR) is reset to a known state by the XRS

signal only.

PR

DU

T PREVIEW