TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

40

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

PIE registers (continued)

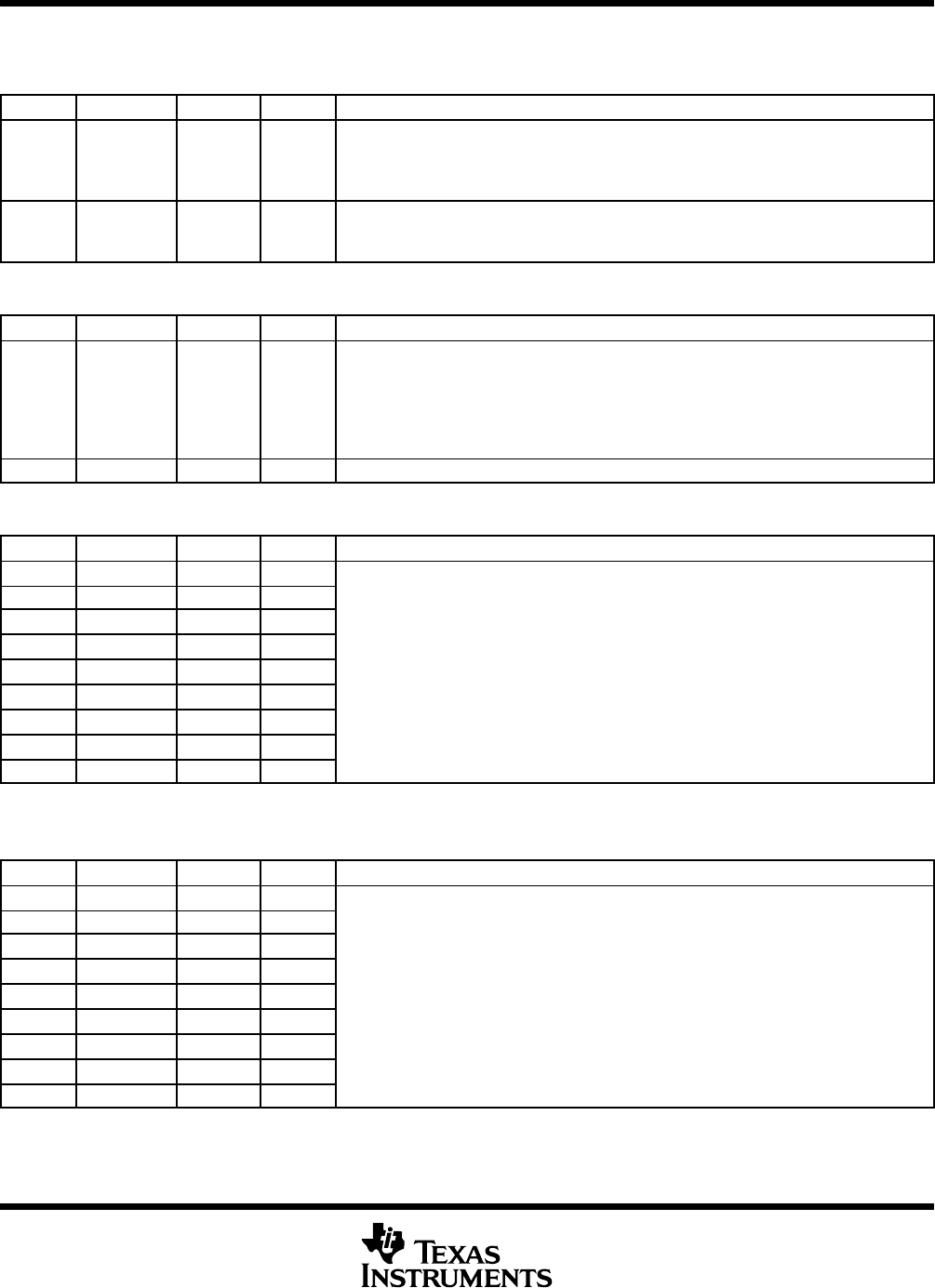

Table 23. PIECTRL Register Bit Definitions

BIT(S) NAME TYPE RESET DESCRIPTION

0 ENPIE R/W 0 Enable vector fetching from PIE block. When this bit is set to 1, all vectors are fetched from

the PIE vector table. If this bit is set to 0, the PIE block is disabled and vectors are fetched

as normal. All PIE block registers (PIEACK, PIEIFR, PIEIER) can be accessed even when

the PIE block is disabled.

15:1 PIEVECT R 0 Vector fetch address. Displays the address of the vector that was fetched. The least

significant bit of the address is ignored and only bits 1 to 15 are shown. The vector address

can be used to determine which interrupt generated the fetch.

Table 24. PIEACK Register Bit Definitions

BIT(S) NAME TYPE RESET DESCRIPTION

11:0 PIEACK R/W=1 0 Writing a 1 to the respective interrupt bit enables the PIE block to drive a pulse into the CPU

interrupts input, if an interrupt is pending on any of the group interrupts. Reading this

register indicates if an interrupt is pending in the respective group. Bit 0 refers to INT1 up

to Bit 11, which refers to INT12.

Note: Writes of 0 are ignored.

15:12 spares R=0 0

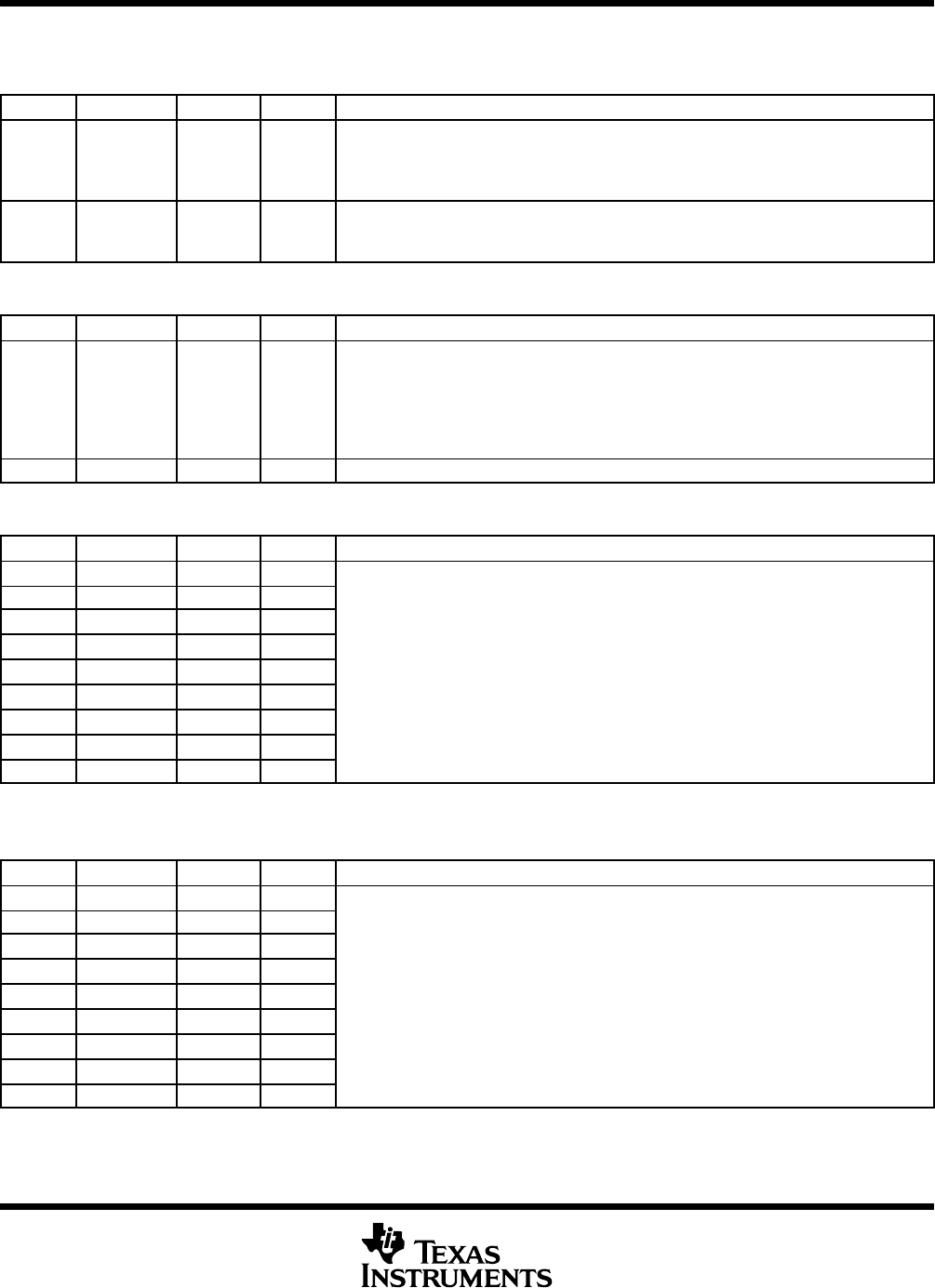

Table 25. PIEIERx Register Bit Definitions

†

BIT(S) NAME TYPE RESET DESCRIPTION

0 INTx.1 R/W 0

1 INTx.2 R/W 0

2 INTx.3 R/W 0

3 INTx.4 R/W 0

These register bits individually enable an interru

p

p

4 INTx.5 R/W 0

ese reg

s

er

s

n

v

ua

y ena

e an

n

errup

w

n a group.

ey

e

ave very muc

like the CPU interrupt enable register. Setting a bit to 1 will enable the servicing of the

5 INTx.6 R/W 0

.

respective interrupt. Setting a bit to 0 will disable the servicing of the bit.

6 INTx.7 R/W 0

7 INTx.8 R/W 0

15:8 spares R=0 0

†

x = 1 to 12. INTx means CPU interrupts INT1 to INT12.

Table 26. PIEIFRx Register Bit Definitions

†

BIT(S) NAME TYPE RESET DESCRIPTION

0 INTx.1 R/W 0

1 INTx.2 R/W 0

2 INTx.3 R/W 0

These register bits indicate if an interrupt is currently active. They behave very much like

th CPU i t t fl i t Wh i t ti ti th ti i t bit i t

3 INTx.4 R/W 0

the CPU interrupt flag register. When an interrupt is active, the respective register bit is set.

The bit is cleared when the interru

p

t is serviced or by writing a 0 to the register bit This

4 INTx.5 R/W 0

w

u

v

y w

.

register can also be read to determine which interrupts are active or pending.

5 INTx.6 R/W 0

ending.

Note: The PIEIFR register bit is cleared during the interrupt vector fetch portion of

6 INTx.7 R/W 0

Note: The PIEIFR register bit is cleared during the interrupt vector fetch portion of

p

p

7 INTx.8 R/W 0

.

15:8 spares R=0 0

†

x = 1 to 12. INTx means CPU interrupts INT1 to INT12.

PR

DU

T PREVIEW