TMS320F2810, TMS320F2812

DIGITAL SIGNAL PROCESSORS

SPRS174B – APRIL 2001 – REVISED SEPTEMBER 2001

38

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

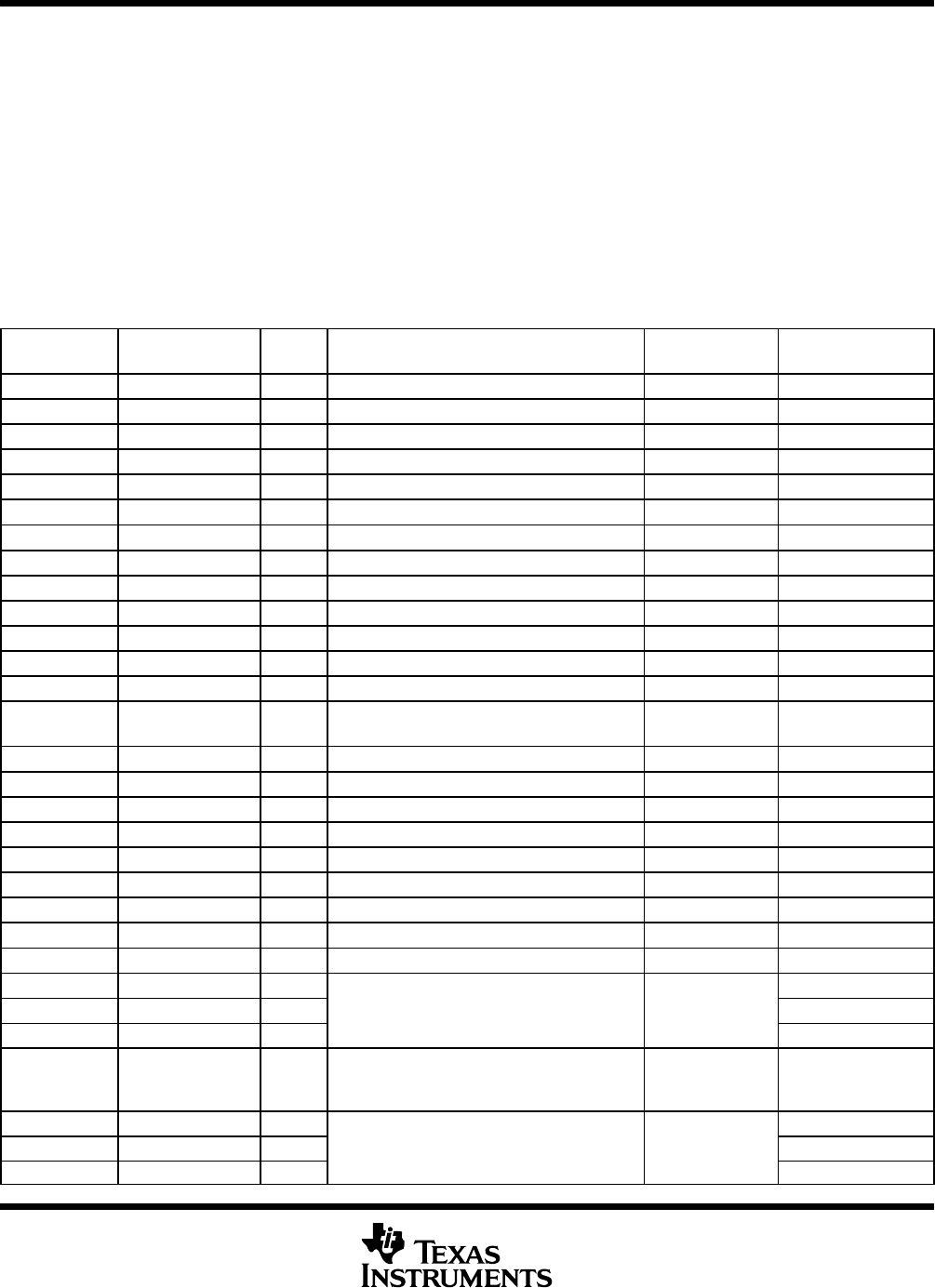

PIE vector map

The PIE Vector Table (Table 21) consists of a 256 x 16 SARAM that can also be used as RAM if the PIE block

is not in use. The PIE vector table contents are undefined on reset. Interrupt priority for INT1 to INT12 is fixed

by the CPU. Priority for each group of 8 interrupts is, controlled by the PIE. For example: if INT1.1 should occur

simultaneously with INT8.1, both interrupts will be presented to the CPU simultaneously by the PIE block, and

the CPU will service INT1.1 first. If INT1.1 should occur simultaneously with INT1.8, then INT1.1 will be sent

to the CPU first and then INT1.8 will follow. Interrupt prioritization is performed during the vector fetch portion

of the interrupt processing. A “TRAP 1” to “TRAP 12” instruction or an “INTR INT1” to “INTR INT12” instruction

will always fetch the vector from the first location of each group (“INTR1.1” to “INT12.1”). Hence, it is

recommended that these instructions not be used when PIE is enabled. The “TRAP 0” operation will fetch the

vector from location 0x0000 0D00. The vector table is EALLOW protected.

Table 21. PIE Vector Table

NAME ADDRESS

SIZE

(x16)

DESCRIPTION CORE PRIORITY

PIE GROUP

PRIORITY

not used 0x0000 0D00 2 RESET never fetched here 1 (highest) –

not used 0x0000 0D02 2 INT1 remapped to INT1.1–INT1.8 below – –

not used 0x0000 0D04 2 INT2 remapped to INT2.1–INT2.8 below – –

not used 0x0000 0D06 2 INT3 remapped below – –

not used 0x0000 0D08 2 INT4 remapped below – –

not used 0x0000 0D0A 2 INT5 remapped below – –

not used 0x0000 0D0C 2 INT6 remapped below – –

not used 0x0000 0D0E 2 INT7 remapped below – –

not used 0x0000 0D10 2 INT8 remapped below – –

not used 0x0000 0D12 2 INT9 remapped below – –

not used 0x0000 0D14 2 INT10 remapped below – –

not used 0x0000 0D16 2 INT11 remapped below – –

not used 0x0000 0D18 2 INT12 remapped below – –

INT13 0x0000 0D1A 2 External Interrupt 13 (XINT13) or

CPU-Timer 1 (for RTOS use)

17 –

INT14 0x0000 0D1C 2 CPU-Timer 2 (for RTOS use) 18 –

DATALOG 0x0000 0D1E 2 CPU Data Logging Interrupt 19 (lowest) –

RTOSINT 0x0000 0D20 2 CPU Real-Time OS Interrupt 4 –

EMUINT 0x0000 0D22 2 CPU Emulation Interrupt 2 –

NMI 0x0000 0D24 2 External Non-Maskable Interrupt 3 –

ILLEGAL 0x0000 0D26 2 Illegal Operation – –

USER0 0x0000 0D28 2 User Defined Trap – –

. . . . . .

USER11 0x0000 0D3E 2 User Defined Trap – –

INT1.1 0x0000 0D40 2 1 (highest)

. . .

Group 1 Interrupt Vectors 5

.

INT1.8 0x0000 0D4E 2

8 (lowest)

.

.

.

.

.

.

.

.

.

Group 2 Interrupt Vectors

to

Group 11 Interrupt Vectors

6

to

15

INT12.1 0x0000 0DF0 2 1 (highest)

. . .

Group 12 Interrupt Vectors 16

.

INT12.8 0x0000 0DFE 2

8 (lowest)

PR

DU

T PREVIEW