SLCS115D − DECEMBER 1986 − REVISED JULY 2003

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

POST OFFICE BOX 1443

• HOUSTON, TEXAS 77251−1443

PARAMETER MEASUREMENT INFORMATION

A close approximation of the input offset voltage can be obtained by using a binary search method to vary the

differential input voltage while monitoring the output state. When the applied input voltage differential is equal,

but opposite in polarity, to the input offset voltage, the output changes states.

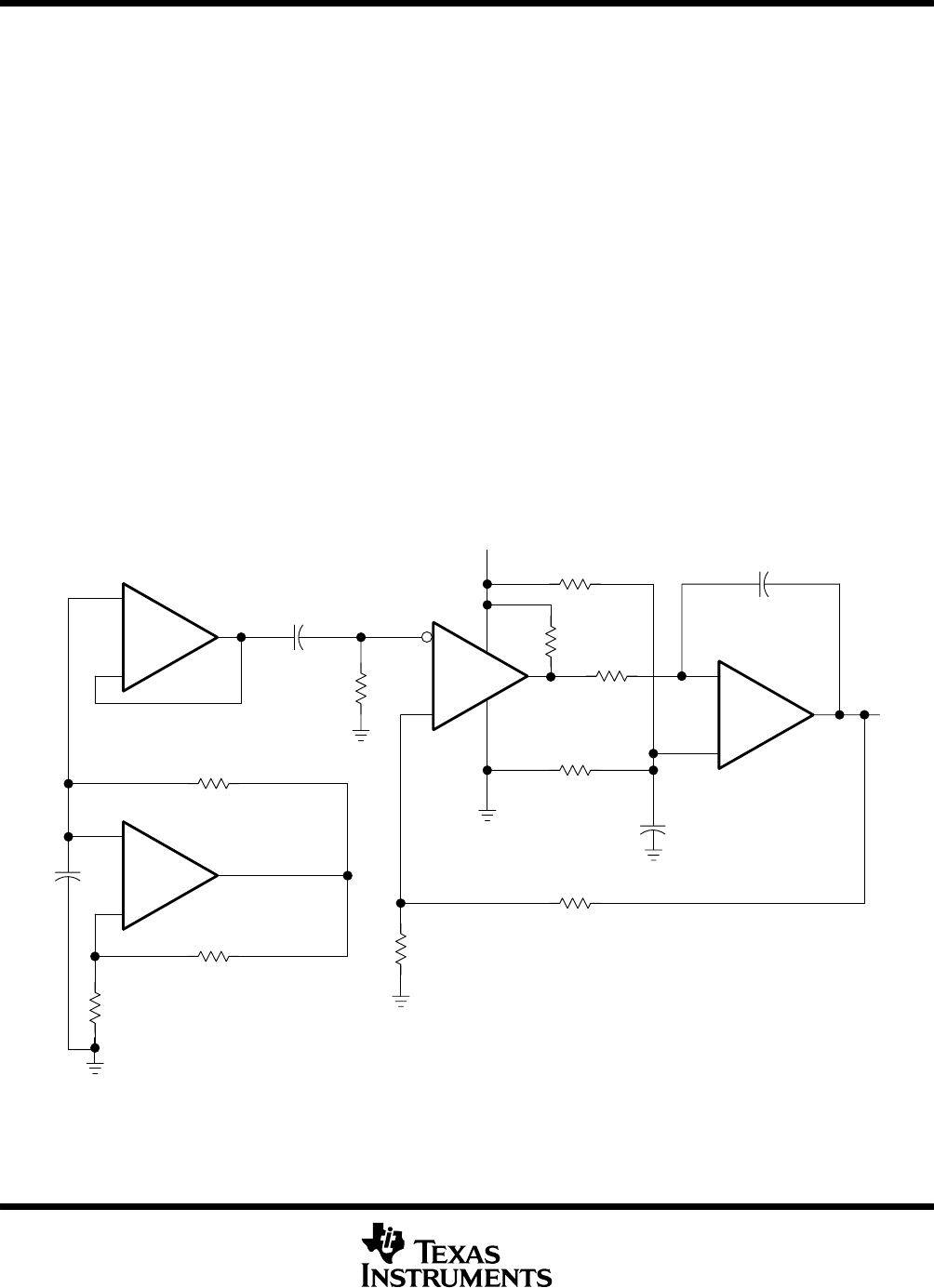

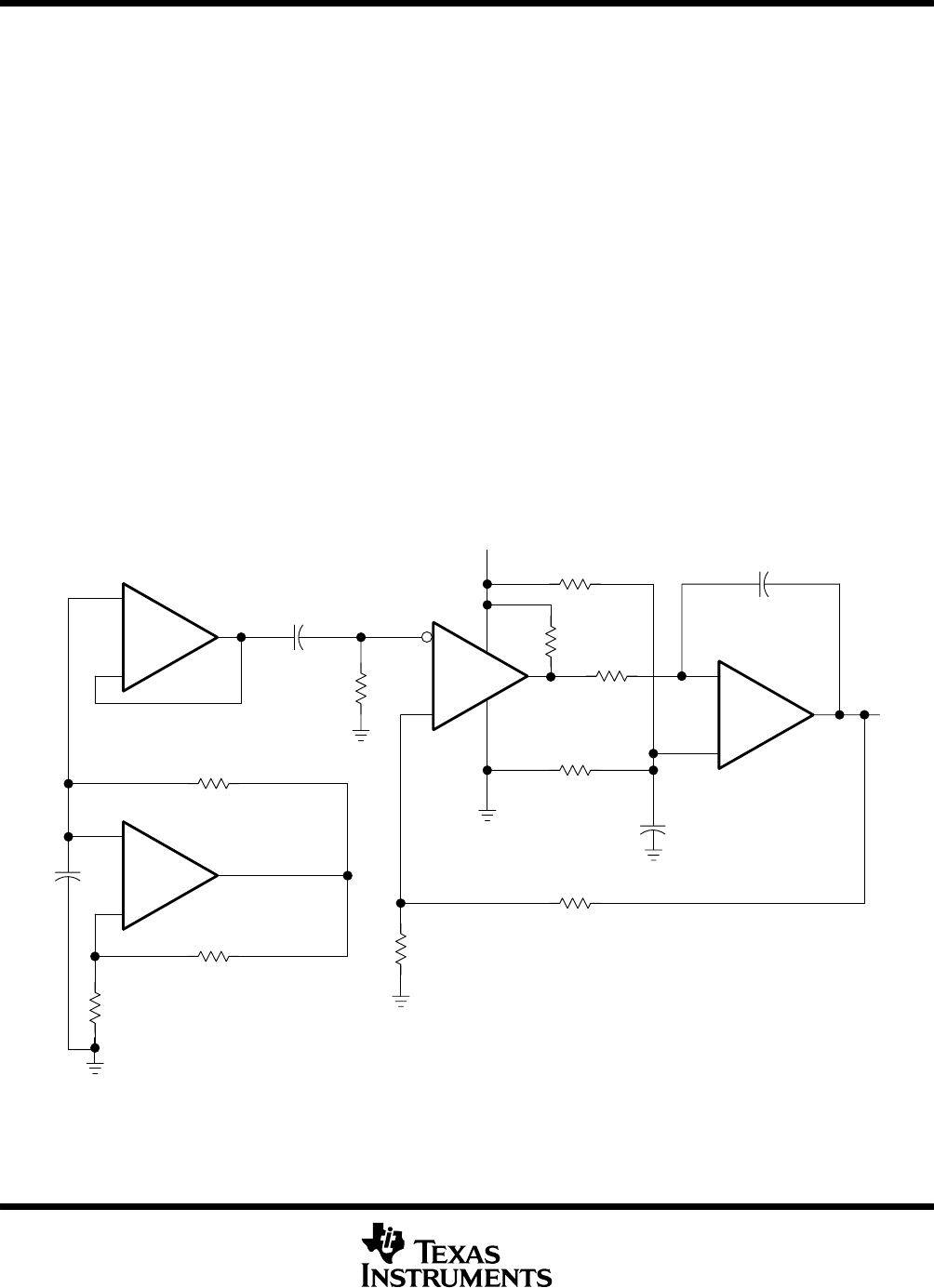

Figure 2 illustrates a practical circuit for direct dc measurement of input offset voltage that does not bias the

comparator in the linear region. The circuit consists of a switching-mode servo loop in which U1A generates

a triangular waveform of approximately 20-mV amplitude. U1B acts as a buffer, with C2 and R4 removing any

residual dc offset. The signal is then applied to the inverting input of the comparator under test, while the

noninverting input is driven by the output of the integrator formed by U1C through the voltage divider formed

by R9 and R10. The loop reaches a stable operating point when the output of the comparator under test has

a duty cycle of exactly 50%, which can only occur when the incoming triangle wave is sliced symmetrically or

when the voltage at the noninverting input exactly equals the input offset voltage.

The voltage divider formed by R9 and R10 provides an increase in input offset voltage by a factor of 100 to

make measurement easier. The values of R5, R8, R9, and R10 can significantly influence the accuracy of the

reading; therefore, it is suggested that their tolerance level be 1% or lower.

Measuring the extremely low values of input current requires isolation from all other sources of leakage current

and compensation for the leakage of the test socket and board. With a good picoammeter, the socket and board

leakage can be measured with no device in the socket. Subsequently, this open-socket leakage value can be

subtracted from the measurement obtained with a device in the socket to obtain the actual input current of the

device.

−

+

DUT

V

DD

+

−

−

+

−

+

C2

1 µF

R4

47 kΩ

R5

1.8 kΩ, 1%

C3

0.68 µF

U1C

1/4 TLC274CN

U1B

1/4 TLC274CN

U1A

1/4 TLC274CN

R7

1 MΩ

R8

1.8 kΩ, 1%

R9

10 kΩ, 1%

R1

240 kΩ

R2

10 kΩ

C1

0.1 µF

R3

100 kΩ

C4

0.1 µF

Integrator

R10

100 Ω, 1%

Buffer

Triangle

Generator

V

IO

(X100)

R6

5.1 kΩ

Figure 2. Circuit for Input Offset Voltage Measurement