TIBPAL16R4-25C, TIBPAL16R6-25C, TIBPAL16R8-25C

TIBPAL16R4-30M, TIBPAL16R6-30M, TIBPAL16R8-30M

LOW-POWER HIGH-PERFORMANCE IMPACT™ PAL

®

CIRCUITS

SRPS059A FEBRUARY 1984 − REVISED DECEMBER 2010

13

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

programming information

Texas Instruments programmable logic devices can be programmed using widely available software and

inexpensive device programmers.

Complete programming specifications, algorithms, and the latest information on hardware, software, and

firmware are available upon request. Information on programmers capable of programming Texas Instruments

programmable logic also is available, upon request, from the nearest TI field sales office or local authorized TI

distributor, by calling Texas Instruments at +1 (972) 644−5580, or by visiting the TI Semiconductor Home Page

at www.ti.com/sc.

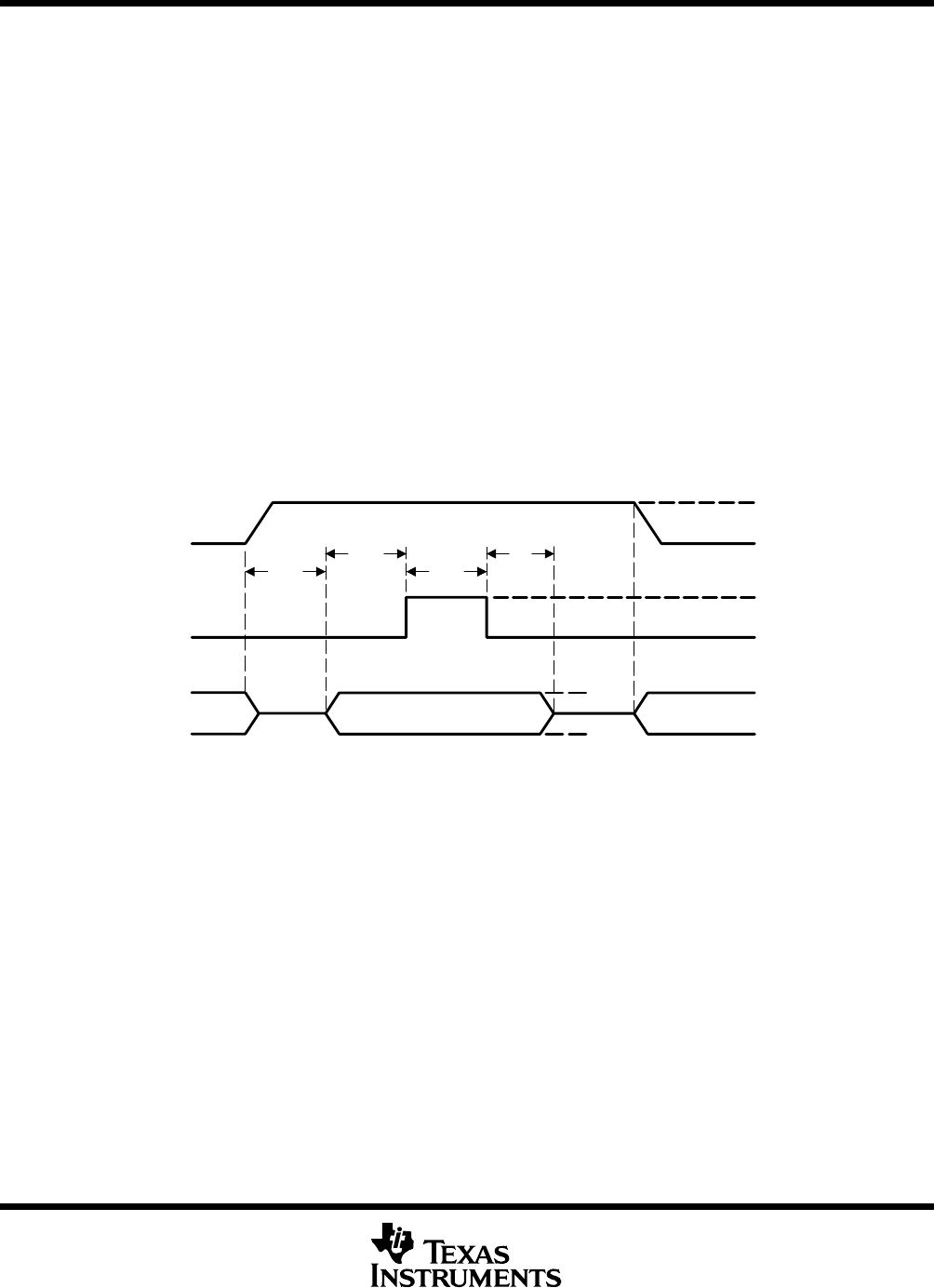

preload procedure for registered outputs (see Figure 1 and Note 3)

The output registers can be preloaded to any desired state during device testing. This permits any state to be

tested without having to step through the entire state-machine sequence. Each register is preloaded individually

by following the steps given below.

Step 1. With V

CC

at 5 V and Pin 1 at V

IL

, raise Pin 11 to V

IHH

.

Step 2. Apply either V

IL

or V

IH

to the output corresponding to the register to be preloaded.

Step 3. Pulse Pin 1, clocking in preload data.

Step 4. Remove output voltage, then lower Pin 11 to V

IL

. Preload can be verified by observing the

voltage level at the output pin.

t

d

t

su

t

w

t

d

V

IHH

V

IL

V

IL

V

OL

V

OH

V

IH

Pin 11

Pin 1

Registered I/O

Input Output

V

IH

V

IL

NOTE 3: t

d

= t

su

= t

h

= 100 ns to 1000 ns V

IHH

= 10.25 V to 10.75 V

Figure 1. Preload Waveforms