Intel

£

Advanced+ Boot Block Flash Memory (C3)

Datasheet 25

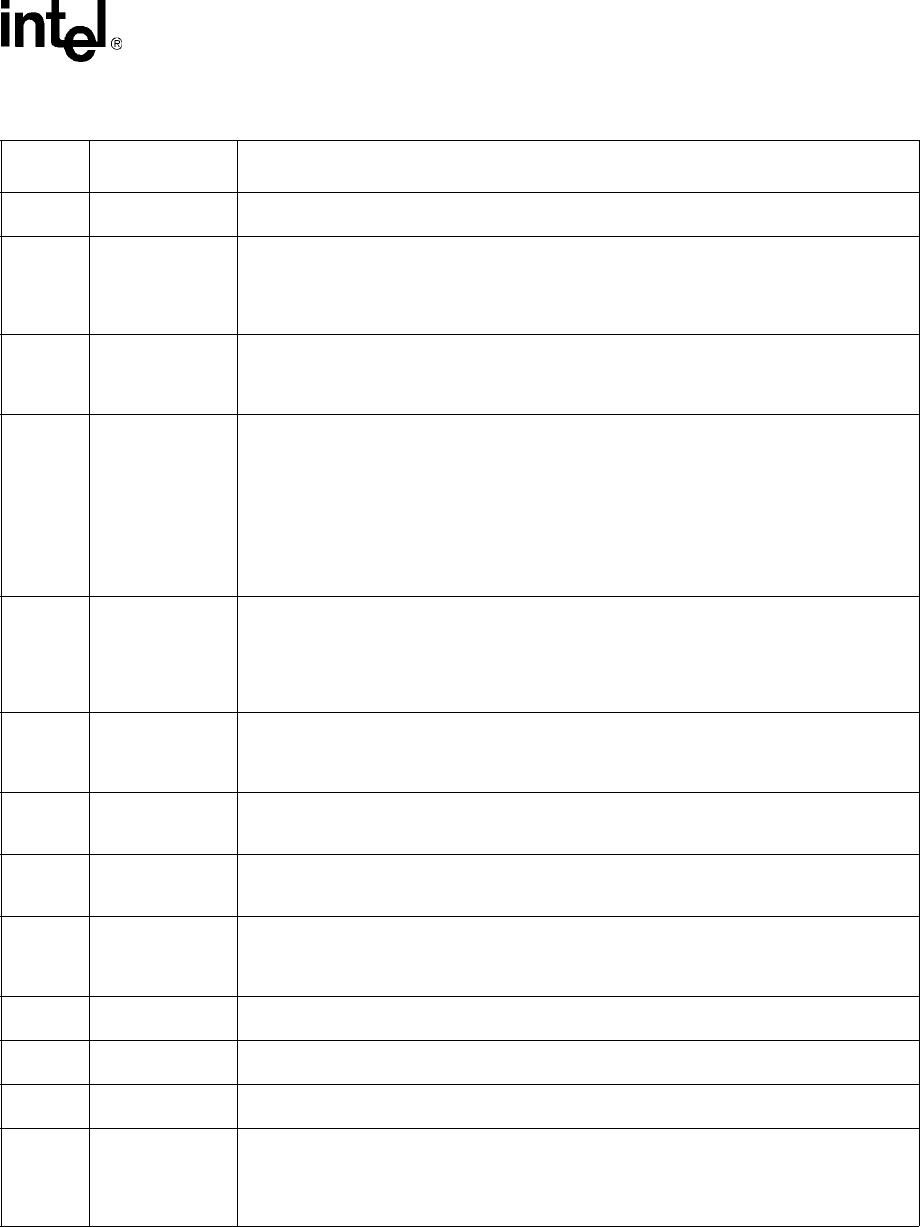

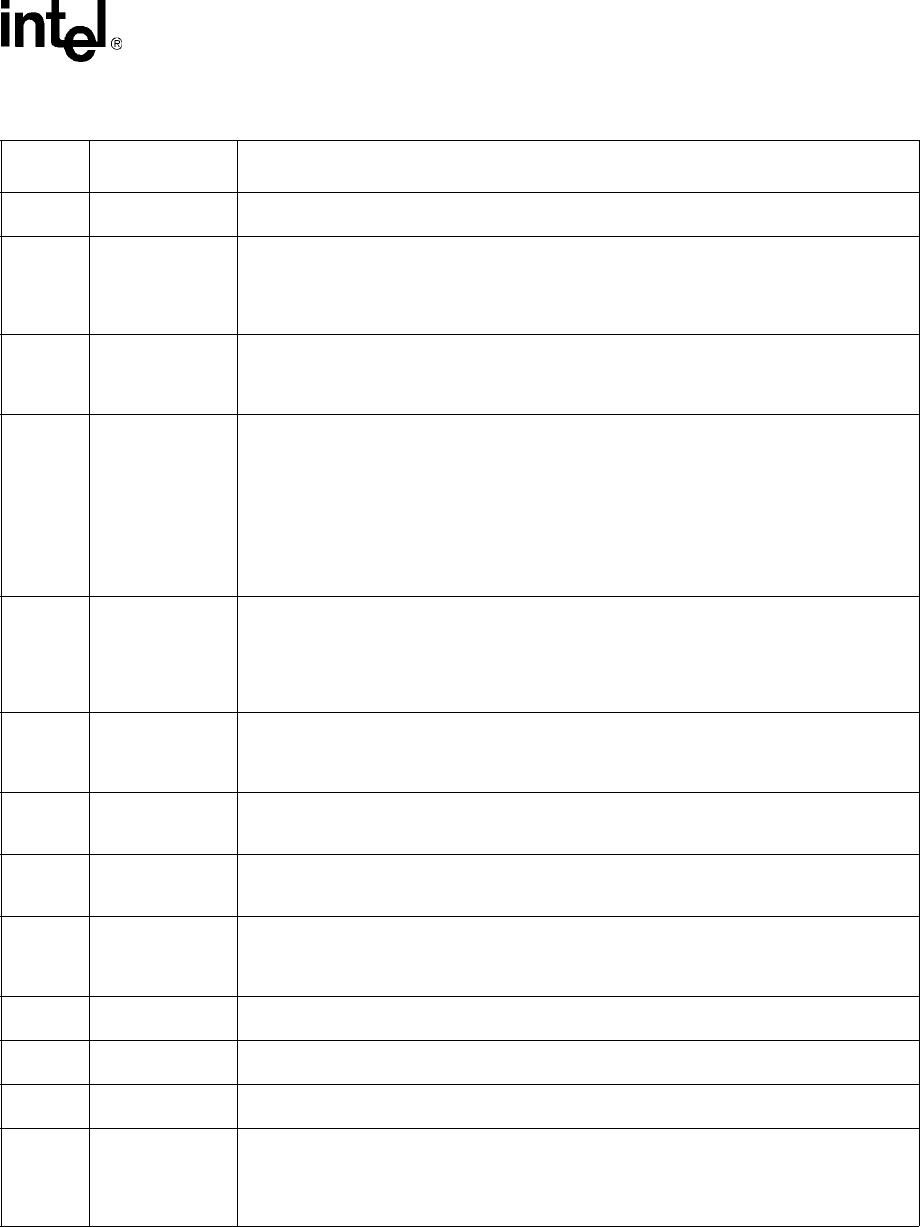

Table 8. Command Codes and Descriptions

Code

(HEX)

Device Mode Command Description

FF Read Array

This command places the device in read-array mode, which outputs array data on the data

pins.

40 Program Set-Up

This is a two

-cycle command. The first cycle prepares the CUI for a program operation. The

second cycle latches addresses and data information and initiates the WSM to execute the

Program algorithm. The flash outputs status-register data when CE# or OE# is toggled. A Read

Array command is required after programming to read array data. See Section 4.2, “Program

Mode” on page 21.

20 Erase Set-Up

This is a two

-cycle command. Prepares the CUI for the Erase Confirm command. If the next

command is not an Erase Confirm command, then the CUI will (a) set both SR.4 and SR.5 of

the status register to a “1,” (b) place the device into the read-status-register mode, and (c) wait

for another command. See Section 4.3, “Erase Mode” on page 22.

D0

Erase Confirm

Program/Erase

Resume

Unlock Block

If the previous command was an Erase Set-Up command, then the CUI will close the address

and data latches and begin erasing the block indicated on the address pins. During program/

erase, the device will respond only to the Read Status Register, Program Suspend and Erase

Suspend commands, and will output status-register data when CE# or OE# is toggled.

If a Program or Erase operation was previously suspended, this command will resume that

operation.

If the previous command was Block Unlock Set-Up, the CUI will latch the address and unlock

the block indicated on the address pins. If the block had been previously set to Lock-Down, this

operation will have no effect. (See Section 5.1)

B0

Program Suspend

Erase Suspend

Issuing this command will begin to suspend the currently executing Program/Erase operation.

The status register will indicate when the operation has been successfully suspended by

setting either the program-suspend SR[2] or erase-suspend SR[6] and the WSM status bit

SR[7] to a “1” (ready). The WSM will continue to idle in the SUSPEND state, regardless of the

state of all input-control pins except RP#, which will immediately shut down the WSM and the

remainderofthechipifRP#isdriventoV

IL

. See Sections 3.2.5.1 and 3.2.6.1.

70

Read Status

Register

This command places the device into read-status-register mode. Reading the device will

output the contents of the status register, regardless of the address presented to the device.

The device automatically enters this mode after a Program or Erase operation has been

initiated. See Section 4.1.4, “Read Status Register” on page 20.

50

Clear Status

Register

The WSM can set the block-lock status SR[1], V

PP

Status SR[3], program status SR[4], and

erase-status SR[5] bits in the status register to “1,” but it cannot clear them to “0.” Issuing this

command clears those bits to “0.”

90

Read

Identifier

Puts the device into the read-identifier mode so that reading the device will output the

manufacturer/device codes or block-lock status. See Section 4.1.2, “Read Identifier” on

page 19.

60

Block Lock, Block

Unlock, Block

Lock-Down Set-

Up

Prepares the CUI for block-locking changes. If the next command is not Block Unlock, Block

Lock, or Block Lock-Down, then the CUI will set both the program and erase-status-register

bits to indicate a command-sequence error. See Section 5.0, “Security Modes” on page 27.

01 Lock-Block

If the previous command was Lock Set-Up, the CUI will latch the address and lock the block

indicated on the address pins. (See Section 5.1)

2F Lock-Down

If the previous command was a Lock-Down Set-Up command, the CUI will latch the address

and lock-down the block indicated on the address pins. (See Section 5.1)

98

CFI

Query

Puts the device into the CFI-Query mode so that reading the device will output Common Flash

Interface information. See Section 4.1.3 and Appendix C, “Common Flash Interface”.

C0

Protection

Program

Set-Up

This is a two-cycle command. The first cycle prepares the CUI for a program operation to the

protection register. The second cycle latches addresses and data information and initiates the

WSM to execute the Protection Program algorithm to the protection register. The flash outputs

status-register data when CE# or OE# is toggled. A Read Array command is required after

programming to read array data. See Section 5.5.