Intel

£

Advanced+ Boot Block Flash Memory (C3)

62 Datasheet

C.6 Intel-Specific Extended Query Table

Certain flash features and commands are optional. The Intel-Specific Extended Query table

specifies this and other similar types of information.

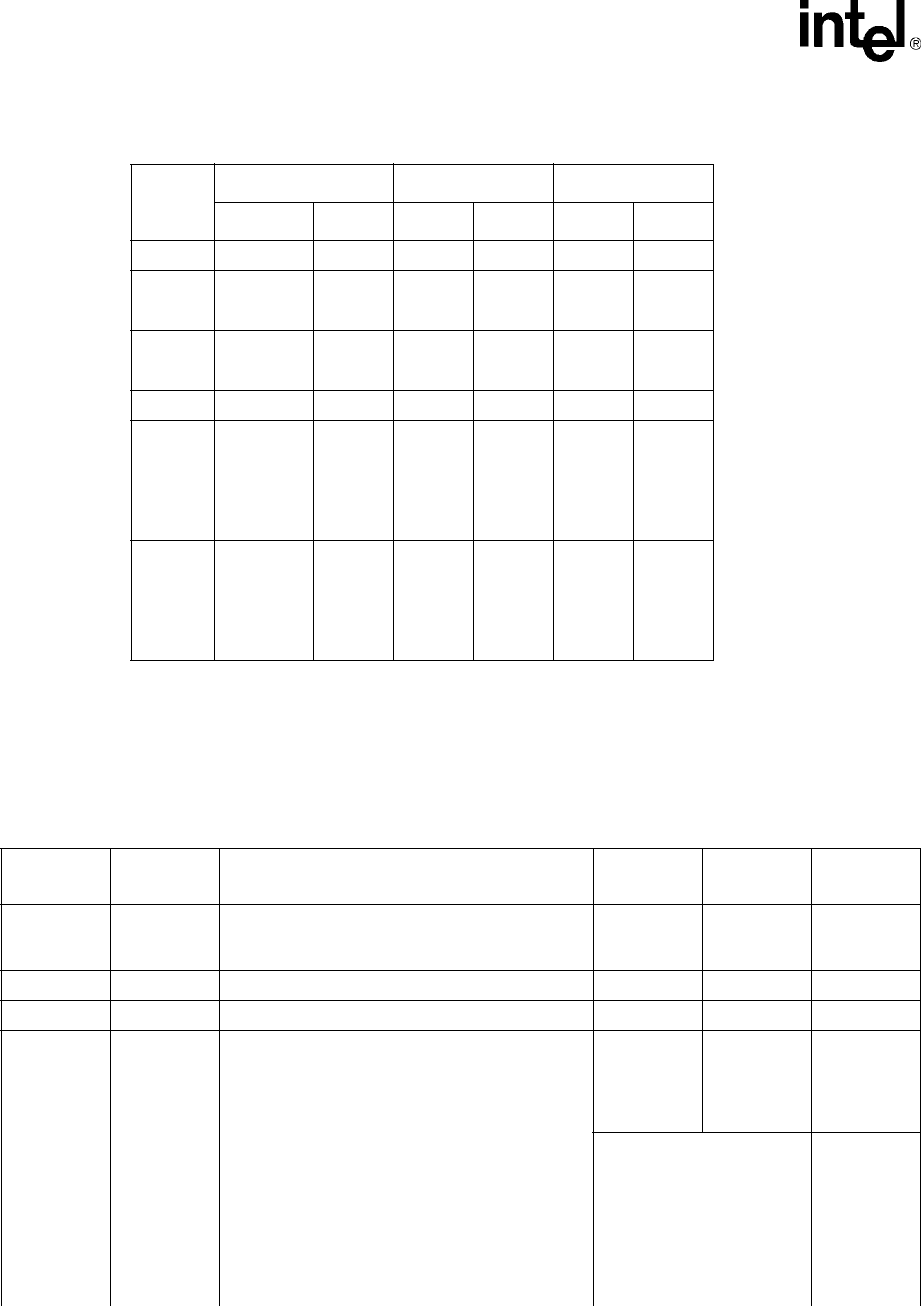

Table 31. Device Geometry Details

Address

16 Mbit 32 Mbit 64 Mbit

-B -T -B -T -B -T

0x27 --15 -15 --16 -16 --17 --17

0x28 --01 --01 --01 --01 --01 --01

0x29 --00 --00 --00 -00 -00 -00

0x2A --00 --00 --00 -00 -00 -00

0x2B --00 --00 --00 -00 -00 -00

0x2C --02 --02 --02 --02 --02 --02

0x2D --07 --1E --07 --3E --07 --7E

0x2E --00 --00 --00 -00 -00 -00

0x2F --20 --00 --20 -00 --20 --00

0x30 --00 --01 --00 --01 --00 --01

0x31 --1E --07 --3E --07 --7E --07

0x32 --00 --00 --00 -00 -00 -00

0x33 --00 --20 --00 --20 --00 --20

0x34 --01 --00 --01 --00 --01 --00

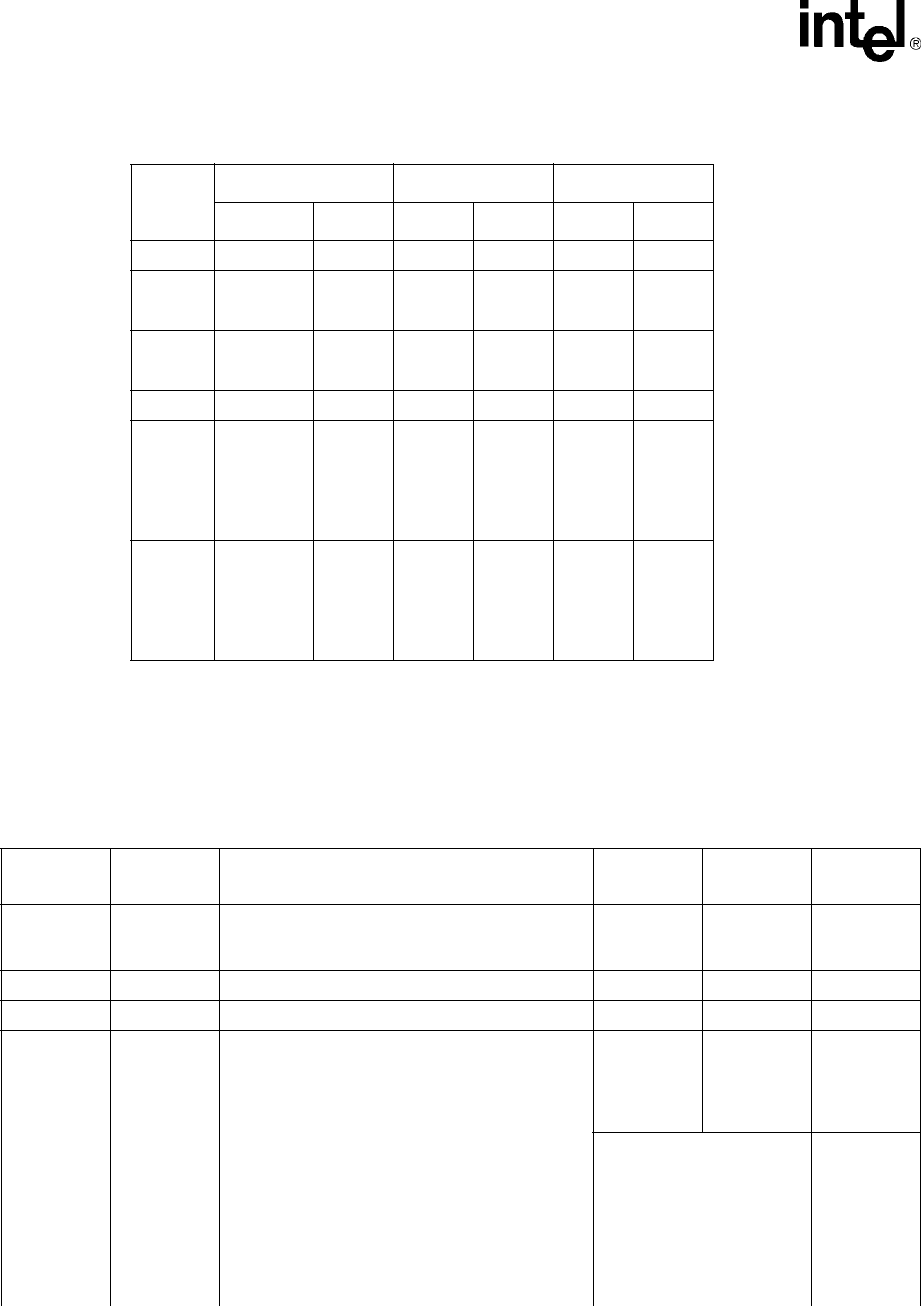

Table 32. Primary-Vendor Specific Extended Query (Sheet 1 of 2)

Offset

1

P = 0x15

Length

Description

(Optional Flash Features and Commands)

Address Hex Code Value

0x(P+0)

0x(P+1)

0x(P+2)

3

Primary extended query table

Unique ASCII string “PRI”

35:

36:

37:

--50

--52

--49

“P”

“R”

“I”

0x(P+3) 1 Major version number, ASCII 38: --31 “1”

0x(P+4) 1 Minor version number, ASCII 39: --30 “0”

0x(P+5)

0x(P+6)

0x(P+7)

0x(P+8)

4

Optional feature and command support (1=yes,

0=no)

bits 9–31 are reserved; undefined bits are “0.” If bit

31 is “1” then another 31 bit field of optional

features follows at the end of the bit-30 field.

3A:

3B:

3C:

3D:

--66

--00

--00

--00

bit 0 Chip erase supported

bit 1 Suspend erase supported

bit 2 Suspend program supported

bit 3 Legacy lock/unlock supported

bit 4 Queued erase supported

bit 5 Instant individual block locking supported

bit 6 Protection bits supported

bit 7 Page mode read supported

bit 8 Synchronous read supported

bit 0 = 0

bit 1 = 1

bit 2 = 1

bit 3 = 0

bit 4 = 0

bit 5 = 1

bit 6 = 1

bit 7 = 0

bit 8 = 0

No

Yes

Yes

No

No

Yes

Yes

No

No