Intel

£

Advanced+ Boot Block Flash Memory (C3)

Datasheet 57

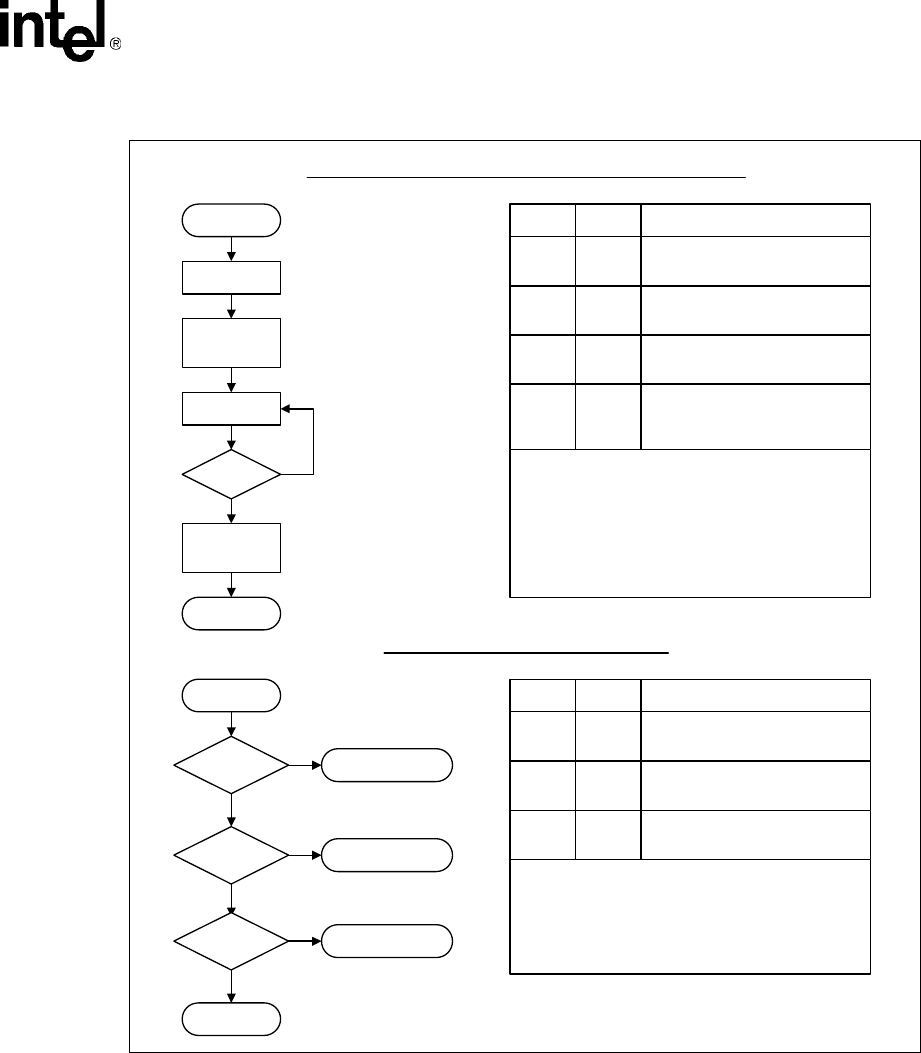

Figure 18. Protection Register Programming Flowchart

FULL STATUS CHECK PROCEDURE

Program Pr otecti on Register operation addresses m ust be

wi thin the Protection Register address space. Addresses

outside this space will return an error.

Repeat for subsequent pr ogramm i ng operations.

Full Status Register check can be done after each pr ogram, or

after a sequence of program operations.

Write 0xFF after the last operation to set Read Ar ray state.

SR[3] must be cleared befor e the Write State Machine wi ll

allow further program attempts.

Only the Clear Staus Register comm and clears SR[1, 3, 4].

If an er ror is detected, clear the Status register before

attempting a program retry or other error recover y.

1

0

1

1

PROTECTION REGISTER PROGRAMMING PROCEDURE

Start

Wri te 0xC0,

PR Address

Wri te PR

Address & Data

Read Status

Register

SR[7] =

Full Status

Check

(i f desired)

Program

Complete

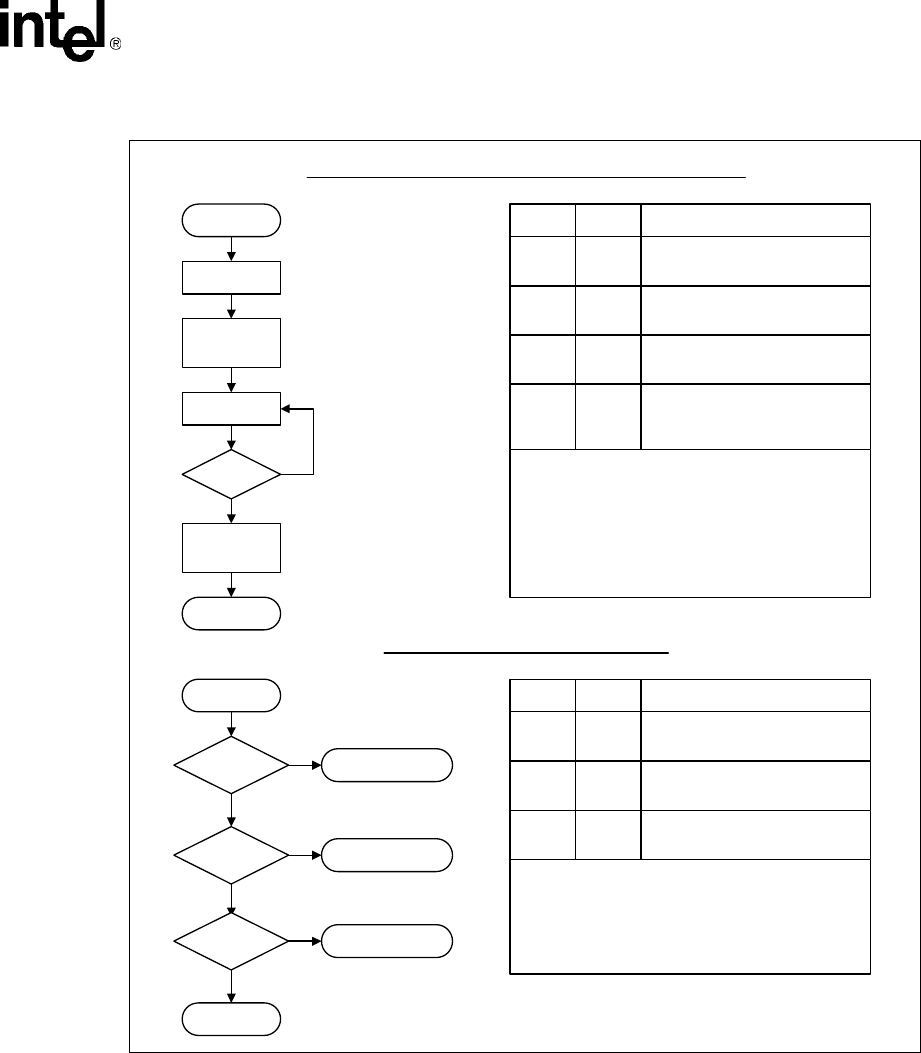

Read Status

Register Data

Program

Successful

SR[3], SR[4] = V

PP

Range Error

Program Er ror

Register Locked;

Program Aborted

Idle

Idle

Bus

Operation

None

None

Command

Check SR[1], SR[3], SR[4]:

0,1,1 = V

PP

Range Er r or

Check SR[1], SR[3], SR[4]:

0,0,1 = Programm ing Err or

Comments

Wr i te

Wr i te

Idle

Program

PR Setup

Protection

Program

None

Data = 0xC0

Addr = Fir st Locati on to Pr ogr am

Data = Data to Pr ogram

Addr = Location to Pr ogram

Check SR[7]:

1 = WSM Ready

0=WSMBusy

Bus

Operation

Command Comments

Read None

Status Register Data. Toggle CE# or

OE# to Update Status Register Data

Idle None

Check SR[1], SR[3], SR[4]:

1,0,1 = Block locked; operati on aborted

(Program Setup)

(Confirm Data)

0

0

SR[3], SR[4] =

0

SR[3], SR[4] =

1