Intel

£

Advanced+ Boot Block Flash Memory (C3)

44 Datasheet

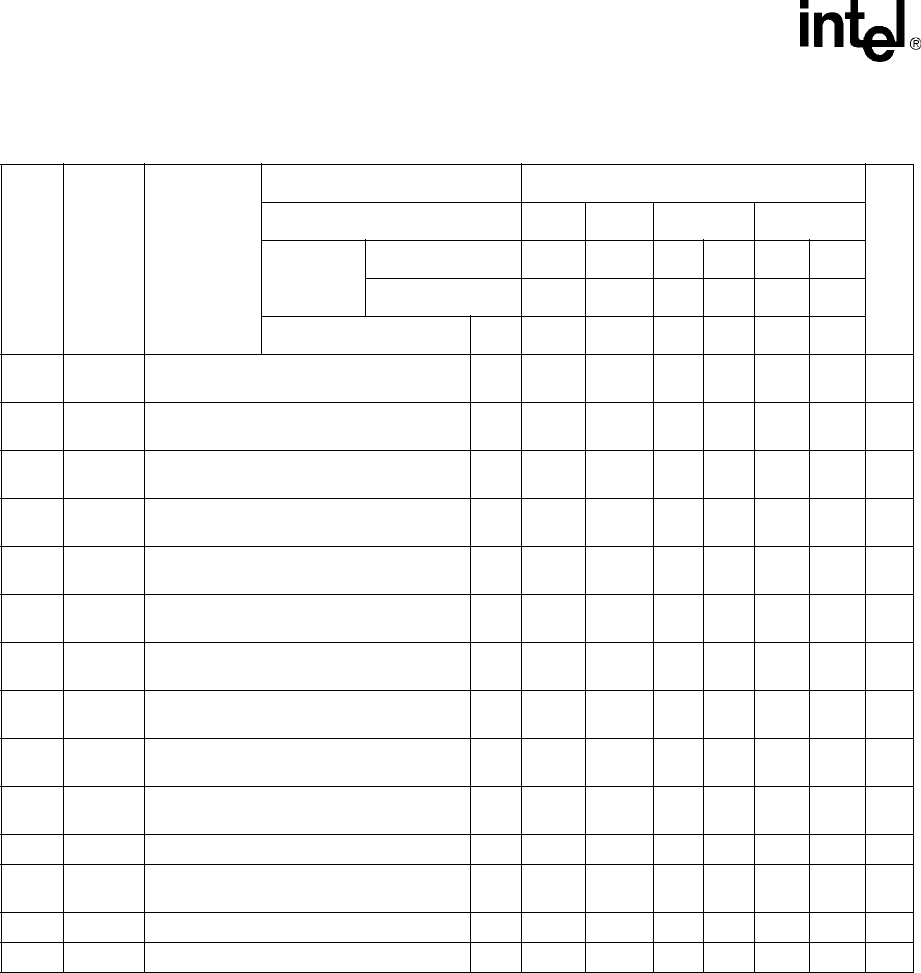

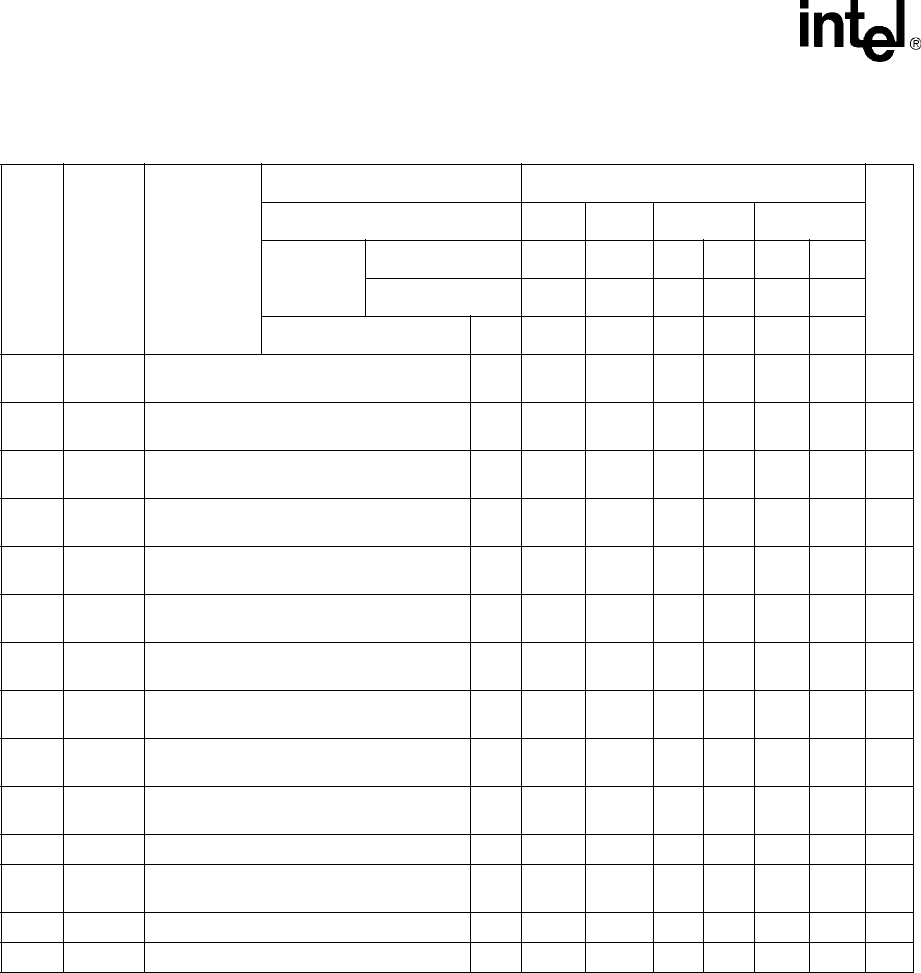

Table 18. Write Operations—16 Mbit Density

#SymParameter

Density 16 Mbit

Unit

Product 70ns 80ns 90ns 110ns

V

CC

3.0 V – 3.6 V 80 100

2.7V–3.6V 70 80 90 110

Note Min Min Min Min Min Min

W1

t

PHWL

/

t

PHEL

RP# High Recovery to WE# (CE#) Going

Low

4,5 150 150 150 150 150 150 ns

W2

t

ELWL

/

t

WLEL

CE# (WE#) Setup to WE# (CE#) Going Low 4,5 0 0 0 0 0 0 ns

W3

t

WLWH

/

t

ELEH

WE#(CE#)PulseWidth 1,4,5 45 50 50 60 70 70 ns

W4

t

DVWH

/

t

DVEH

Data Setup to WE# (CE#) Going High 2,4,5 40 40 50 50 60 60 ns

W5

t

AVWH

/

t

AVEH

Address Setup to WE# (CE#) Going High 2,4,5 50 50 50 60 70 70 ns

W6

t

WHEH

/

t

EHWH

CE# (WE#) Hold Time from WE# (CE#)

High

4,5 0 0 0 0 0 0 ns

W7

t

WHDX

/

t

EHDX

Data Hold Time from WE# (CE#) High 2,4,5 0 0 0 0 0 0 ns

W8

t

WHAX

/

t

EHAX

Address Hold Time from WE# (CE#) High 2,4,5 0 0 0 0 0 0 ns

W9

t

WHWL /

t

EHEL

WE# (CE#) Pulse Width High 1,4,5 25 30 30 30 30 30 ns

W10

t

VPWH

/

t

VPEH

V

PP

Setup to WE# (CE#) Going High 3,4,5 200 200 200 200 200 200 ns

W11 t

QVVL

V

PP

Hold from Valid SRD 3,4 0 0 0 0 0 0 ns

W12

t

BHWH

/

t

BHEH

WP# Setup to WE# (CE#) Going High 3,4 0 0 0 0 0 0 ns

W13 t

QVBL

WP# Hold from Valid SRD 3,4 0 0 0 0 0 0 ns

W14 t

WHGL

WE#HightoOE#GoingLow 3,4 30 30 30 30 30 30 ns

NOTES:

1. Write pulse width (t

WP

) is defined from CE# or WE# going low (whichever goes low last) to CE# or WE# going high

(whichever goes high first). Hence, t

WP

=t

WLWH

=t

ELEH

=t

WLEH

=t

ELWH

. Similarly, write pulse width high (t

WPH

) is defined

from CE# or WE# going high (whichever goes high first) to CE# or WE# going low (whichever goes low last). Hence,

t

WPH

=t

WHWL

=t

EHEL

=t

WHEL

=t

EHWL

.

2. Refer to Table 7, “Command Bus Operations” on page 24 for valid A

IN

or D

IN

.

3. Sampled, but not 100% tested.

4. See Figure 11, “AC Input/Output Reference Waveform” on page 49 for timing measurements and maximum allowable input

slew rate.

5. See

Figure 9, “Write Operations Waveform” on page 47.